Изобретение относится к вычислительной технике и может использоваться в устройствах, предназначенных для автоматизации экспериментов, в частности в таких случаях когда объект исследования описывается некоторой системой уравнений и решается задача определения внешних воздействий, которым подвергается объект исследования.

Известно устройство для суммирования, содержащее комбинационный п-разрядный сумматор и для обеспечения обратимости элемента НЕ, 2п сумматоров по модулю два, т.е. по два сумматора в каждом разряде, первые входы которых подключены к первой входной шине слагаемых и к выходу элемента НЕ своего разряда, выходы комбинационного п-разрядного сумматора соединены поразрядно с третьими входами полусумматоров и с входами элемента НЕ tl3«

- Недостатком этого устройства является низкая устойчивость работы, обусловленная в первую очередь циклическим переносом из старшего разряда в младв ий, а также наличием замкнутых контуров в каждом разряде, организованных из последовательно

соединенных инверторов, необратимого сумматора и сумматора по модулю, кроме того,сложность функционирования из-за необходимости задания...нформации в истинных значениях и ее отрицаниях, а также представления положительных чисел в прямом коде, а отрицательных - в обратном.

Наиболее близким к изобретению

10 является устройство, содержащее в

каждом разряде ( i 1п)

одноразрядный двоичный сумматор, четыре сумматора по модулю два, три элемента задержки и два элемента ,

15

Недостатком сумматора является относительно высокая сложность, обуслЬвленная применением в каждом разряде одноразрядного сумматора, а также относительно невысокое быстродействие,

20 определяемое последовательной организацией переноса между разрядами.

Целью изобретения является упрощение обратимого п-разрядного сумматора и увеличение его быстродействия. .

25

Поставленная цель достигается тем,.что обратимей п-разрядный, сумматор, содержащий в каждом i-м разряде (i 1, ..., п) четыре сумматора по модулю два, три элемента задержки и два элемента И, причем пер-1

30

вые входы первого и второго сумматоров по модулю два соединены с выходами, первого и второго элементов задержки и шинами данного разряда первого и второго слагаемых обратимого п-разрядного сумматора соответственно, входы первого и второго элементов задержки -соединены с выходами третьего и четвертого сумматоров по модулю два и первыми входами первого и второго элементов И, вторые входы первого и второго элементов И подключены к выходам второго и первого сумматоров по модулю два и к первым входам четвертого и третьего сумматоров по модулю два, вторые входы третьего и четвертого сумматоров по модулю два соединены с шиной суммы данного разряда обратимого п-разрядного .сумматора и выходом третьегоэлемента задержки , каждый I-и разряд обратимого п-разрядного сумматора содержит пятый сумматор по модулю два, третий и четвертый элементы И и элемент ИЛИ, причем первые входы третьего и четвертого элементови и вторые входы первого и второго сумматоров по модулю два соединены с выходом элемента ИЛИ (1-1)-го разряда обратимого п-разряд ного, сумматора, вторые входы третьего и четвертого элементов И подключены соответственно к шинам данного разряда первого и второго слагаемых обратимого п-разрядного сумматора, вход третьего элемента задержки соединен; с выходом пятого сумматора по модулю два, входы которо.го подключены к выходу первого сумматора по модулю два и ыине данного разряда второго слагаемого обратимого п-разрядного сумматора соответственно, выходы первого, второго, третьего и четвертого элементов И соединены с входами элемента ИЛИ.

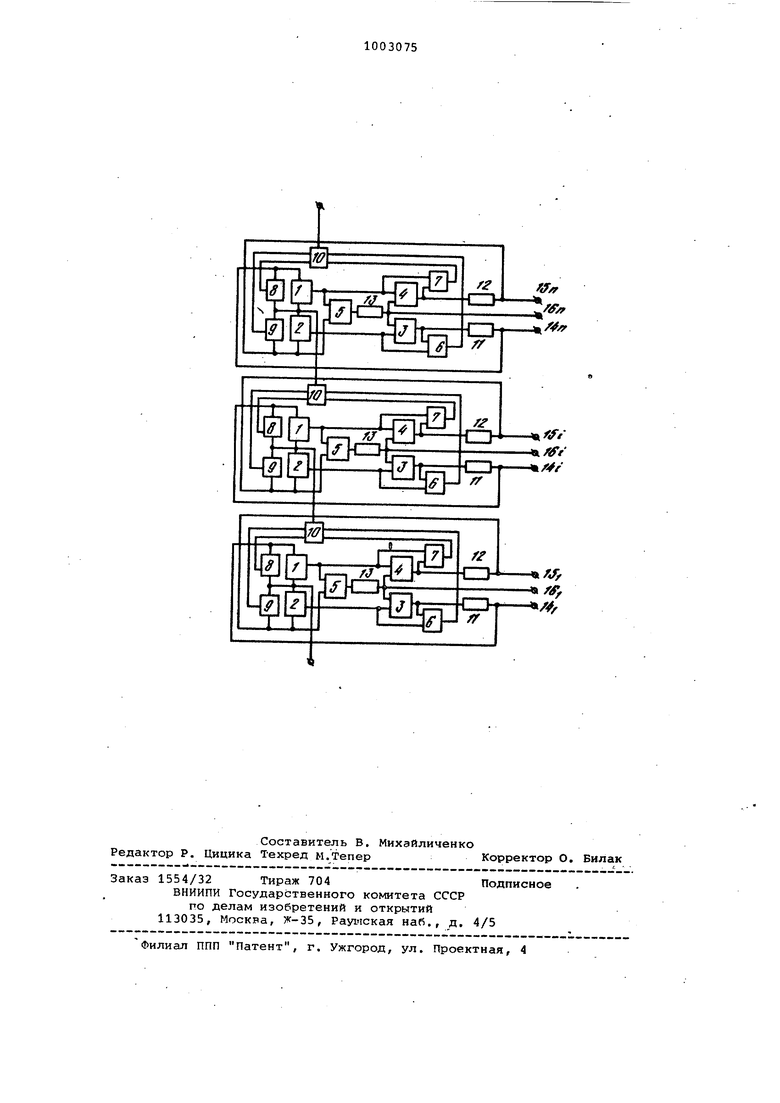

На чертеже представлена схема обратимого п-разрядного сумматора для случая, когда информация ставлена п 3 двоичными разрядами.

ОбратимЕлй п-разрядный сумматор в каждом i-м разряде содержит пять сумматоров 1-5 по модулю два, четыре элемента И 6-9, элемент ИЛИ 10, три элемента задержки 11-13, шину первого слагаемого 14; , шину второго слагаемого 15 и .шину сумм 16 , входы сумматоров 1 и 2 по модулю два каждого i-ro разряда обратимого.п-разрядного сумматора подключены к выходам элементов задержки 11 и 12 и входным шинам первого 14 и второго 15 слагаемых,.соответственно, выходы сумматоров 3 и по модулю два подключены к входам первого и второго эле задержки 11 и 12 и к входам первого и второго элементов б и 7, вторые входы которых подключены к выходам сумматоров 2 и ,1 по модулю два и первым входам сумматоров 3 и 41

по модулю-j два, вторые входы которых соединены с шиной cyMNbi 16 и с выходом элемента задержки 13, Выход элемента ИЛИ 10 каждого t-го разряда обратимого п-разрядногр сумматора подключен к входам сумматоров 1 и 2 по модулю два и элементов И 8 и 9 (1+1)-го разряда (i « п). Входы элементов И 8 и 9. 1-го разряда обратимого п-разрядного сумматора подключены соответственно к шинам первого J.4 и второго 15 слагаемых, а выход сумматора 5 по модулю два подключен к входу элемента задержки 13. Первый вход сумматора 5 по модулю два I-го разряда обратимого п-разрядного сумматора соединен с выходом сумматора 1 по модулю два, второй вход. - с шиной второго слагаемого 14, а входы элемента ИЛИ 10 подключены, к выходам Э7;ементов И 6-9.

РаЬоту обратимого п-разрядного сумматора поясним на npHjf epe определения суммы а+Ь,первой S-b и второй 1 S-a разности чисел S, а, Ь, представленных в разрядной форме:

Г... is i la... i;

t&... При этом в обратном п-разрядном сум;маторе сумма реализуется на сумматорах 1 и 5 по модулю два, а эффект обратимости организуется с помощью применения в каждом разряде сумматоров 1-4 по модулю два, элементов 4-9, элемента ИЛИ 10 и трех элементов задержки 11-13. При подаче значений .Ь и Ь на шину первого слагаемого и шину второго слагаемого 15| обратимого п-разрядного сумматора и после окончания переходного процесса на выходе сумматора 5. по модулю два обрадуется значение s искомого вектора S, при этом значение каждого

,I-го разряда S которого подается через элемент задержки 13 на входы сумматора 3 и 4 по модулю два, на выходах которых образуются значения соответству ощих разрядов i,b векторов а и 6.

При подаче вычитаемого S на шину сумм 16- и вычитателя I - на шину первого слагаемого 14|, после окончания переходного процесса на выходе сумматора 4 по модулю два.каждого 1-го разряда обратимого п-разрядного сумматора образуется значение Ь вектора. S, которое через элемент задержки 13 подается на вторые входы сумматоров 2 и 5 по модулю два. При этом на выходе сумматоров 5 и 3 по модулю два об.разуются соответствен-, . но значения S и I векторов S и а. При подаче вычитаемого- S и вычитателя Ь на шину сумм 16|й соответот. венно шину второго слагаемого 15, , после окончания переходного процесса на выходе сумматора 3 по модулю два каждого i-ro разряда обратимого п-разрядн го сумматора образуется значение а вектора If, которое элемент задержки 11 подается на вход сумматора 1 по модулю два 2. При . этом на выходах сумматоров 5 и 4 по модулю два обр.азуются со9тветственн значения S и Ь векторов S и Ь. Эффект обратимости в обратимом п-разрядном сумматоре достигается путем моделирования в каждом разряде устройства системы логических уравнений -f ii« I - ,©b.; II j j a 5,,© .« So..- bit f © - знак, обозначающий операцию сложения по модулю два, р - значение переноса из (i-l)в i-й разряд. Использование в кгикдом i-ом разря де обратимого п-разрядного сумматора новых элементов - двух элементов И, сумматора по модулю два и элемента ИЛИ, а также введение новых связей между ними выгодно отличает данный сумматор от известного устройства, так как уменьшается количество необходимого электронного оборудования. Например, для построения 1-го разряда известного устройства необходимо четыре сумматора по модулю два и оди полный однородный двоичный сумматор что эквивалентно двум сумматорам сло жения по модулю два (в. соо.тветствии с выражением 5 J @ 1 © iJ) - всего шесть сумматоров по модулю два. Для построения i-ro разряда данного обратимого п-разрядного сумматора необходи.мо пять сумматоров по модулю два. Для организации переноса в известном необходимо один элемент ИЛИ пять элементов И (так как в необрати мом суммат.оре .енрс обр.азуется по выражению ) и три шины переноса. В предлагаемом обратимом сумматоре для организации переноса необходимо одни элемент ИЛИ, четыре элемента И и одна шина переноса. Таким образом, для построения i-r р аэряда предлагаемого обратимого сум )матора необходимо на один сумматор по модулю два, один элемент И и две шины переноса меньше. Кроме того, увеличивается быстродействие сумматора благодаря организадии сквозного переноса с помощью разряда обратимого двух элементов И и элемента ИЛИ каждого i-го разряда обратимого п-раэрядного сумматора. Формула изобретения Обратимый п-разрядный сумматор, содержащий в каждом i-м разряде (i 1, ..., п) четыре сумматора по модулю два, три элемента задержки и два элемента И, причем первые входы первого и второго сумматоров по модулю два соединены с выходами первого и второго элементов задержки и шинами данного разряда первого и второго слагаемых обратимого п-разрядного сумматора соответственно, входа первого и второго элементов задержки соединены с выходами третьего и четвертого сумматоров по модулю два и первыми входами первого и. второго элементов И соответственно, вторые входы первого и второго элементов И подключены к выходам второго и первого сумматоров по модулю , два и к первым входам четвертого и третьего сумматоров по модулю два соответственно, вторые входы треть его и четвертого сумматоров по модулю два соединены с шиной суммы данного разряда обратимого п-разряд- ного сумматора и выходом третьего элемента задержки, о т л и ч а ющ и и с я тем, что, с целью упрощения и повышения быстродействия сумматора , каждый i-и разряд обратимого п-разрядного сумматора содержит пятый сумматор по модулю два, третий и четвертый элементы И и элемент ИЛИ, причем первые входы третьего и четвертого элементов И и вторые входы первого и второго сумматоров по модулю два соединены с выходом элемен-, та ИЛИ i-1-го разряда обратимого п-разрядного сумматора, вторые входы третьего и четвертого элементов И подключены соответственно к шинс1М данного разряда первого и второго cлaгae влx обратимого п-раэряднбго сумматора, вход третьего элемента задержки соединен с выходом пятого сумматора по модулю два, входы которого подключены к выходу первого сумматора по модулю два и шине данного разряда второго слагаемого обратимого п-разрядного сумматора соответственно, выходы первого, второго, третьего и четвертого элементов И .соединены с входами элемента или, . . Источники информации, . принятые во внимание при экспертизе 1. Авторское свидетельство СССР 514293, клч G 06 F 7/50, 1977. 2. Авторское свидетельство СССР по заявке 2792635/28-24, кл. G 06 F 7/50, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Обратимый п-разрядный сумматор | 1979 |

|

SU824204A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Накапливающий сумматор | 1985 |

|

SU1319023A1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

| Арифметическое устройство | 1979 |

|

SU860065A1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

Авторы

Даты

1983-03-07—Публикация

1980-02-22—Подача