(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Устройство для умножения | 1987 |

|

SU1444755A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании цифровых вычислительных устройств. Известно устройство для умножения и извлечения квадратного корня, содержащее регистры операндов и резуль тата, схему анализа кодов, сумматоры генератор тактов 1 . Наиболее близким к предлагаемому является арифметическое устройство, содержащее регистры множимого, множителя, группу элементов И, ИЛИ,И-НЕ п групп сумматоров, группы элементов 2И-ИЛИ 2. Недостатком известных устройств является невысокое быстродействие при извлечении квадратного корня. .Цель изобретения - повышение быст родействия устройства при выполнении операции вычисления квадратного корн Поставленная цель достигается тем что в арифметическом устройстве, содержащем регистры множимого и множителя, группу элементов И, группу эле кюнтов ИЛИ, элементы И, ИЛИ, И-НЕ, п групп сумматоров, причем выходы сумматоров п-ой (где п - разрядность результата) группы соединены со входами регистра произведения, инверсные выходы разрядов которого (со второго по п-ый) соединены с первыми входами соответствующих элементов 2И-ИЛИ первс группы, вторвае входы которых соединены с выходами регистра мнеткимого, третьи входы - с входом разрешения записи произведения, а выходы подключены к первым входам сумматоров п-ой группы, вторые входы которых соединены с выходами сумлаторов (п-1)ой группы и разрядными входами регистра , вторую группу элементов 2И-ИЛИ, выход f-ro (где 1, 2..., п) разряда регистра множителя соединен с первым входом i-ro элемента И группы, выход которого подключен ко входу (21-1)-го разряда регистра кшожимого, выход i-ro элемента ИЛИ группы подключен к первому входу (2«-1)-го элемента 2И-ИЛИ второй группы, а первый вход i-ro элемента ИЛИ группа соединен с выходом i-ro разряда регистра множителя, первый вход 21-го элемента 2И-ИЛИ второй группы соединен с прямым выходом (2i+1)-ro разряда регистра cyMNti,вторые входы элементов 2И-ИЛИ второй группы подсоединены к выходам сумматоров (п-2)-ой группы управляющие входы элементов 2И-ИЛИ второй группы

подключены к входу разрешения записи произведения, а выходы - ко вторым входам .сумматоров (п-1)-ой группы, иверсный выход переноса п-ой группы сумматоров соединен с первым входом первого элемента И, второй вход которого соединен со входом разрешения записи в регистр, а выход подключен к управляющим входам элементов И групы и входам синхронизации регистра суммы, инверсный выход первого разряда которого соединен с первым входом элемента И-НЕ, второй вход которого подключен к прямому выходу первого разряда регистра произведения, а выход - к первому входу первого элемента И-ИЛИ первой группы, второй и третий входы которого подключены соответственно к выходу первого разряда регистра множимого и входу разрешения записи произведения, выход первого разряда регистра множителя соединен с первым входом второго эле мента И, выход которого соединен с четвертым входом элемента2И-ИЛИ первой группы, а выход второго разряда регистра множителя соединен с первым входом элемента ИЛИ, выход которого соединен с соответствующим входом матрицы умножения, вторые входы второго, элемента И и элемента ИЛИ соединены с входом разрешения записи произведения, второй вход i-ro элемента ИЛИ группы соединен с прямым выходом 2 i-ro разряда ре- гистра cyMJvuJ.

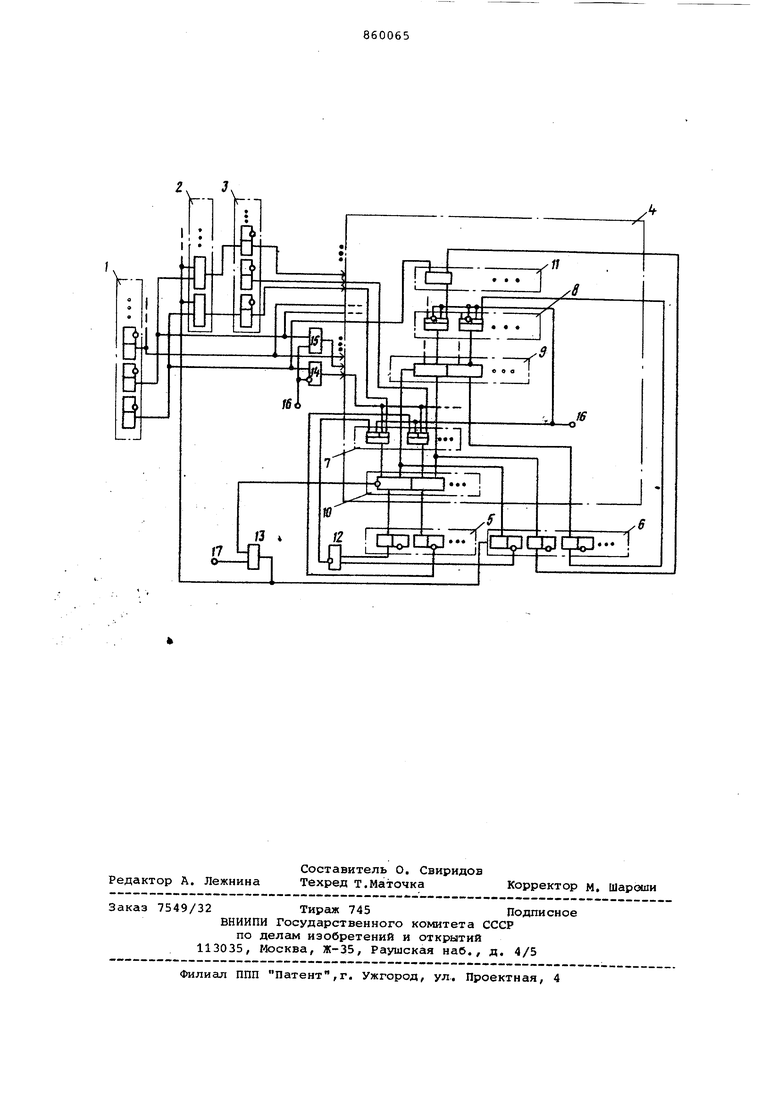

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит регистр 1 множителя, группу элементов И 2, регист 3 множимого, матрицу 4 умножения н сумматорах, регистр 5 произведения, регистр б суммы, первую группу элементов И-ИЛИ 7, вторую группу элементов И-ИЛИ 8 {п-1)-ую строку сумматоров 9 матрицы, последнюю строку сумматоров 10 матрицы, группу элементов ИЛИ 11, элемент И-НЕ 12, первый элемент И 13, второй элемент И 14, элемент ИЛИ 15, первую шину 16 управления, вторую шину 17 управления. Элементы 7-11 объединены в матрицу 4 умножения.

Устройство работает следующим образом.

При умножении и квадратировании в регистры 1 и 3 заносятся сомножители, на шины 16 и 17 управления подается О, результат произведения с выгсода матрицы 4 записывается в регистр 5, вычисление квадратного корня выполняется методом обратного поиска за п тактов (где п - разрядность результата) т.е. производится последовательный подбор цифр результата, квадрат которого сравнивается с подкоренным выражением. Шлчисление квадрата результата в i-ом приближении (шаге) выполняется с использованием значения результата а - (i-1)го шага и приращения Ь., задаваемого в i-ом шаге.

% (%+, al.+ 2a,., b. Ь f В исходном состоянии регистры 1, 3 и 6 очищены, на шину 16 подан разрешаюций сигнал, в регистре 5 записано подкоренное выражение. В первом такте в регистре 1 производится перQ вый сдвиг и в старший разряд заносится 1, которая является пробным приращением (Ь ) для первого шага вычислений. За счет того, что выходы регистра 1 подключены через группу элементов ИЛИ 11 и группу элементов

5 И-ИЛИ 8 к входам ряда сумматоров 9 со сдвигом (i-ый разряд регистра 1 к ()-му разряду ряда сумматоров 9), то на вторые входы ряда, сумматоров 9 подается число равное Ь Через

0 эти же группы элементов на вторые

входы ряда сумматоров 9 с регистра 6, в котором хранится квадрат результата (i-l)-ro шага, поступает число а о 0. На первые входы ряда

5 сумматоров 9 через открытые ключи, управляемые сигналом шины 16 через элемент ИЛИ 15, со входов матрицы поступает результат произведения Ь 2а 0, который формируется на регистре 3. На ряде сумматоров 10 производится сравнение квадрата результата первого шага а + 2ао Ь + ь Ь с подкоренным выражением А, хранящимся в регистре 5. В конце первого такта при наличии переноса 1 ряда сумматоров 10

{при SA) значение a с выходов ряда сумматоров 9 по управляющему сигналу шины 17 записывается в регистр б, а в первый {в ()-ый, но 0 ) разряд регистра 3 переписывается 1 с первого разряда регистра 1. Если с, (при ), то содержимое регистров 3 и б не изменится.

5 Второй и последующие такты начинаются с импульса, по которому содержимое регистров 1 и 3 сдвигается на разряд вправо. Описанный процесс повторяется с учетом того, что при вычисл лении квадрата результата i-ом ( приближений (шаге) на ряд сумматоров 9 кроме слагаемого Ь поступают слагаемые аД и , которые равны или больше нуля в зависимости от результата а, предыдущего шага. Ввиду

5 того, что у слагаемых а и Ь в i-oM шаге не перекрывается диапазон их возможных численных значений, то они поступают на одни и те же входы ряда сумматоров 9 через группу элементов ИЛИ 11. Слагаемое формируется на регистре 3 после установки 1 (или О) в )-ом разряде в конце (i- 1)-го такта и последующего сдвига содержимого регистра 3 в начале I-го такта. Модуль разности старшего разряда регистра 5 и старшего разряда регист ра б формируется на элементе И-НЕ 12 что не требует установки дополнитель ного разряда сумматора в ряде сумматоров 9 матрицы 4. Таким образом, после п тактов п-разр9дный результат вычисления ква ратного корня, сдвинутый на п разря(дов вправо, находится в регистре 3. Как видно из описания, сущность улучшения по сравнению с известным устройством заключается в повышении быстродействия устройства при выполнении операции вычисления квадратног корня за счет уменьшения.периода каж дого из п вычислительных тактов. Вре мя выполнения операции вычисления квадратного корня известного устройства для п разрядов результата определяется из соотношения ty, « п (2п TC) l:n(2vi-t 2H-Cy,) ,, где задержка распространения пер носа на один разряд сумматораtf.- задержка распространения сиг нала суммы на один разряд сумматора. Время выполнения операции вычисле ния квадратного корня предлагаемого устройства для п разрядов результата t ;t п(2п-Ги) , . Ускорение, получаемое при вычислении квадратного корня на нём, k . Таким образом, расчеты показывают что быстродействие предлагаемого устройства по сравнению с известным вдвое больше. Формула изобретения Арифметическое устройство, содержащее регистры множимого и множителя группу элементов И, группу элементов ИЛИ, элементы И, ИЛИ, И-НЕ, п групп сумматоров, причем выходы сумматоров п-ой (где п - разрядность результата группы соединены со входа ми регистра произведения г инверсные Шзхходн разрядов которого 1со второго по п-ый) соединены с первыми входалш соответствующих элементов И-ИЛИ первой группы,- вторые входы которых соединены с выходами регистра множимого, третьи входы - с входом, разрешения записи произведения, а выходы подключены к первым входам сумматоров,п-ой группы, вторые входы которых соединены с выходами сумматоров (п-1)-ой группы и разрядными ВХОДс1МИ реГЙСТра суммы, вторую группу элементов 2И-ИЛИ, отличающееся тем, что, с целью повьшения быстродействия, в устройстве выход i-ro (где ,2...,n) разряда регистра множителя соединен с первым входом i-ro элемента И группы, выход которого подключен ко входу (2i-1)-ro разряда регистра множимого, выход i-ro элемента ИЛИ группы подключен к первому входу (2i-l) элемента 2И-ИЛИ второй группы, а первый вход i-ro элемента ИЛИ группы соединен с выходом i-ro разряда регистра множителя, первый вход 2 I-го элемента 2И-ИЛИ второй группы соединен с прЯ1у1ым выходом (2i+l)-ro разряда регистра суммы, вторые входы элементов 2И-ИЛИ второй группы подсоединены к выходам сумматоров (п-2)-ой группы, управляющие входы элементов 2И-ИЛИ второй группы подключены к входу разрешения записи произведения, а выходы - ко вторым входам сумматоров (п-1)-ой группы, инверсный выход переноса п-ой группы сумматоров соединен с первым входом первого элемента И, второй вход которого соединен со входом разрешении записи в регистр, а выход подключен к управляющим входам элементов И группы к входам синхронизации регистра , инверсный выход первого разряда которого соединен с первым входом элемента И-НБ, второй вход которого подключен к прямому выходу первого разряда регистра произведения, а выход - к первому входу первого элемента И-ИЛИ первой группы, второй и третий входы которого подключены соответственно к выходу первого разряда регистра множимого и входу разрешения записи произведения, выходпервого разряда регистра множителя соединен с первым входом второго элемента И, выход которого соединен с четвертым входом элемента 2И-ИЛИ первой группы, а выход второго разряда регистра множителя соединен с первым входом элемента ИЛИ, выход которого соединен с соответствующим входом матрицы умножения, вторые входы второго элемента И и элемента ИЛИ соединены с входом разрешения записи произведения, второй вход 1-го элемента ИЛИ группы соединен с прямым выходом 2i-ro разряда регистра суммы. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 657434, кл. G 06 F 7/38, 1977. 2. Авторское сш1детельство СССР 542993, кл. G Об F 7/38, 1977.

Авторы

Даты

1981-08-30—Публикация

1979-11-30—Подача