сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Конвейерный сумматор | 1989 |

|

SU1714588A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Накапливающий сумматор | 1985 |

|

SU1319023A1 |

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для параллельного суммирования двоичных чисел в фибоначчи- евой системе счисления. Целью иозбрете- ния является расширение области применения за счет обеспечения работы в вычислительных системах переменной разрядности. Накапливающий сумматор имеет разряды (одноразрядные сумматоры), каждый из которых содержит восемь элементов ИЛИ, два элемента И, элемент сложения по модулю два, триггер со счетным входом и элемент задержки. 5 табл., 2 ил.

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах для параллельного суммирования двоичных чисел в фибоначчи- евой системе счисления.

Цель изобретения - расширение области применения за счет обеспечения работы в вычислительных системах переменной разрядности.

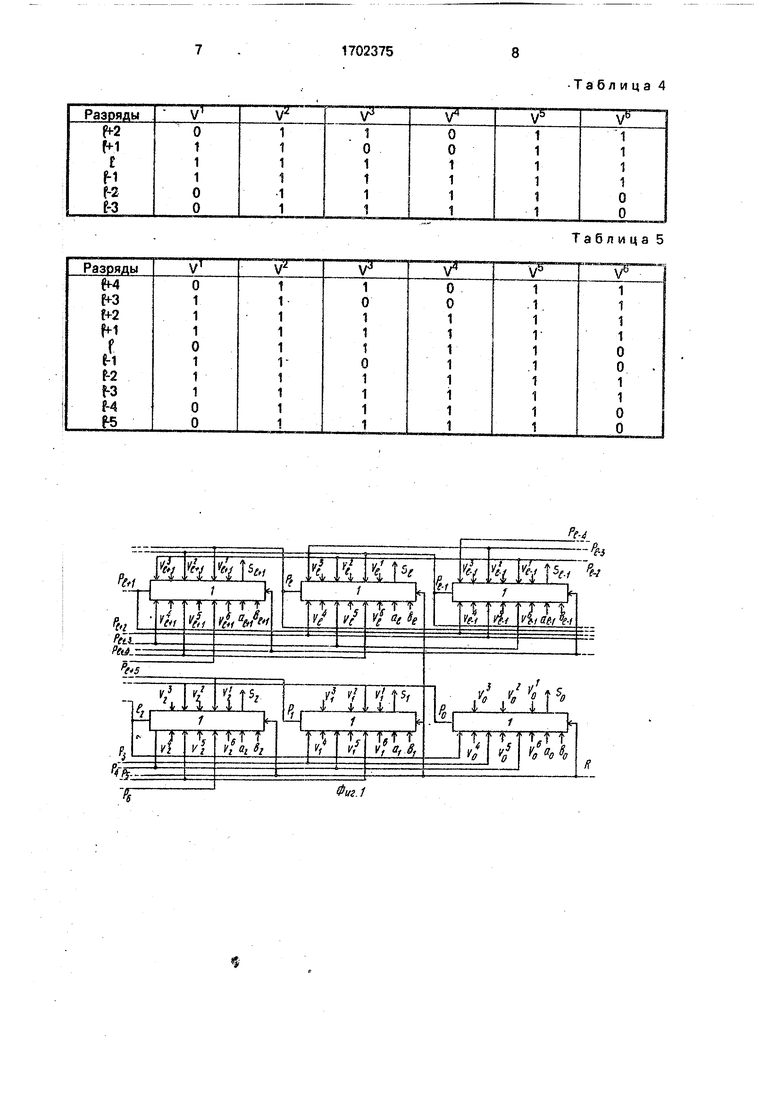

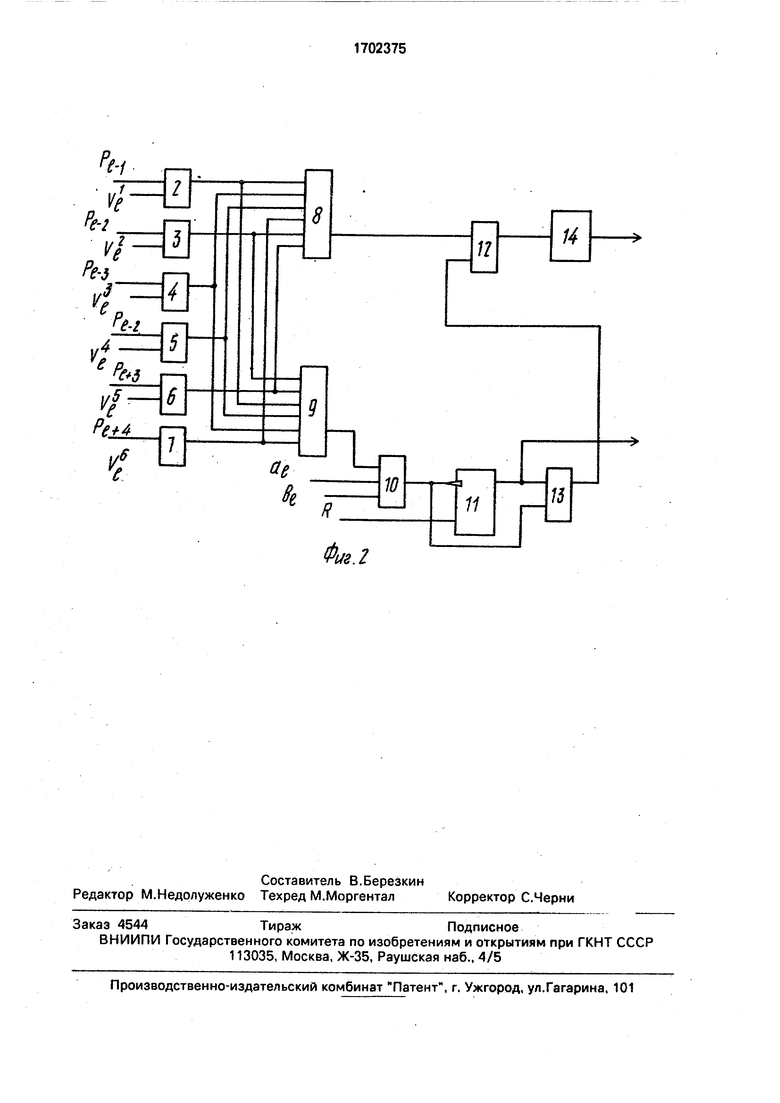

На фиг.1 приведена блок-схема накапливающего сумматора; на фиг.2 - схема одного разряда сумматора.

Накапливающий сумматор содержит (фиг,1) разряды 1 (одноразрядные сумматоры). Каждый разряд (фиг.2) сумматора содержит элементы ИЛИ 2-7, элемент И 8, элемент сложения по модулю два 9, элемент ИЛИ 10, триггер 11 со счетным входом, элемент ИЛИ 12, элемент И 13, элемент задержки 14.

При этом к первому и второму входам первого элемента ИЛИ 10 подключены

входные шины первого ai и второго 3i слагаемых, а к третьему входу первого элемента ИЛИ 10 подключен выходу элемента 9 сложения по модулю два, выход первого элемента ИЛИ 10 - к единичному входу триггера 11, установочный вход которого подключен к шине сброса R, а выход триггера 11 подключен к первому входу первого элемента И 13 и к шине результата сложения Se. К второму входу первого элемента И 13 подключен выход первого элемента ИЛИ 10, выход первого элемента И 13 подключен к первому входу второго элемента ИЛИ 12, выход которого подключен к элементу 14 задержки, выход подключенный к шине переноса Ре блока.

Первые входы третьего, четвертого, пятого, шестого, седьмого и восьмого элементов ИЛИ 2-7 соответственно подключены к шинам переноса (, (f-2)-ro, (№)-го, (fr-2)- го, (f+3}-ro и (Ь-4)-го блоков.

VI

О

го со VI ел

Вторые входы этих же элементов ИЛИ подключены к шинам запрета переносов rex же блоков.

Выходы третьего, четвертого, пятого, шестого седьмого и восьмого элементов ИЛИ 2-7 подключены к первым, вторым, третьим, четвертым, пятым и шестым входам второго элемента И 8 и элемента 9 сложения по модулю два соответственно.

Выход второго элемента И 8 подключен к второму входу второго элемента ИЛИ 12.

Рассмотрим работу устройства для пяти случаев.

Для первого случая, когда используются все разряды, на входы запретов V 1-го разряда сумматора подаются сигналы лог.О и лог.1 согласно табл.1.

На неуказанные входы запретов V 2-го, 1-го и 0-го разрядов сумматора V 1; Лх V2o и V1o всегда подаются сигнал лог. 1.

Перед началом суммирования подается сигнал R Сброс, который устанавливает триггер 11 со счетным входом в нулевое состояние.

Предположим, , вН), и Рр+ .

Исходные операнды ai и BI подаются последовательно с интервалом tn Гт, где ту - время срабатываний триггера 11. Тогда, после подачи сигнала триггер 11 устанавливается в единичное состояние по заднему фронту сигнала.

На единичном выходе триггера 11 образуется лог.1 и на выходе S возникаег лог.1 - промежуточная сумма. После подачи сигнала et О состояние триггера 11 не изме- нится. Сигнал Pft-2 1 появится на входе 1-го разряда, как результат суммирования в (1+ + 2)-м разряде, с задержкой тп.з, обеспечивающей завершения переходных процессов в разрядах накапливающего сумматора. Так как на входе VV-0 согласно табл,1 и на входе Pf+2-1, то на выходе элемента И 4 образуется лог.1, которая попадает на четвертые входы И 8 и элемента сложения по модулю два.

Так как сигнал , то на выходе элемента И 2 образуется сигнал лог.О, на входах V2e, V3e, V5t, V6e - лог.1, поэтому на выходах элементов И 3, И 5, И б и И 7 лог, 1, которая попадает на вторые, третьи, пятые, шестые входы элемента И 8 и элемент 9 сложения по модулю два на первых входах элемента И 8 и элемента 9 сложения по модулю два, лог.О, поэтому на выходе элемента И 8 лог.О, а на выходе элемента 9 сложения по модулю два лог.1, которая через элемент ИЛИ 10 попадает на счетный вход триггера 11. Так как триггер 11 находится в единичном состоянии и на втором

входе элемента И 13 лог.1, на выходе этого элемента И образуется лог,1, которая, проходя через элемент ИЛИ 12, попадает на вход элемента линии задержки 14, на выхо- 5 де которого также возникает лог.1, задержанная на врэмя гл.з.

По заднему фронту сигнала Р|+2 триггер 11 перейдет в нулевое состояние и на выходе элемента И 13 образуется лог.О, что при- 0 ведет к окончанию импульса PI на выходе. После окончания образования промежуточных переносов, процесс суммирования считается завершенным.

Рассмотрим второй случай, когда от- 5 ключается -й разряд на входы подаются сигналы согласно табл.2.

На V входы на указанных в табл.2 разрядов подаются сигналы такие же, как и на $+2)-й разряд.

0 Суммирование происходит следующим образом.

Подается операндА Ап,...,Аги, Ар, Af-iAiAo

при этом АЈ- не участвует в суммировании и состояние Se не рассматривается. Затем 5 поступает операнд В Bn,...BffiBjB{-i,...,BiBo. Если образовался перенос Рм он поступает на (Ј-И)-й и (f3}-u разряды. Если возник перенос Pf, то он попадает не на С-й разряд, а на (М)-й разряд.

0 Рассмотрим третий случай, когда отключаются { +2}-й, f-й и (Ь2}-й разряды. Сигналы V подаются согласно табл.3.

На V входы остальных разрядов подаются сигналы такие же, как и на (f+4)-tf разряд, 5 Поступает операнд А An,...,At+4, Afr-з, Afv2, Afn, A, Af-i, , AH, ..- AiAo. затем поступает операнд В Bn...., Bft-a, , , , Bg Bfi, , Вьз, ВмBtBo.

Разряды (Н-2)-й, t-й и (С-2}-й в работе не 0 участвуют и состояние S(fr-2), S и Sp-2 не учитываются в результате суммирования.

Если возник сигнал РН, то он попадает не на (С+2}-й и (Р-1)-й, а на разряды (|+3)-й и (.

5 Рассмотрим четвертый случай, когда два соседних разряда отключаются ({-и и (Й}-й). Сигналы V подаются согласно табл.4.

На V входы остальных разрядов поступают сигналы такие же, как и для (Р+2)-го 0 разряда.

На вход сумматора поступает операнд

А AnАИ, Аен, Af, Ац, Af-2, Af3AiAo.

Затем поступает операнд

В- ВпВ&а, Bfri, Bf, BM, Bf-2, В зBiBo.

5 Состояние Af, Af-i, BI и Вм не учитываются и в суммировании не участвует, результат Se и Se-i не учитывается. Если возник перенос PЈt/ он попадает на (Й-2)-й и на (Ј-3)-й разряды. Перенос Pfn поступает на (И)-й и $-4)-й разряды.

Рассмотрим пятый случай, когда (+2)-й, (М)-й ( и (гЗ)-й разряды. Сигналы V подаются согласно табл.5.

На V входы остальных разрядов сигналы поступают та кие же, как и для (f+4}-ro разряда. При поступлении операндов А и В разряды , . А(2, Af3, Bff2, Bp-1 Bf-2 И Bj-3 в работе не участвуют и их значения не рассматривается, Sf+2, Sfn, S(-2, Spo не учи- тываются. При образовании PI он поступает на (+3)-й и (М}-й разряды. Ppi поступает на f-й к (Ј-5)-й разряды.

Pi-4 поступают на (Ј-1}-й и (-6}-й, Рц-з поступает на (+4)-й и (И)-й разря- ДЫ.

Формула изобретения Накапливающий сумматор, каждый из п разрядов которого содержит элемент сложения по модулю два, триггер, элемент за- держки, первый и второй элементы ИЛИ, первый и второй элементы И, при этом к первому и второму входам первого элемента ИЛИ подключены шины слагаемых данного разряда сумматора, а к третьему входу подключен выход элемента сложения по модулю два, выход первого элемента ИЛИ подключен к счетному входу триггера, установочный вход которого подключен к

шине сброса сумматора, выход триггера подключен к первому входу первого элемента И и к шине суммы данного разряда сумматора, к второму входу первого элемента И подключен выход первого элемента ИЛИ, выход первого элемента И подключен к первому входу второго элемента ИЛИ, выход которого подключен к входу элемента задержки, выход которого подключен к шине переноса из данного разряда сумматора, второй вход второго элемента ИЛИ подключен к выходу второго элемента И, о т л и ч а- ю щ и и с я тем, что, с целью расширения области применения за счет обеспечения работы в вычислительных системах переменной разрядности, в каждый разряд сумматора введены элементы ИЛИ с третьего по восьмой, причем первые входы третьего, четвертого, пятого, шестого, седьмого и восьмого элементов ИЛИ подключены соответственно с шинам переноса из (f-1)-ro ( 2)-го, (f-3)-ro, ()-го, (И)-го и (Р+4)-го разрядов сумматора, а вторые входы подключены соответственно к соответствующим шинам запретов переносов сумматора, выходы элементов ИЛИ с третьего по восьмой подключены к входам второго элемента И, элемента сложения по модулю два.

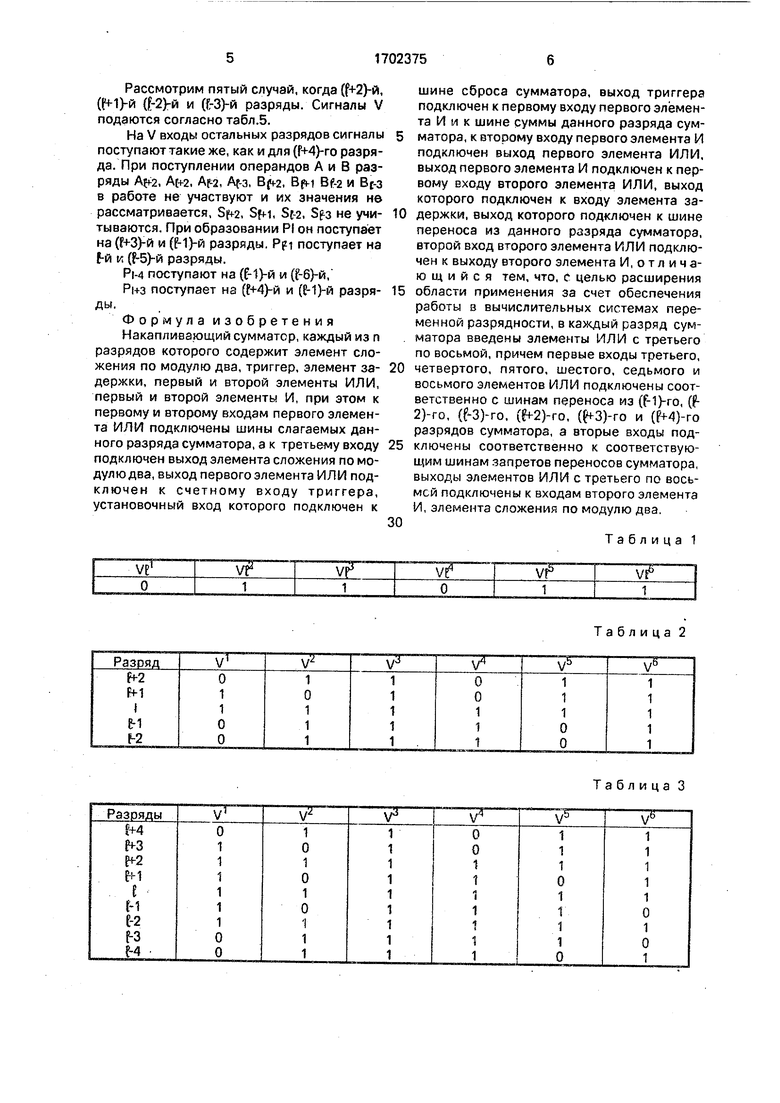

Таблица 1

Таблица 2

Таблица 3

Таблица 4

Таблица 5

Фиг. 2

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Накапливающий сумматор | 1976 |

|

SU577528A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-30—Публикация

1989-09-12—Подача