Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки сигналов, измерительных устройствах и устройствах сортировки.

Цель изобретения - повышение быстродействия.

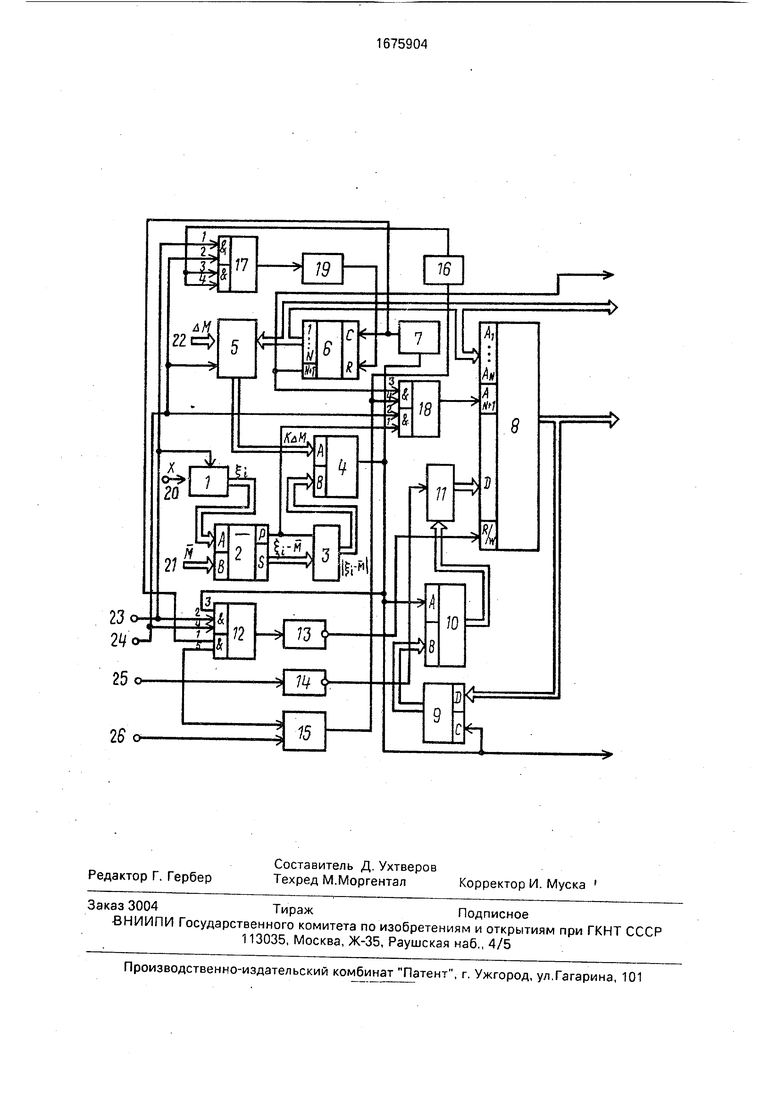

На чертеже представлена функциональная схема устройства.

Анализатор содержит аналого-цифровой преобразователь АЦП 1, блок 2 вычитания, блок 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 4 сравнения, блок 5 умножения, счетчик 6, генератор 7 тактовых импульсов, блок 8 памяти, информационный выход анализатора 9, сумматор 10, блок 11 элементов И, первый элемент 2И-ИЛИ 12, первый 13 и второй 14 элементы НЕ, элемент ИЛИ 15, формирователь 16 импульсов, второй 17 и третий 18 элементы 2И-ИЛИ, элемент 19

задержки, информационный вход 20 устройства, вход 21 установки начального значения математического ожидания анализатора, вход 22 задания ширины дифференциального диапазона анализатора, тактовый вход 23 устройства, вход 24 начальной установки математического ожидания анализатора, вход 25 сброса анализатора, вход 26 запуска анализатора, выход блока 8 памяти соединен с первым входом сумматора 10, выход счетчика 6 соединен с адресным входом блока 8 памяти, информационный вход 20 анализатора является входом АЦП 1, выход которого соединен с входом уменьшаемого блока 2 вычитания, вход вычитаемого которого соединен с входом 21 установки начального значения математического ожидания анализатора, информационный выход блока вычитания соединен с первой группой входов

о, ел

блока 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход переноса блока вычитания соединен с второй группой входов блока 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом блока 4 сравнения, второй вход которого соединен с выходом блока 5 умножения, вход множимого которого соединен с входом 22 задания ширины дифференциального диапазона анализатора, вход множителя блока 5 умножения соединен с выходом счетчика 6, суммирующий вход счетчика 6 соединен с выходом генератора 7 счетных импульсов и с первым входом первой группы входов первого элемента 2И-ИЛИ 12, второй вход первой группы входов которого соединен с входом первого элемента НЕ 14, первым входом элемента ИЛИ 15 и с входом 25 сброса анализатора, второй вход элемента ИЛИ 15 является входом 26 запуска анализатора, выход первого элемента НЕ 14 соединен с управляющим входом блока 11 элементов И, информационные входы которого соединены с выходом сумматора 10, выход Больше блока 4 сравнения соединен с входом запуска генератора счетных импульсов,с первым входом второй группы входов первого элемента 2 И-ИЛИ 12, второй вход второй группы входов которого является тактовым входом 23 анализатора и соединен с входом синхронизации АЦП 1 и первым входом первой группы входов второго элемента 2 И-ИЛИ 17, второй вход первой группы входов которого соединен с третьим входом второй группы входов первого элемента 2 И-ИЛИ 12, с тактовым входом блока 5 умножения, с входом 24 начальной установки математического ожидания анализатора и с первым входом первой группы входов третьего элемента 2 И-ИЛИ 18, второй вход первой группы входов которого соединен с выходом переноса блока 2 вычитания, выход формирователя 16 импульсов соединен с первым и вторым входами второй группы входов второго элемента 2 И-ИЛИ 17, выход которого через элемент 19 задержки соединен с входом сброса счетчика 6, выход переноса которого соединен с первым входом второй группы входов третьего элемента 2 И-ИЛИ 18, второй вход второй группы входов которого соединен с входом формирователя 16 импульсов и с выходом элемента ИЛИ 15, выход третьего элемента 2 И-ИЛИ 18 соединен со старшим разрядом адресного входа блока 8 памяти, аыход первого элемента 2И- ИЛИ 12 соединен с входом второго элемента НЕ 13, выход которого соединен с входом чтения/знака блока 8 памяти.

Анализатор работает следующим образом.

Имеются три режима работы: стирание, анализ и считывание. В режиме стирания по

входу 25 поступает сигнал Лог. 1, который подается на второй вход второй группы входов первого элемента 2 И-ИЛИ 12 и разрешает прохождение на выход элемента 2 И-ИЛИ 12 тактовых импульсов от генератора 7, поступающих на первый вход первой группы входов элемента 2 И-ИЛИ 12. С выхода элемента 2 И-ИЛИ 12 через первый элемент НЕ 13 импульсы поступают на вход чтения/запись блока 8 памяти и разрешают

запись. Одновременно импульсы с генератора 7 поступают на тактовый вход счетчика 6, N выходных разрядов которого непосредственно подключены к N адресным разрядам блока 8 памяти, а N-Ч выход подключен

к третьему входу третьего элемента 2 И- ИЛИ 18. Поскольку второй вход второй группы входов элемента 2 И-ИЛИ 18 подключен к выходу элемента ИЛИ 15, на нем в режиме стирания находится Лог. 1, а значит N+1,

на выходной разряд счетчика 6 оказывается подключенным через элемент 2 И-ИЛИ 18 к (N+IJ-му адресному разряду блока 8 памяти. В момент включения режима стирания через элемент ИЛИ 15 запускается формирователь 16 импульсов, с выхода которого импульс через второй элемент 2 И-ИЛИ 17 устанавливает счетчик 6 в нулевое состояние. Потенциал Лог. 1 с входа 25, проходя через второй элемент НЕ 14. преобразуется

в Лог. О, который блокирует элементы И 11,в связи с чем .на информационные входы блока 8 памяти поступают нули. Эти нули записываются по очереди во все ячейки памяти, адреса которых задаются последовательно счетчиком 6.

В режиме анализ по входу 24 поступает сигнал Лог, 1. Синхронно с тактовыми импульсами с входа 23 происходит преобразование аналогового сигнала в цифровой

код § в АЦП 1. Код Јi поступает на вход А блока 2 вычитания, на вход В которого поступает код математического ожидания М. В блоке 2 вычитания определяется разность |i М. Если Ј, - М 0, то на выходе

переноса блока 2 вычитания образуется Лог. О, который поступает на вторые входы блока 3 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, которые при этом пропускают код с выхода блока 2 вычитания без изменений. Если § - М 0, то на выходе переноса блока 2 вычитания формируется Лог. 1, которая переводит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3 в режим инверсии, поэтому на выходе блока 3 формируется модуль разности

|Јi - Ml 0, который поступает на вход В блока 4 сравнения. Первый тактовый импульс с входа 23 проходит через второй элемент 2 И-ИЛИ 17, поскольку последний открыт Лог. 1 с входа 24, и сбрасывает счетчик 6 в нуль. Нулевой код счетчика 6 поступает на вход блока 5, поэтому и на его выходе имеется нулевой код, который поступает на вход А блока 4 сравнения. Поскольку в большинстве случаев |§ - М I 0, то на выходе А В блока 4 сравнения имеется Лог. О, генератор 7 не блокируется, его импульс переводит счетчик 6 в Лог. 1. В блоке 5 величина кода дифференциального диапазона анализа А М, поступающая на вход 22 анализатора, умножается на 1, результат умножения в блоке сравнения сравнивается с величиной |Јi -Ml или fЈi -Mi ДМ, то на выходе А В блока 4 появляется Лог. 1, генератор 7 блокируется, эта Лог. 1 поступает на третий вход первого элемента 2 И-ИЛИ 12 и совместно с Лог. 1 с входа 24 разрешает прохождение тактового импульса с входа 23 на выход элемента 2 И-ИЛИ 12 и далее через элемент НЕ 13 на вход чтения/записи блока 8 памяти.

Информация с выхода блока 8 памяти подается на вход сумматора 10, в котором этот код суммируется с Лог. 1, и увеличенное число записывается в блок 8 памяти по адресу 1. Если |Ј, -Ml Л М, то счетчик 6 при следующем тактовом импульсе генератора 7 переходит в состояние 2, на выходе блока 5 появляется код 2 ДМ, а затем 3 АМ-К А М, пока не станет |Јi - М| К AM. Тогда по вышеописанной схеме произойдет запись числа, имевшегося по адресу К в блоке 8 памяти. Адрес AN+I блока памяти знаковый, его понятие означает (условно), что имеется не только ячейка с номером К (по разрядам адресов), ном ячейка с номером -К Знак определяется по состоянию переноса в блоке 2. Сигнал переноса поступает на первый вход первой группы входов третьего элемента 2 И-ИЛИ 18 и через него на адресный вход блока 8 памяти, поэтому при записи в блок памяти учитывается и знак.

Если объем входной выборки i 14,1 « 2№Л входные отсчеты § распределяются в 1-ячейках блока 8 памяти, причем вероятность попадания двух чисел в одну ячейку весьма мала и при считывании из памяти входные числа выстраиваются по возрастанию величин, т.е. анализатор обеспечивает ранжирование входных величин.

В случае обьема выборки I 2N+1 анализатор обеспечивает вычисление гистограммы входных чисел, можно смещать центр гистограммы М и ее шаг AM

В режиме стирания на вход 26 анализатора подается сигнал Лог. 1. При этом через элемент ИЛИ 15 запускается формирователь 16 импульсов, импульс которого через элемент 2 И-ИЛИ и элемент 19 задер0 жки устанавливает в нуль счетчик 6. Поскольку блок умножения заблокирован в отсутствии режима анализа, то на его выходе имеется информационный нуль, на выходе блока 4 сравнения также имеется нуль и

5 генератор 7 тактовых импульсов разблокирован. Счетчик 6 последовательно опрашивает адреса блока 8 памяти причем (N-H)-u разряд счетчика 6 в режиме считывания через элемент 2 И-ИЛИ 18 подключен к (N+1)0 му адресному входу блока 8 памяти. Формула изобретения Статистический анализатор, содержащий блок памяти, сумматор, счетчик, блок сравнения, элемент ИЛИ, элемент задерж5 ки, генератор тактовых импульсов, выход блока памяти соединен с первым входом сумматора, второй вход которого является входом задания логической единицы анализатора, выход счетчика соединен с ад0 ресным входом блока памяти, отличающийся тем, что, с целью повышения быстродействия, в него введены блок вычитания, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок умножения, блок элементов И,

5 три элемента 2И-ИЛИ, формирователь импульсов, два элемента НЕ и аналого- цифровой преобразователь, причем информационным входом анализатора является информационный вход аналого-цифрового

0 преобразователя, выход которого соединен с входом уменьшаемого блока вычитания, вход вычитаемого которого соединен с входом установки начального значения матема- тического ожидания анализатора,

5 информационный выход блока вычитания соединен с первой группой входов блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход переноса блока вычитания соединен с второй группой входов блока элементов ИСК0 ЛЮЧАЮЩЕЕ ИЛИ, выходы которого соединены с первым входом блока сравнения, второй вход которого соединен с выходом блокз умножения, вход множимого которого соединен с входом задания шири5 ны дифференциального диапазона анализатора, вход множителя блока умножения соединен с выходом счетчика, суммирующий вход счетчика соединен с выходом генератора тактовых импульсов и с первым входом первой группы входов первого элемента 2И-ИЛИ, второй вход первой группы входов которого соединен с входом первого элемента НЕ, первым входом элемента ИЛИ и с входом сброса анализатора, второй вход элемента ИЛИ является входом запуска анализатора, выход первого элемента НЕ соединен с управляющим входом блока элементов И, информационные входы которого соединены с выходом сумматора, выход Больше блока сравнения соединен с входом запуска генератора тактовых импульсов, с первым входом второй группы входов первого элемента 2И-ИЛИ, второй вход второй группы входов которого является тактовым входом анализатора и соединен с входом синхронизации аналого-цифрового преобразователя и с первым входом первой группы входов второго элемента 2И-ИЛИ, второй вход первой группы входов которого соединен с третьим входом второй группы входов первого элемента 2И-ИЛИ, с тактовым входом блока умножения, с входом начальной установки математического ожидания анализатора и с первым входом первой группы входов третьего элемента 2И-ИЛИ, второй вход первой группы входов которого

соединен с выходом переноса блока вычитания, выход формирователя импульсов соединен с первым и вторым входами второй группы входов второго элемента 2И-ИЛИ, выход которого через элемент задержки соединен с входом сброса счетчика, выход переноса которого соединен с первым входом второй группы входов третьего элемента 2И-ИЛИ, второй вход второй группы входов которого соединен с входом формирователя импульсов и с выходом элемента ИЛИ, выход третьего элемента 2И-ИЛИ соединен со старшим разрядом адресного входа блока памяти, выход первого элемента 2И-ИЛИ соединен с входом второго элемента НЕ, выход которого соединен с входом чтения - записи блока памяти.

гч

25 IB

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения преобразования Фурье | 1986 |

|

SU1325509A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Анализатор спектра сигналов | 1986 |

|

SU1399765A1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

Изобретение относится к вычислительной технике и может быть использовано в ), устройствах обработки сигналов, анализаторах, обеспечивая при этом вычисление чистограмм входных процессов, а также сортировку входных данных по заданной шкале. Цель изобретения - повышение быстродействия за счет уменьшения количества анализируемых входных чисел. Для решения указанной задачи анализатор содержит генератор тактовых импульсов, счетчик, три элемента 2И-ИЛИ, АЦП, блок сравнения, сумматор, блок умножения, два элемента НЕ, формирователь импульсов, элемент задержки, блок элементов И, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок вычитания и блок памяти. 1 ил.

| Устройство для формирования гистограммы случайных чисел | 1984 |

|

SU1198538A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для анализа распределений случайных процессов | 1985 |

|

SU1247896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-07—Публикация

1988-03-09—Подача