1

Изобретение относится к запоминаюа,им устройствам.

Известны программируемые запоминающие матрицы.

Одно из известных устройств содержит дешифратор и матрицу запоминающих МОП-транзисторов 11 .

Недостаток этого устройства - низкое быстродействие.

Наиболее близким к предлагаемому является программируемая логическая матрица, содердащая блок входных инверторов, п-разрядный дешифратор и т-разрядную матрицу МОП-транзисторов с промежуточными шинами и ортогональными выходными шинами, причем между, каждой парой промежуточных шин и каждой парой выходных шин расположены шины нулевого потенциала -.

Недостатком известного устройства является большое количество шин нулевого потенциала.

Цель изобретения - упрощение программируемой логической матрицы.

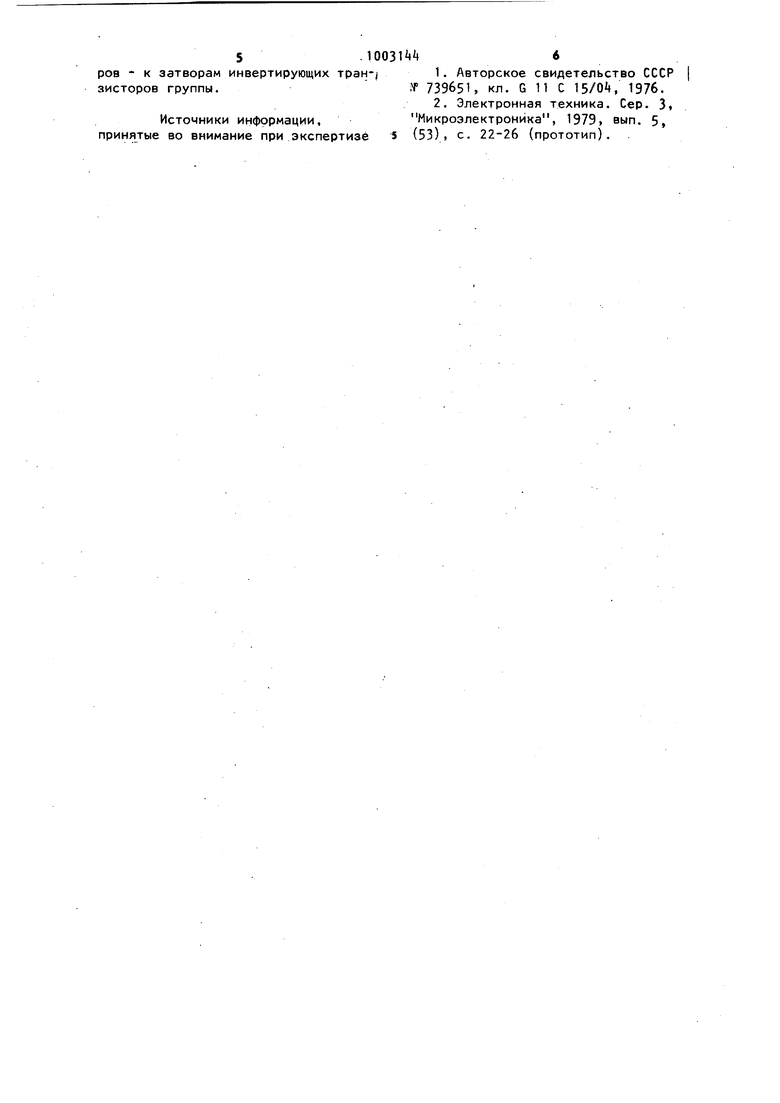

Поставленная цель достигается тем, что в программируемую запоминающую матрицу, содержащую дешифрирующие и выходные транзисторы, группу нагрузочных транзисторов и группу инвертирующих транзисторов, затворы которых являются информационными входами матрицы и соединены с затворами одних из дешифрирующих транзисторов, причем истоки инвертирующих транзисторов группы подключены к шине нулевого потенциала, а стоки соединены с 15 затворами других дешифрирующих транзисторов и истоками нагрузочных тран зисторов группы, стоки и затворы которых подключены к шине питания, стоки дешифрирующих транзисторов и затворы выходных транзисторов соединены с промежуточными шинами матрицы, стоки одних из выходных транзисторов подключены к нечетным выходным шинам матрицы, а стоки других выходных тра зисторов - к четным выходным шинам матрицы, введены инвертирующий и нагрузочный транзисторы, причем сток инвертирующего транзистора соединен с входами четных выходных шин, истоками одних из выходных транзисторов и истоком нагрузочного транзистора, затвор и сток которого подключены к шине питания, исток инвертирующего транзистора соединен с шиной нулевого потенциала, затвор инвертирующего транзистора является тактирующим входом матрицы и соединен с входами нечетных выходных шин и истоками других выходных транзисторов, истоки одних из дешифрирующих транзисторов подключены к стокам инвертирующих транзисторов группы, а истоки других дешифрирующих транзисторов - к затво рам инвертирующих транзисторов гфупп На чертеже представлена принципиа ная схема предлагаемого устройства. Устройство содержит дешифрирующее МОП-транзисторы 1, группу инвертирующих МОП-транзисторов 2. На чертеже обозначены информационные входы 3 матрицы, промежуточные шины , выходные шины 5. Устройство содержит также инвертирующий МОП-транзистор 6 нагрузочный МОП-транзистор 7, группу нагрузочных МОП-транзисторов S и выходные транзисторы 9. На чертеже обозначены также тактирующий вход 10 матрицы и шина 11 питания. Программируемая запоминающая матрица работает следующим образом. На входы 3 подают входное слово, в результате чего все транзисторы 1, стоки которых подключены к запрограм мированной на данное слово шине , запираются и на выходе этой шины 14 устанавливается сигнал 1. После этого на тактирующий вход 10 подается сигнал 1, При этом на выходе каждой нечетной из шин 5 появляется сигнал О, если на пересечении этой шины 5 и выбранной шины k включен транзистор 9, сток которого соединен с данной шиной 5j сигнал 1 - в противном случае. На выходах всех четных шин 5 устанавливается сигнал О. Затем значение тактирующего сигнала изменяется с 1 на О, и на выходе каждой четной из шин 5 появляется сигнал О, если на ее пересечении с выбранной шиной т включен транзистор 9s сток которого соединен с данНОЙ шиной 5. и сигнал 1. - в противном случае. Таким образом, считывание информации осуществляется за два такта: в первом такте информация сничается с нечетных шин 5, а во втором такте - с четных шин 5Технико-экономическое преимущество предлагаемой программирующей запоминающей матрицы заключается в ее более высоком быcтpoдeйcfВИИ по сравнению с прототипом Формула изобретения Программируемая запоминающая матрица, содержащая дешифрирующие и выходные транзисторы, группу нагрузочных транзисторов и группу инвертирующих транзисторов, затворы которых являются информационными входами матрицы и соединены с затворами одних из дешифрирующих транзисторов, причем истоки инвертирующих транзисторов группы подключены к шине нулевого потенциала, а стоки соединены с затворами других дешифрирующих транзисторов и истоками нагрузочных транзисторов группы, стоки и затворы которых подключены к шине питания, стоки дешифрирующих транзисторов и затворы выходных транзисторов соединены с промежуточными шинами матрицы, стоки одних из выходных транзисторов подключены к нечетным выходным шинам матрицы, а стоки других выходных транзисторов - к четным выходным шинам матрицы, отличающаяся тем, что, с целью упрощения программируемой запоминающей матрицы, в нее введены инвертирующий и нагрузочный транзисторы, причем сток инвертирующего транзистора соединен с входами четных выходных шин, истоками одних из выходных транзисторов и истоком нагрузочного транзистора, затвор и сток которого подключены к шине питания, исток инвертирующего транзистора соединен с шиной нулевого потенциала, затвор инвертирующего транзистора является тактирующим входом матрицы и соединен с входами нечетных выходных шин и истоками других выходных транзисторов, истоки одних из дешифрирующих транзисторов подключены к стокам инвертирующих транзисторов группы, а истоки других дешифрирующих транзисто5.1003lAi A

ров - к затворам инвертирующих тран-j 1. Авторское свидетельство СССР зисторов группы. № 739651, кл. G 11 С 15/0, 1976.

Источники информации, Микроэлектроника, 1979, вып. 5, принятые во внимание при экспертизе 5 (53), с. 22-26 (прототип).

2. Электронная техника. Сер. 3,

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU960956A1 |

| Усилитель считывания | 1986 |

|

SU1348980A1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-02—Подача