Изобретение относится к электро- 1 ;;хлике и может быть использовано в iiFiTerpnni.Fiijix схемах на НТП-транзистоЦель изобретения - повышение быстродействия усилителя считывания.

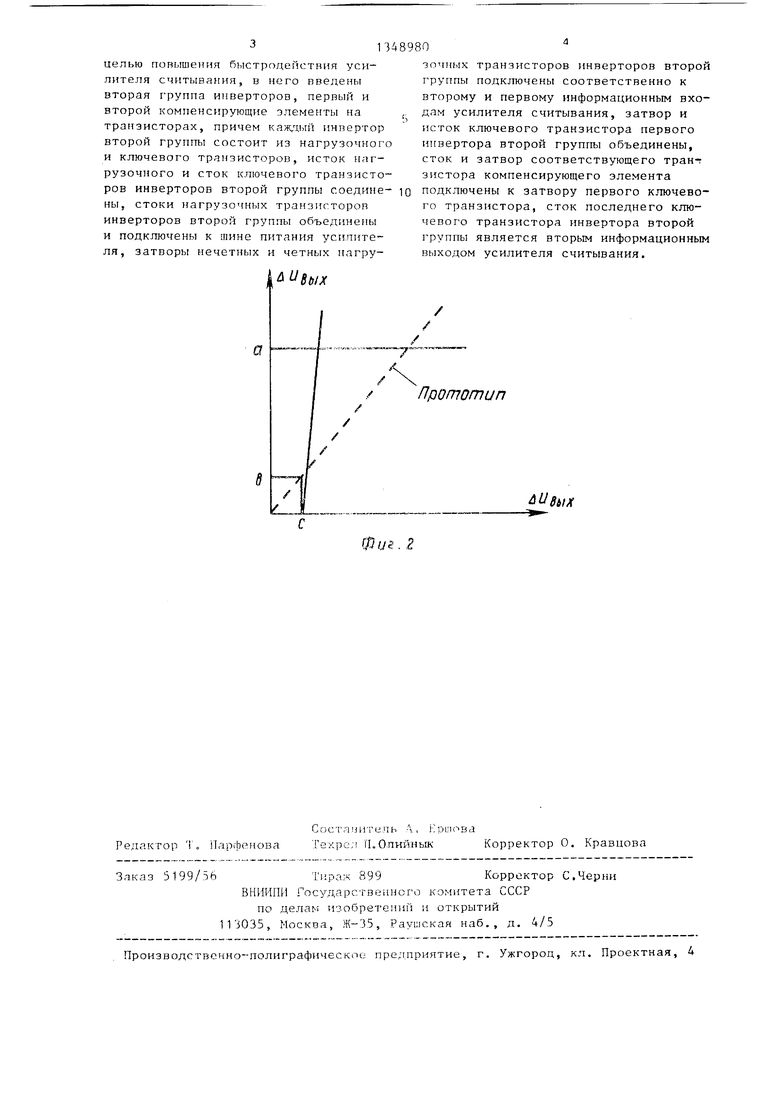

На фиг. 1 представлена схема предлагаемого усилителя считывания; на

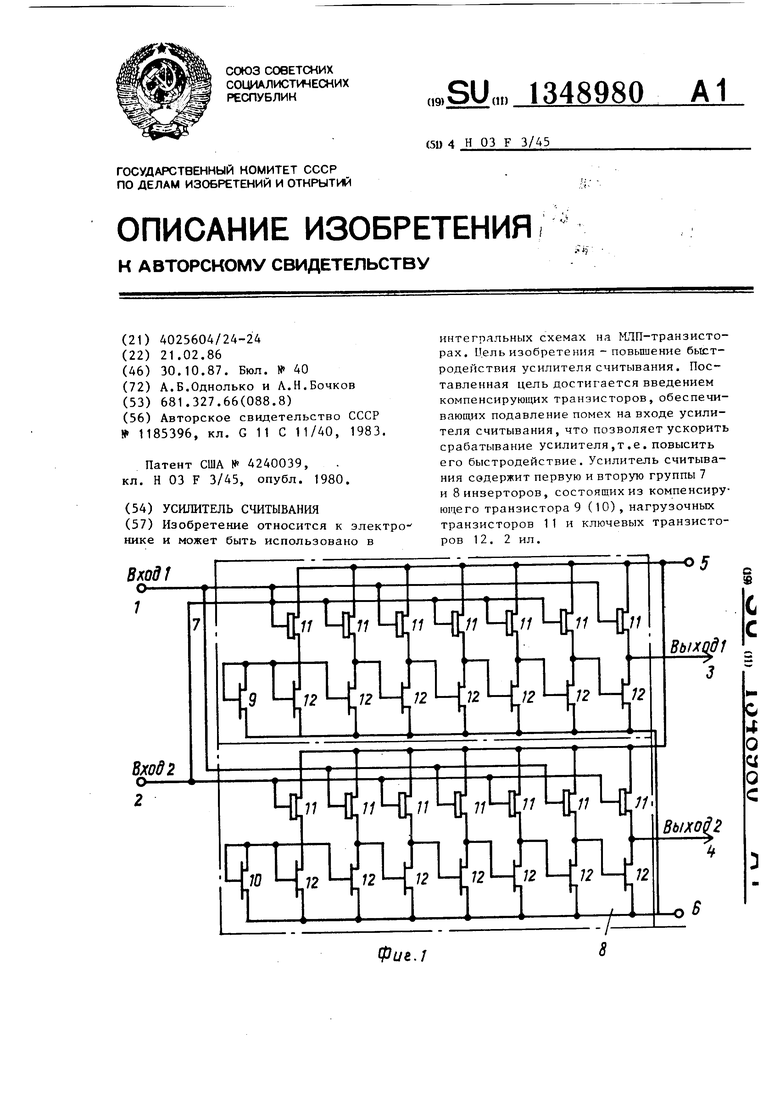

фиг, 2 - выходная характеристика уси- д входе усилителя (фиг. 2).

пителя считывания.

Усилитель считывания содержит первый и второй информационные входд;

Iи 2, первый и второй информационные выходы 3 и 4, шины 5 и 6 питания

IIчулсвого потенциала, первую и вторую группы 7 и 8 инверторов, первый :( : ор )й компенсирующие элементы 9

и lO на транзисторах, нагрузочные трлнпигторы 11, ключевые транзисто- |jbi 12.

При нулевом выходном дифференциальном сигнале на первом и втором ииформационнр 1х выходах низкий урог Г1п. При достижении некоторого уров- 25 устройстве рабочий уровень выходного

сигнала достригается при гораздо меньшем входном сиг-нале, т.е. коэффициент усиления увеличен.

ня сигнала, определяемого величиной : iHiira нуля, напряжение одного из 1111.ормационных вЕ,1ходов, определяемое П Упяриостыо входного сигнала снижа- ; :i ;. . . -. ОМ случае величина выходно- I o сигнала определяется коэффициентом

, ; 1 -1) . . Ко;)с);1л1цие11т усиления опре- ;1ог1яется количеством инверторов в цепочке.

В интегральных схемах памяти усилитель счит1 1вания должен иметь максимальную чувствительность к входному с 1М1алу для улуч1иения основного параметра - времени выборки. Однако, это требование противоречит требо- т 1иию, каслю цемуся помехоусто| чиво- сти, поскольку помехи на входе уси- Ч-ечя, связанные с работой интегральной cxeMiii, усиливаются и проходят на выход усилителя. Мощные выходные каскады отрабат1лт а1от выходной сигнал усилителя и создают тем самым допол- нительл1.1е помехи. Т.е. интегральная схема памяти с высокочувствительным усилителем счигьн ания может войти в режим генерации ло выходу и только iipij достижении на входе усилителя информационного сит нала, превышающего -..uMib помех на В111ходе интегральной cxeMiji, получаем истинное значение вы- Г информации. Поэтому с нелью предотвращения генерации по выходу -т ффиниент усиления усилителя считы- огра1И1чива1от так, чтобы усили30

35

40

45

50

55

.Формула изобретения

Уси.гп{тель считывания, содержащий первую г руппу инверторов, каждый из которых состоит из нагрузочного и ключевого транзисторов, причем стоки нагрузочных транзисторов объединены и подключены к шине гштания уси.1П1те- ля, затвор) нечетнь х а1фузочн 5 х транзисторов об71ед, и являются пер1зым инф(.)15ма ;иоь1Н1,1м входом усилителя считына 1ия, затворы четн,1х ;аг- рузоч(ых тра 1зисторов объединень и вторым информа 1ионн лм входом уси1П теля считывания, исток нагрузочного и сток ключе зого транзисторов каж. ;ого И 1вертора первой группы соединены, затвор и сток кл С1чевого транзистора первого и 1вертора первой групп) объединеяь, затвор ключевого транзистора каждого И шертора первой гру1П1 л, кроме ервого, соединен со стоком ключевого транзистора предыдущего инвертора Г ервой группы, сток послед {его ключевого тра 13 1стора является информа П10 1ным выходом усилителя ., истоки ключевых транзисторов объединены и подкл очены к шине нулевого потенциала усилителя, о т л и ч а о щ и 11 с я тем, что, с

ваемые помехи не проходили на выход интегрально схемы.

Характерные точки: а - рабочий уровень выходного сигнала усилителя; в - допустимый уровень помех на выходе усилителя, т.е. уровень сигнала, который не проходит на выход интегральной схемы; с - уровень помех на

5

()

Из передаточ 1ой характеристики видно, что в случае линейного усилителя максимальная чувствительность ограничена отношением допуст1тмого уровня помех на выходе к уровню помех на входе. В предлагаемом устройстве передаточная характеристика нелинейна, что создает возможность полностью исключить усиление помех на входе усилителя. Для рабочего входного сигнала, преньппающего уровень помех по входу, коэффициент усиления гораздо больше, чем в схеме прототипа. Таким образом, в предлагаемом

0

5

0

5

0

5

.Формула изобретения

Уси.гп{тель считывания, содержащий первую г руппу инверторов, каждый из которых состоит из нагрузочного и ключевого транзисторов, причем стоки нагрузочных транзисторов объединены и подключены к шине гштания уси.1П1те- ля, затвор) нечетнь х а1фузочн 5 х транзисторов об71ед, и являются пер1зым инф(.)15ма ;иоь1Н1,1м входом усилителя считына 1ия, затворы четн,1х ;аг- рузоч(ых тра 1зисторов объединень и вторым информа 1ионн лм входом уси1П теля считывания, исток нагрузочного и сток ключе зого транзисторов каж. ;ого И 1вертора первой группы соединены, затвор и сток кл С1чевого транзистора первого и 1вертора первой групп) объединеяь, затвор ключевого транзистора каждого И шертора первой гру1П1 л, кроме ервого, соединен со стоком ключевого транзистора предыдущего инвертора Г ервой группы, сток послед {его ключевого тра 13 1стора является информа П10 1ным выходом усилителя ., истоки ключевых транзисторов объединены и подкл очены к шине нулевого потенциала усилителя, о т л и ч а о щ и 11 с я тем, что, с

целью повышения быстродействия усилителя считывания, в него введены вторая группа инверторов, первый и второй компенсирующие элементы на транзисторах, причем каждый иннертор второй группы состоит из нагрузочного и ключевого транзисторов, исток нагрузочного и сток ключевого транзисторов инверторов второй группы соедине- юподключены к затвору первого ключевоны, стоки нагрузочных транзисторовго транзистора, сток последнего клюинверторов второй группы о6ъединер1ычевого транзистора инвертора второй

и подключены к шине питания усилите-группы является вторым информационным

ля, затворы нечетных и четных нагру-выходом усилителя считывания.

зочных транзисторов инверторов второй группы подключены соответственно к второму и первому информационным входам усилителя считывания, затвор и исток ключевого транзистора первого инвертора второй группы объединены, сток и затвор соответствующего трант зистора компенсирующего элемента

/

/

/

/

/ Прототип

лидых

-

Редактор Т. Парфенова

Составитель Л, i--j:)iii(

Техрел П.Олийнык Корректор О. Кравцова

Заказ 5199/56 Гира;ч 899Корректор С.Черни

ВННИПИ Государственного комитета СССР

по делак; изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-долиграфическос; предприятие, г. Ужгород, кл. Проектная, 4

Фи&.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания на КМОП-транзисторах | 1983 |

|

SU1149310A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

Изобретение относится к электронике и может быть использовано в интегральных схемах на ВДП-транзисто- рах. Цель изобретения - повьпиение быстродействия усилителя считывания. Поставленная цель достигается введением компенсирующих транзисторов, обеспечивающих подавление помех на входе усилителя считывания, что позволяет ускорить срабатывание усилителя,т.е. повысить его быстродействие. Усилитель считывания содержит первую и вторую группы 7 и 8 инверторов, состоящих из компенсирующего транзистора 9 (10) , нагрузочных транзисторов 1 1 и ключевых транзисторов 12. 2 ил. Bxodf о 7 У„ ы„ LJ,, ы„ ы, ы„ Ц ТО - 72 - 72 - ;2 - ;2 1 т 1 1 Bxoff2 о 2 Ц1 77Ц7/Ц1 //Ц;;Ы;;Ц;Ы;; 05 11 Вых, / с 72 Ч;2 ;Ы;; с 4 О с: о с //Ц;;Ы;;Ц;Ы;; -I п п п 12 L-Г;2Н-;2 1 1 т л Выхода i Фие.1 -I- 8

| Формировтель напряжения смещения подложки для интегральных схем | 1983 |

|

SU1185396A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 4240039, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1987-10-30—Публикация

1986-02-21—Подача