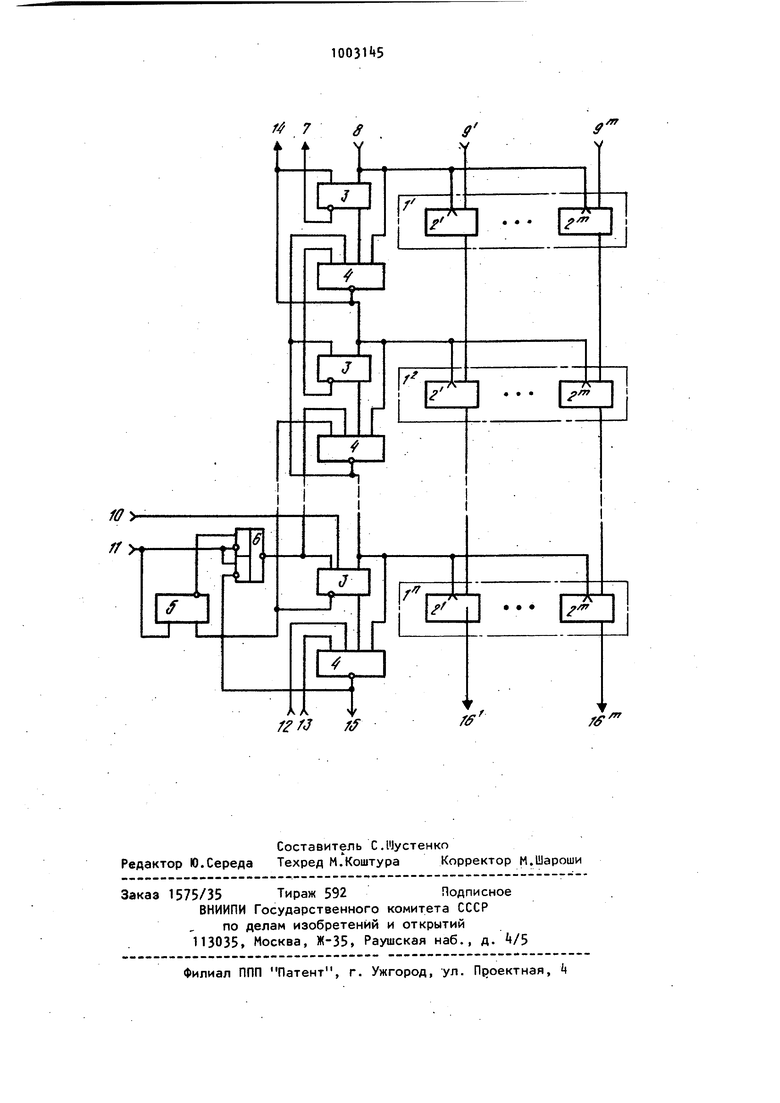

Изобретение относится к цифровой вычислительной технике и может быть использовано в аппаратуре передачи дискретной информации и в вычислитель ной технике для сопряжения устройств .обладающих различным быстродействием Известно бус ерное запоминающее устройство ЗУ ), содержащее регистры данных, вентили записи в регистры и управляющие схемы .записи в регистры, выполненные на основе триггеров и элементов совпадения, в которых запись данных в ЗУ и перезапись данных внутри ЗУ осуществляется импульсами, вырабатываемыми тактируемой управляющей схемой tl 1 . Недостатком этого устройства является необходимость внешнего источника тактовых импульсов, а также сложность схемного решения из-за большого количества элементов. Кроме того, в указанных устройствах наблюдается искажение считываемой информации при асинхронной работе подключенного к буферному ЗУ. Наиболее близким по технической сущности к предлагаемому является буферное ЗУ магазинного типа, содержащее ряд кодовых регистров, соединенных между собой последовательно в каждом разряде, шины сигнала записи, сигнала контроля записи числа, сигнала отброса, сигнала стирания записи, сигнала контроля наличия числа и шины для наращивания устройства, причем информационные входы первого регистра подключены к информационным входам, а информационные выходы последнего кодового регистра - к выходам буфер- ного ЗУ. Каждый регистр имеет схему управления выполненную на элементе И-НЕ и триггере, единичный вход которого соединен с управляющими входами данного регистра и входом данного элемента И-НЕ, я нулевой вход триггера соединен с выходом того же элемента И-НЕ, К другим трем входам элемента | И-НЕ подключены так же единичный выг. ход данного триггера, нулевой выход последующего триггера и выход последующего элемента И-НЕ.. Управляющие входы первого регистра подключены к шине записи. Нулевой выход триггера в схеме управления первым регистром подключен к шине контроля записи чис ла, выход элемента И-НЕ всхёме управления последним 1эегистром подклюМен к шине сигнала контроля наличия числа 23 .,Недостатком известного устройства является низкое быстродействие устройства, вызванное запретом поразряд ной переписи информации в запоминающ устройстве до окончания сигнала стир ния записи. Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается тем что в буферное запоминающее устройств во, содержащее последовательно соединенные регистры, входы первого из которых являются информационными входами устройства, выходы каждого из. ре гистров подключены к информационным входам последующего регистра, а выходы последнего регистра являются информационными выходами устройства, последовательно соединенные через элементы. И-НЕ триггеры, первый выход каждого из которых подключен к. первом входу соответствующего элемента И-НЕ выход каждого из элементов И-НЕ подкл чен к первому входу последующего триггера, к управляющему входу соответствующего регистра, к первому входу п оследующего элемента И-НЕ, к второму входу предыдущего триггера и к второму.входу предыдущего элемента И-НЕ, первый выход каждого триггера подключен к третьему входу последующего элемента И-НЕ, второй выход каждого триггера, кроме последнего, подключен к четвертому входу предыдущего элемента И-НЕ, первый и второй входы и второй выход первого триггера, второй и четвертый входы и выход последнего элемента И-НЕ являются соответст вующими управляющими входами и выходами устройства, введены дополнительный триггер и элемент И-ИЛИ-НЕ, первый вход которого подключен к выходу дополнительного триггера, первый вход дополнительного триггера подключен к второму выходу последнего триггера. второй вход триггера подключен к второму и третьему входам элемента И-ИЛИНЕ и является соответствующим управляющим входом устройства, четвертый вход элемента И-ИЛИ-НЕ подключен к выходу последнего элемента И-НЕ, выход элемента И-ИЛИ-НЕ подключен к второму входу последнего триггера и к второму входу предыдущего элемента И-НЕ. Быстродействие устройства повышается в результате того, что после считывания информации из буферного запоминающего устройства новая информация переписывается в последний регистр до окончания сигнала стирания записи в нем, а дополнительный триггер с схемой И-ИЛИ-НЕ обеспечивает сохранность информации, ааново записанной в последний регистр устройства. На чертеже изображена функциональная схема предлагаемого буферного ЗУ. Устройство содержит регистры , каждый из которых.выполнен на триггерах , триггеры 3 схем управления регистрами, элементы. И-НЕ, дополнительный триггер 5, элемент И-ИЛИ-НЕ 6, управляющий выход 7 записи числа, управляющий вход 8 записи, информационные входы устройства 9-|-9f, управляющий вход 10. сброса, управляющий вход 11 сигнала стирания записи, управляющие входы 12-„14 для наращивания устройства, управляющий выход 15 сигнала, контроля наличия числа, информационные выходы устройства. Устройство работает следующим образом. При поступлении сигнала записи на вход 8 записи в первый регистр 1 производится запись информации, одновременно сраб.атывает триггер 3 схемы управления первого регистра и сигнал с его единичного выхода разблокирует перв,ый элемент И-НЕ k. Сигнал, появившийся на выходе первого элемента И-НЕ k, разрешает перезапись информации во второй регистр 2, к же происходит срабатывание второго триггера 3, возврат в исходное состояние первого триггера 2 и блокировка второго элемента И-НЕ k. Сигналы на единичном выходе первого триггера 2 и на нулевом выходе второго триггера блокируют первый элемент И-НЕ 4 и сигнал перезаписи информации во второй регистр 1 заканчивается, при этом разблокируется второй элемент И-НЕ k, . сигнал на выходе которого разрешает перезапись информации в третий регистр 1-J- Таким образом, осуществляется последовательный сдвиг, информации, поступившей в запоминающее устройство, до регистра, элемент И-НЕ k схемы управления которого заблокирован сигналом с нулевого выхода три|- гера схемм управления следующего регистра. После окончания сигнала перезаписи информации в последний регистр If, и при наличии сигналов на входах 12 и 13 триггер схемы управления последнего регистра возвращается в исходное состояние сигналом с выхода элемента И-ИЛИ-НЕ 6, на инверсный .вход которого поступает сигнал с выхода последнего элемента И-НЕ 4. -После считывания информации из, последнего кодового регистра подается сигнал на вход 11 стирания записи, который блокирует второй вентиль и открывает первый вентиль элемента И-ИЛИ-Н 6 и поступает на единичный вход дополнительного триггера 5 схемы сброса, оставляя его в исходном состоянии. Сигнал с выхода элемент.а И-ИЛИ-НЕ возвращает триггер последней схемы управления в ис;;одное состояние и блокирует предпоследний элемент И-НЕ t, сигнал с нулевого выходя триггера 3 опрокидысает триггер схемы сброса в единичное состояние, блокируя тем самым первый вентиль элемента И-ИЛИ-НЕ 6, и подает разрешающий сигнал на первый вход предпоследнего элементу И-НЕ . Сигнал.на выходе элемента И-ИЛИ-НЕ 6 заканчивается, разблокируя эле.мент И-НЕ схемы управления предпоследнего регистра, если триггер предыдущей схемы управления находится в единичном состоянии, т.е. в регистре записано число, нз выходе этого элемента И-НЕ 4 появится сигнал разрешающий перезапись информации в последний регистр и устанавливагщий . триггер схемы управления последнего регистра в единичное состояние, в противном случае верезапись не производится..

При этом оканчивается действие сигнала на нулевом входе триггера 5п (однако триггер остается в предудыщем состоянии) и блокируется по первому входу элемент И-НЕ k схемы управления предпоследнего регистра, что приводит к окончанию сигнала на выходе этого

элемента. Таким образом, снимается сигнал перезаписи с управляющих входов последнего регистра,срабатывает триггер схемы управления предпоследнего регистра, на выходе соответствующего элемента И-НЕ 4 вырабатывается сигнал перезаписи в предпоследний регистр и т.д., а схема сброса сохраняет свое .состояние до окончания сиг:нала на входе стирания записи. После окончания сигнала на входе стирания записи триггер схемы сброса переключается в нулевое .состояние и схема сброса возвращается в исходное состояние. -

Для увеличения информационной ем..кости буферного ЗУ оно может наращиваться последовательным подключением аналогичного устройства, для чего к входам 12, 13 и 15 и выходам одного ЗУ подключаются соответственно входы 1i{, 7 и 8 и входы ,, следующего ЗУ.

При подаче сигнала на вход 10 сброса триггер схемы управления последнего кодового регистра переключается в исходное состояние, разрешая перезапись информации из предыдущего регистра. Так как элемент И-НЕ схемы управления предыдущего регистра при этом не блокируется, осуществляется .последвательный сдвиг информации в последний регист-р и стирание всей информаци хранившейся в ЗУ. .

Регистры хранения m-разрядных чисе могут быть реализованы на RS-триггера а в схеме сброса должен быть Е-триг-, гер. Все триггеры - с инверсным управлением.

Таким образом, предлагаемое буферное ЗУ магазинного типа обеспечивает повышение быстродействия за счет . обеспечения независимости последовательного переноса информации в устройстве от регистра к регистру.после считывания от длительности сигнала стирания записи, определяемого быстродействием внешнего устройства. Скорость переноса информации в запоминающем устройстве определяется временем срабатывания логических, элементов, на которых оно реализовано. Кроме того, наличие схемы сброса упрощает последовательное соединение однотипных ЗУ для наращивания объема памяти БЗУ - имеется одинаковый состав входных и выходных шин для увеличения объема ВЗУ, которые необходимо соединить между собой в Соответствии с их функциональным назначением.

Формула изобретенР)я

Буферное запоминающее устройство, содержащее последовательно соединенные регистры, входы первого из которых являются информационными входами устройства, выходы каждого из регистров подключены к информационным входам последующего регистра, а выходы последнего регистра являются информационными выходами устройства, последовательно соединенные через элементы И-НЕ триггеры, первый выход каждого из которых подключен к первому входу последующего элемента И-НЕ, выход каждого из элементов И-НЕ подключен к первому входу последующего триггера, к управляющему входу соответствующего регистра, к первому входу последующего элемента , к второму входу предыдущего триггера и к второму входу предыдущего элемента И-НЕ, первый выход каждого триггера подключен к третьему входу последующего элемента И-НЕ, второй выход каждого триггера, кроме последнего подключен к чeтвepтo y входу предыдущего элемента И-НЕ, первый и второй входы и второй выход первого триггера, второй и четвертый входы и выход последнего элемента И-НЕ являются . соответствующими управляющими входами и выходами устройсгва, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный триггер и элемент И-ИЛИ-НЕ, первый вход которого подключен к выходу дополнительного триггера, первый вход дополнительного триггера подключен к второму выходу последнего триггера, второй вход триггера подключен к второму и третьему входам элемента И-ИЛИ-НЕ и является соответствующим управляющим входом устройства, четвертый вход элемента И-ИЛИ-НЕ подключен к выходу последнего элемента И-НЕ, выход элемента И-ИЛИ-НЕ подключен к второму входу последнего триггера и к второму входу предыдущего элемента И-НЕ.

Источники информации,

принятые во внимание при экспртизе

1.Авторское свидетельство СССР № 750565, кл. G 11 С 19/00, 1976.

2.Авторское свидетельство СССР № 763970, кл. G 11 С 1S/00, 1977

(прототип).

// Л7 f

/тт

rff

7ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1977 |

|

SU763970A1 |

| Буферное запоминающее устройство | 1977 |

|

SU763965A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1462421A1 |

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| Ферроакустическое запоминающее устройство | 1984 |

|

SU1238153A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Буферное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU842973A1 |

| УСТРОЙСТВО ФОТОМЕТРИРОВАНИЯ ИЗОБРАЖЕНИЙ С ВЫРАЖЕННЫМ МАКСИМУМОМ ПРОСТРАНСТВЕННОГО РАСПРЕДЕЛЕНИЯ ОСВЕЩЕННОСТИ | 1995 |

|

RU2084842C1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-12—Подача