Изобретение относится к автоматике и вычислительной технике и может быть использовано для сбора информации от двухпозиционных датчиков, например, в АСУТП.

Целью изобретения является повышение надежности устройства за счет ис- ключения выдачи . сбойной информации при включении питания.

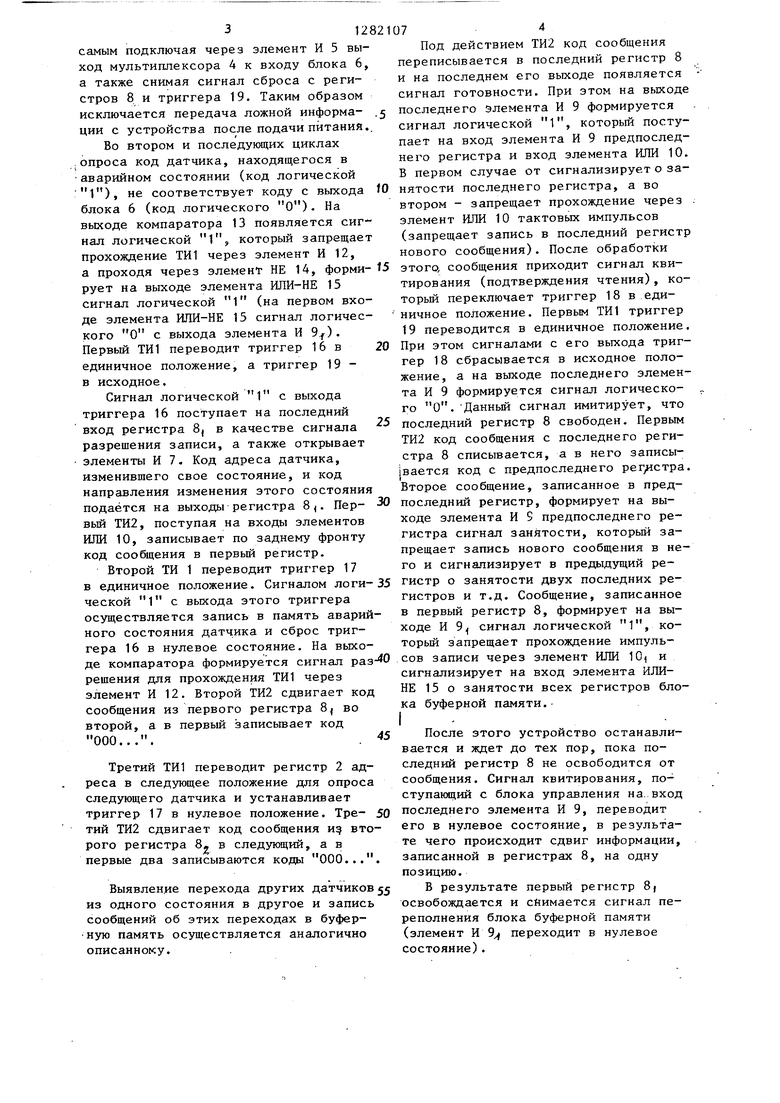

На чертеже показана функциональ- 10 первом входе (регистр 8 свободен)

ная схема устройства.

Устройство содержит (фиг.1) формирователь 1, 1№гистр 2 адреса, триггер 3, мультиплексор 4, первый элемент И 5, блок 6 оперативной памяти, илок буферной памяти, состоящий из блока элементов И 7, регистров 8, элементов И 9 и блока элементов РШИ 10, генератор 11, второй элемент И 12, компаратор 13, блок коррекции, состоящий из элемента НЕ 14, элемента ИЛИ-НЕ 15 и двух триггеров 16 и 17, а также блок управления, состоящий из триггеров 18 и 19.

Устройство работает следующим образом.

.J При включении питания на выходе формирователя 1 появляется сигнал, который устанавливает регистр 2 адреса и триггер 3 в исходное положение. Сигналом с первого выхода триггера 3 на выходе элемента И 5 формируется сигнал логического О, а сигналом с второго выхода триггера 3 D-триггер 19 устанавливается в единичное положение, а.регистры 8 - в нулевое. I .

На выходах элементов И 9 формируются сигналы логического О, триггер 18 сигналом с первого выхода триггера 19 устанавливается в нулевое положение. Начинается первый цикл опроса датчиков, при котором блок 6 устанавливается в исходное (нулевое) положение. Под воздействием кода, поступающего с выхода регистра 2 адреса на адресные входы мультиплексора 4 и блока 6, выход первого датчика подключается к выходу элемента И 5, а на выходе блокг. 6 формируется код, записанный по этому адресу. Код с выхода блока 6 поступает на первый вход компаратора 13, на второй вход которого поступает в это время сигнал логического О с элемента И 5.

Если на выходе блока 6 имеется сигнал логической 1, то на выходе компаратора 13 появляется сигнал лоJ5

на выходе элемента РШИ-НЕ 15 формируется сигнал логической 1, разре шающий производить запись кода сооб щения в блок буферной памяти. I

20

30

35

Генератор 11 выдает на своих вых дах тактовые импульсы отрицательной полярности, сдвинутые относительно друг друга на 180 . При приходе пер вого тактового импульса с первого выхода генератора (ТИ 1) триггер 16 переходит в единичное положение. Си налом логической 1 с его выхода открываются элементы И 7 и код сооб 25 щения (код номера датчика и код пол жения) подается на входы регистра 8 на последний вход регистра поступае сигнал разрешения записи с блока ко рекции.

При приходе тактового импульса с второго выхода генератора 11 (ТИ2) на выходах элементов ИЛИ 10 формиру ются отрицательные импульсы, от зад него фронта которых осуществляется запись кода в регистр 8(. Но записи не происходит, так как на входах сброса регистров присутствует сигна сброса с триггера 3.

С приходом второго ТИ1 триггер 1 переходит .в единичное положение. Си налом логической 1 с его выхода осуществляется сброс триггера 16 в нулевое положение и запись кода О в память 6 по адресу регистра 2.

При одинаковых сигналах на входа компаратора 13 на его выходе формируется сигнал логического О, разр шая прохождение импульсов через эле мент И 12. Очередной импульс перекл чает регистр 2 дреса для опроса сл дующего датчика, а триггер 17 устанавливается в исходное положение. Аналогично записывается код О во все ячейки памяти, где до этого бьш « записана логическая 1. После окон чания первого-цикла опроса на выход переполнения регистра 2 адреса появ ляется сигнал , который устанавливае триггер 3 в исходное положение, тем

40

45

50

.гической 1, который, поступая на вход элемента И 12, запрещает прохождение через него импульсов от; генератора 11. Этот же сигнал, инвертируясь элементом НЕ 14, поступает на вход элемента ИЛИ-НЕ 15, сигнализируя о переходе датчика из одного

.состояния в другое.

При сигнале логической О на

5

на выходе элемента РШИ-НЕ 15 формируется сигнал логической 1, разрешающий производить запись кода сообщения в блок буферной памяти. I

0

0

5

Генератор 11 выдает на своих выходах тактовые импульсы отрицательной полярности, сдвинутые относительно друг друга на 180 . При приходе первого тактового импульса с первого выхода генератора (ТИ 1) триггер 16 переходит в единичное положение. Сигналом логической 1 с его выхода открываются элементы И 7 и код сооб- 5 щения (код номера датчика и код положения) подается на входы регистра 8, на последний вход регистра поступает сигнал разрешения записи с блока коррекции.

При приходе тактового импульса с второго выхода генератора 11 (ТИ2) на выходах элементов ИЛИ 10 формируются отрицательные импульсы, от заднего фронта которых осуществляется запись кода в регистр 8(. Но записи не происходит, так как на входах сброса регистров присутствует сигнал сброса с триггера 3.

С приходом второго ТИ1 триггер 17 переходит .в единичное положение. Сигналом логической 1 с его выхода осуществляется сброс триггера 16 в нулевое положение и запись кода О в память 6 по адресу регистра 2.

При одинаковых сигналах на входах компаратора 13 на его выходе форми руется сигнал логического О, разрешая прохождение импульсов через элемент И 12. Очередной импульс переключает регистр 2 дреса для опроса следующего датчика, а триггер 17 устанавливается в исходное положение. Аналогично записывается код О во все ячейки памяти, где до этого бьша записана логическая 1. После окончания первого-цикла опроса на выходе переполнения регистра 2 адреса появляется сигнал , который устанавливает триггер 3 в исходное положение, тем

0

5

0

31282107

самым подключая через элемент И 5 выход мультиплексора 4 к входу блока 6, а также снимая сигнал сброса с регистров 8 и триггера 19. Таким образом исключается передача ложной информа- .5 ции с устройства после подачи питания..

Во втором и последующих циклах .опроса код датчика, находящегося в аварийном состоянии (код логической ), не соответствует коду с выхода tO блока 6 (код логического О). На выходе компаратора 13 появляется сигнал логической 1, который запрещает прохождение ТИ1 через элемент И 12,

Под действием ТИ2 код сообщения переписывается в последний регистр 8 и на последнем его выходе появляется сигнал готовности. При этом на выходе последнего элемента И 9 формируется сигнал логической 1, который поступает на вход элемента И 9 предпоследнего регистра и вход элемента ИЖ 10. В первом случае от сигнализирует о занятости последнего регистра, а во втором - запрещает прохождение через элемент ИЛИ 10 тактовых импульсов (запрещает запись в последний регистр нового сообщения). После обработки

20

а проходя через элемент НЕ 14, форми- t5 этого, сообщения приходит сигнал кви- рует на выходе элемента ИЛИ-НЕ 15 тирования (подтверждения чтения), ко- сигнал логической 1 (на первом входе элемента ИЛИ-НЕ 15 сигнал логического О с выхода элемента И 9). Первый ТИ1 переводит триггер 16 в единичное положение, а триггер 19 - в исходное.

Сигнал логической 1 с выхода триггера 16 поступает на последний вход регистра 8, в качестве сигнала разрешения записи, а также открывает элементы И 7. Код адреса датчика, изменившего свое состояние, и код направления изменения этого состояния подаётся на выходы регистра 8,. Перторый переключает триггер 18 в единичное положение. Первым ТИ1 триггер 19 переводится в единичное положение. При этом сигналами с его выхода триггер 18 сбрасывается в исходное положение, а на выходе последнего элемента И 9 формируется сигнал логического 0. Данньм сигнал имитирует, что

25 последний регистр 8 свободен. Первым ТИ2 код сообщения с последнего регистра 8 списывается, а в него записы- вается код с предпоследнего per/iCTpa. Второе сообщение, записанное в пред30 последний регистр, формирует на выходе элемента И 9 предпоследнего регистра сигнал занятости, который запрещает запись нового сообщения в него и сигнализирует в предыдущий ревый ТИ2, поступая на входы элементов ИЛИ 10, записывает по заднему фронту код сообщения в первый регистр.

Второй ТИ 1 переводит триггер 17

в единичное положение. Сигналом логи-35 гистр о занятости двух последних реческой 1 с выхода этого триггера осуществляется запись в память аварийного состояния датчика и сброс триггера 16 в нулевое состояние. На выходе компаратора формируется сигнал решения для прохождения ТИ1 через элемент И 12. Второй ТИ2 сдвигает код сообщения из первого регистра 8 во второй, а в первый записывает код 000..... 45

После этого устройство останавливается и ждет до тех пор, пока последний регистр 8 не освободится от сообщения. Сигнал квитирования, поступающий с блока управления на. вход

Третий ТИ1 переводит регистр 2 адреса в следующее положение для опроса следующего датчика и устанавливает

триггер 17 в нулевое положение. Тре- 50последнего элемента И 9, переводит

тий ТИ2 сдвигает код сообщения кщ вто-его в нулевое состояние, в результарого регистра 8, в следующий, а вте чего происходит сдвиг информации,

первые два записываются коды 000....записанной в регистрах 8, на одну

позицию.

Выявление перехода других датчиков 55 В результате первый регистр 8|

из одного состояния в другое и записьосвобождается и снимается сигнал песообщений об этих переходах в буфер-реполнения блока буферной памяти

ную память осуществляется аналогично(элемент И 9 переходит в нулевое

описанноку.состояние).

Под действием ТИ2 код сообщения переписывается в последний регистр 8 и на последнем его выходе появляется сигнал готовности. При этом на выходе последнего элемента И 9 формируется сигнал логической 1, который поступает на вход элемента И 9 предпоследнего регистра и вход элемента ИЖ 10. В первом случае от сигнализирует о занятости последнего регистра, а во втором - запрещает прохождение через элемент ИЛИ 10 тактовых импульсов (запрещает запись в последний регистр нового сообщения). После обработки

0

t5 этого, сообщения приходит сигнал кви- тирования (подтверждения чтения), ко-

торый переключает триггер 18 в единичное положение. Первым ТИ1 триггер 19 переводится в единичное положение. При этом сигналами с его выхода триггер 18 сбрасывается в исходное положение, а на выходе последнего элемента И 9 формируется сигнал логического 0. Данньм сигнал имитирует, что

5 последний регистр 8 свободен. Первым ТИ2 код сообщения с последнего регистра 8 списывается, а в него записы- вается код с предпоследнего per/iCTpa. Второе сообщение, записанное в пред0 последний регистр, формирует на выходе элемента И 9 предпоследнего регистра сигнал занятости, который запрещает запись нового сообщения в него и сигнализирует в предыдущий регистров и т.д. Сообщение, записанное в первый регистр 8, формирует на выходе И 9 сигнал логической 1, который запрещает прохождение импульсов записи через элемент ИЛИ 10 и сигнализирует на вход элемента ИЛИ- НЕ 15 о занятости всех регистров блока буферной памяти.I

После этого устройство останавливается и ждет до тех пор, пока последний регистр 8 не освободится от сообщения. Сигнал квитирования, поступающий с блока управления на. вход

Дальнейшая работа устройства происходит аналогично описанному.

Таким образом, первый цикл работы устройства после включения питания отводится для обнуления блока оперативной памяти, т;е. для исключения передачи сбойной информации.

Формула изобретения

Устройство для ввода информации, содержащее мультиплексор, регистр адреса, блок оперативной памяти компаратор, блок коррекции, блок управтем, что, с целью повьппения надеж ности устройства за счет исключен выдачи сбойной информации при вкл чении питания, устройство содержи

5 формирователь, триггер, два элеме та И и генератор, первый выход к торого соединен с вторь1м входом б ка управления, третьим входом бло коррекции и первым входом второго

О элемента И, вьтход которого соедин с стробирукяцим входом регистра ад са, выход переполнения которого с динен с первым входом триггера, п вый выход которого соединен с вто

ления и блок буферной памяти, инфор- 5 входом первого элемента И, выход

мационные выходы которого являются. информационными выходами устройства, информационные входы мультиплексора являются информационными входами устройства, информационные выходы регистра адреса соединены с адресными входами мультиплексора, адресными входами блока оперативной памяти и информационными входами группы блока буферной памяти, выход готовности которого является управляющим выходом устройства, выход компаратора соединен с вторым входом блока коррекции, первый выход которого соединен с входом разрешения записи блока буферной памяти, второй выход .блока коррекции соединен с входом стробирования блока оперативной памяти, выход которого соединен с первым входом компаратора и вторым информационным входом блока буферной памяти, отличающееся

Редактор О,Головач Заказ 7267/47

Составитель В.Файзрахманов

Техред Л.Сердюкова Корректор Л.Пилипенко

Тираж 670 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

тем, что, с целью повьппения надежности устройства за счет исключения выдачи сбойной информации при включении питания, устройство содержит

формирователь, триггер, два элемента И и генератор, первый выход которого соединен с вторь1м входом блока управления, третьим входом блока коррекции и первым входом второго

элемента И, вьтход которого соединен с стробирукяцим входом регистра адреса, выход переполнения которого соединен с первым входом триггера, первый выход которого соединен с вторым

которого.соединен с первым информаци- ОНН1Д4 входом блока буферной памяти, информационным входом блока оперативной памяти и вторым входом компаратора, выход формирователя соединен с входом сброса регистра адреса и вторым входом триггера, второй выход которого соединен с входом адреса блока буферной памяти, и первым входом блока управления, выход которого соединен с входом подтверждения чтения блока буферной памяти, выход переполнения которого соединен с пер вым входом блока коррекции, второй

вход которого объединен с вторым входом второго элемента И, выход мультиплексора соединен с первым входом первого элемента И, второй выход генератора соединён с входом синхронизации блока буферной памяти, третий вход блока.управления является входом квитирования устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1989 |

|

SU1644120A2 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для сопряжения памяти с процессором | 1986 |

|

SU1377866A1 |

| Устройство для реализации нормальных алгорифмов Маркова | 1987 |

|

SU1455345A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сбора информации от двухпозиционных датчиков, например, в АСУТП. Цель изобретения - повышение надежности за счет исключения выдачи сбойной информации при включении питания. Устройство содержит формирователь регистр 2 адреса, триггер 3, мультиплексор, 4, два элемента ИЗ, 12, блок 6 оперативной памяти, блок буферной памяти, блок коррекции, генератор 11, компаратор 13, блок управления. Устройство производит циклический опрос датчиков, подключенных к входам мультиплексора. , Состояние каждого датчика сравнивается с его состоянием на предыдущем цикле опроса, хранящемся в блоке оперативной памяти. При изменении состояния какого-либо датчика происходит запись- кода адреса этого датчика и информации о его состоянии в двух последних циклах опроса (текущем и предьщущем) в блок буферной памяти. После этого выполняется коррекция информации в блоке оперативной . При включении питания срабатывает формирователь и происходит установка триггера в состояние, при котором информационный вход блока оперативной памяти обнулен, а запись информации в буферную память блокирована (подан сигнал сброса). В результате в первом цикле опроса датчиков в блоки оперативной и буферной памяти заносится нулевая информация. По окончании первого цикла опроса триггер изменяет свое состояние, и устройство переходит в рабочий режим. Стирание оперативной и буферной памяти после включения питания исключает передачу ложной информации в первом цикле опроса. 1 ил. (Л

Авторы

Даты

1987-01-07—Публикация

1985-01-04—Подача