(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

1

Изобретение относится к цифровой вычислительной технике, технике пере. дачи дискретной информации и телеграфии, а более точно к аппаратуре ввода (Вывода данных и сопряжения узлов, обладающих разным быстродействием.

Известно буферное запоминающее устройство (ЗУ), содержащее регистры памяти и сдвиговые регистры, содержащие в каждом разряде каскад на- RS триггерах с элементами записи, управляющий каскад на 1 -триггере и че- тьрех элементах совпадения {J-JИзвестно гакже ЗУ, содержащее в каждом каскаде регистр, выполненный на Э - триггерах, управляющий счетиый триггер, элемент задержки .

Общими недостатками этих устройств являются сложность их выполнения и большое количество элементов.

Наиболее близким из известных по технической сущности к предложенному является буферное ЗУ 3, содержащее кодовые регистры, информационные входы

2

которых соединены со Bxoaavm устройства, выходы кодовых регистров подключены к выходам устройства, управляющие входы кодовых регистров соединены с шиной записи и нулевым входом первого триггера, единичные выходы триггеров соединены с первыми входами элементов И-НЕ, нулевой выход первого триггера соединен с шиной сигнала контроля записи числа, шину сигнала стирания за10писи, шину сигнала сброса и шину сигнала контроля наличия числа, соединенную с выходом последнего элемента И-НЕ.

Недостатком прототипа является сложность схемы, обусловленная применением

15 управляемых импульсных перезаписьшающих генераторов.

Цедь изобретения - упрощение буферного запоминающего устройства.

Поставленная цель достигается тем,

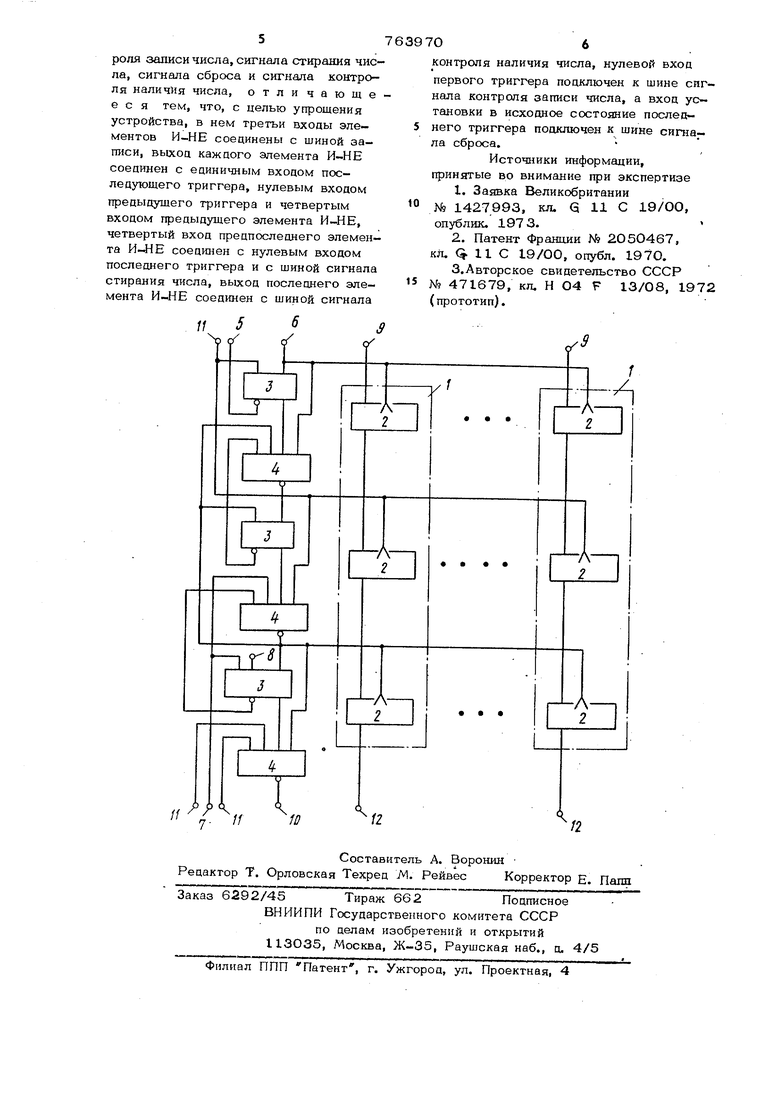

20 что в устройстве третьи входы элементов И-JiE соединены с шиной записи, выход каждого элемента И-НЕ соединен с единичным входом последующего триггера, нулевым входом предыдущего триг гера и четвертым входом предыдущего элемента И-НЕ, четвертый вход пред-, .последнего элемента И-НЕ соединен с нулевым входом последнего триггера и с шиной сигнала стирания числа. Выход последнего элемента И-НЕ соединен с шиной сигнала контроля наличия числа, нулевой вход первого триггера подключен к шине сигнала контроля записи числа, а вход установки в исходное состояние последнего триггера подключен к шине сигнала сброса. Сущность предлагаемого буферного Я поясняется чертежом,на котором предст лена функциональная схема устройства. ЗУ содержит кодовые регистры 1 выполненные на триггерах 2 , триггеры 3, элементы И-НЕ 4, шину 5 сигнала контроля записи числа, шину за писи 6, шину 7 сигнала стирания записи, шину 8 сигнала сброса, входы 9, шину 1О сигнала контроля наличия числа, входы 11 для наращивания устройст ва, выходы 12. ЗУ работает следующим образом. Пр поступлении импульса записи на шину 6 производится запись числа в кодовые регистры I первого триггера 2 в резул тате чего опрокидывается триггер 3 и сигнал с его единичного выхода разрешает срабатывание первого элемента И-НЕ 4. ГТри-срабатывании, первого элемента 4 производится перезапись числа во второй триггер 2, опрокидывание второго триггера 3, возврат в исходное состояние первого триггера 2 и блокировка входа второго элемента И-НЕ 4. Сигналы с нулевого выхода второго триггера 3 и единичного выхода первого триггера 3 после их опрокидывания возвращают первый элемент И-ЛЕ 4 в исходное состояние. При этом сигнал перезаписи заканчивается и разблокируется второй элемент И-НЕ 4. Дальнейшая перезапись числа происходит аналогично до каскада, вход элемента И-НЕ 4 которого заблокирован сигналом с нулевого выхода триггера 3 следующего каскада. При подаче сигнала стирания на шину 7 последнего триггера 3 он опрокидывается в исходное состояние и вход предыдущего элемента И-НЕ 4 блокируется. По окончании сигнала стирания второй элемент И-НЕ 4 разблокируется и, если в предыдущем триггере 2 записано число, срабатывает. При этом существляется персоапись из предоследнего триггера 2, опрокидывшше оследнего триггера 3, возврат в исодное состояние второго триггера 3, предпоследнего триггера 3 и блокируетя запись в него числа. Опрокидывание последнего триггера 3 и возврат в исодное состояние ;преапослеш1его триггера 3 возвращают выходными сигналами предпослеоний элемент И-НЕ 4 в исходное состояние. При этом оканчивается сигнал перезаписи в последний триггер 2, разблокируется первый элемент И-НЕ 4 и разрешается перезапись в предпоследний триггер 2 и т.д. При подаче сигнала на шину 8 последнего триггера 3 его триггер 2 опрокидывается в исходное состояние , разрешая перезапись числа из предыдущего триггера 2. Поскольку второй элемент -НЕ 4 при этом не блокируется, произодится последовательный сдвиг в последний триггер 2 и стирание всей информации, хранившейся в ЗУ. Предложенное соединение элементов позволило исключить управляемые импульсные перезаписывающие генераторы, а значит упростить, т.е. выполнить его целиком на интегральных логических элементах. Задержка продвижения числа в устройстве составляет 4 при длительности импульса записи 3t, где - время задержки срабатьшания логического элемента. Введение дополнительной шины сброса ЗУ упрощает стирание информации во всех его каскадах. В этом случае для очистки устройства необходимо подать потенциальный сигнал на шину 8 вместо формирователя последовательности тактовых импульсов по шине стирания. Формулаизобретения Буферное запоминающее устройство, содержащее кодовые регистры, информационные входы которых соединены со входами устройства, в.ыходы кодовых регистров подключены к выходам устройства, управляющие входы первого кодового регистра соединены с шиной записи и единичным входом первого триггера, нулевой выход каждого триггера соединен со вторым входом предыдущего элемента И-НЕ, а единичный выход - со вторым входом поел еду нэщего элемента И-НЕ, и шины сигнала контроля записи числа, сигнала стирания числа, сигнала сброса и сигнала контроля наличия числа, отли чающе еся тем, что, с целью упрощения устройства, в нем третьи входы элементов И-НЕ соединены с шиной записи, выход каждого элемента И-НЕ соединен с единичным входом последующего триггера, нулевым входом предыдущего триггера и четвертым входом предыдущего элемента И-НЕ, четвертый вход предпоследнего элемента ИЛЕ соединен с нулевым входом последнего триггера и с шиной сигнала стирания числа, выход последнего элемента И-НЕ соединен с шиной сигнала 06 контроля наличия числа, нулевой вход первого триггера подключен к шине сигнала контроля записи числа, а вход установки в исходное состояние последнего триггера подключен к шине сигнала сброса. Источники информации, принятые во внимание при экспертизе 1,Заявка Великобритании № 1427993, кл. Q 11 С 19/00, опублик. 1973. 2.Патент Франции № 205О467, кл. 0 11 С 19/00, опубл. 197О. З.Авторское свидетельство СССР № 471679, кл. Н О4 F 13/08, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU1003145A1 |

| Буферное запоминающее устройство | 1977 |

|

SU763965A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1462421A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для измерения коэффициента пульсаций постоянного напряжения | 1989 |

|

SU1742644A1 |

| Логический анализатор | 1986 |

|

SU1363211A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Многоканальное запоминающее устройство | 1990 |

|

SU1805497A1 |

Авторы

Даты

1980-09-15—Публикация

1977-07-05—Подача