Изобретение относится к передаче дискретной информации, телеграфии и вычислительной технике и в частности к аппаратуре ввода-вывода данных и сопряжений узлов, обладающих разным быстродействием.

Известен асинхронный буферный накопитель, содержащий в каждой ступени два регистра запоминающих так- Q тируемых RS-триггеров и два нетактируемых RS-триггера управления 1.

Известен также синхронный электронный двоичный запоминающий и сдвиговый регистр, содержащий в каждом . каскаде запоминающую секцию на триггерах со схемами записи и управляющую секцию на триггере и четырех элементах совпадения 2.

Недостатком известных устройств 20 является сложность функционального выполнения.

Наиболее близким к изобретению по технической сущности является буферное запоминающее устройство, со- 25 держащее в каждой ступени регистр запоминающих D-триггеров, D-входы которых соединены с выходами соответствующих триггеров предыдущей ступени, а входы тактирования объедине-. 30

ны в шину записи, и управляющую, секцию, содержащую счетный триггер с установочным входом, элемент совпадения и элемент запрета с двумя прямь;ми и инверсным входом 3.

Недостатком этого устройства является сложность схемы, обусловленная применением элементов задержки -f счетных триггеров со сложной структурой в управляющей секции.

Цель изобретения - упрощение буферного запоминающего устройства.

Поставленная цель достигается тем, что в буферном запоминающем устройстве, содержащем регистры хранения первые входы которых соединены с информационными входами устройства, элементов совпадения, выходы которых подключены ко вторым входам регистров хранения, кроме первого регистра хранения, управляющие триггеры, шину записи, шину стирания, шину сигнала подтверждения записи и шину сброса, выхад каждого управляющего триггера соединен с первым входом данного элемента совпадения и вторым входом предыдущего элемента совпадения, выход каждого элемента совпадения подключен к первому входу данного управляющего триггера и к третьему входу предыдущего элемента совпадения, второй вход Кс1ждого управляющего триггера соединен с выходом предыдущего элемента совпадения и четвертым входом данного элемента совпадения, третий вход предпоследнего элемента совпадения и первый вход последнего управляющего триггера соединены с шиной стирания, выход последнего элемента совпадения соединен с шиной сигнала подтверждения записи, третий вход последнего управляющего триггера подсоединен к шине сброса, второй вход первого управляющего триггера соединен со входом первого элемента совпадения и с шиной записи.

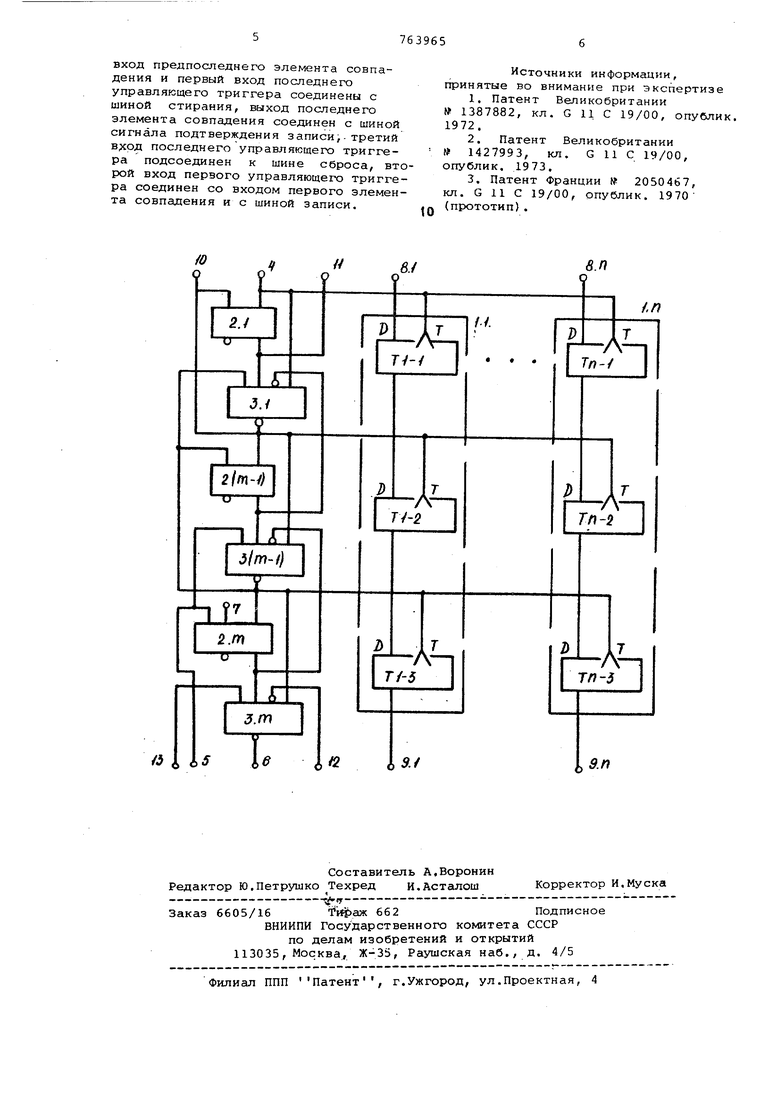

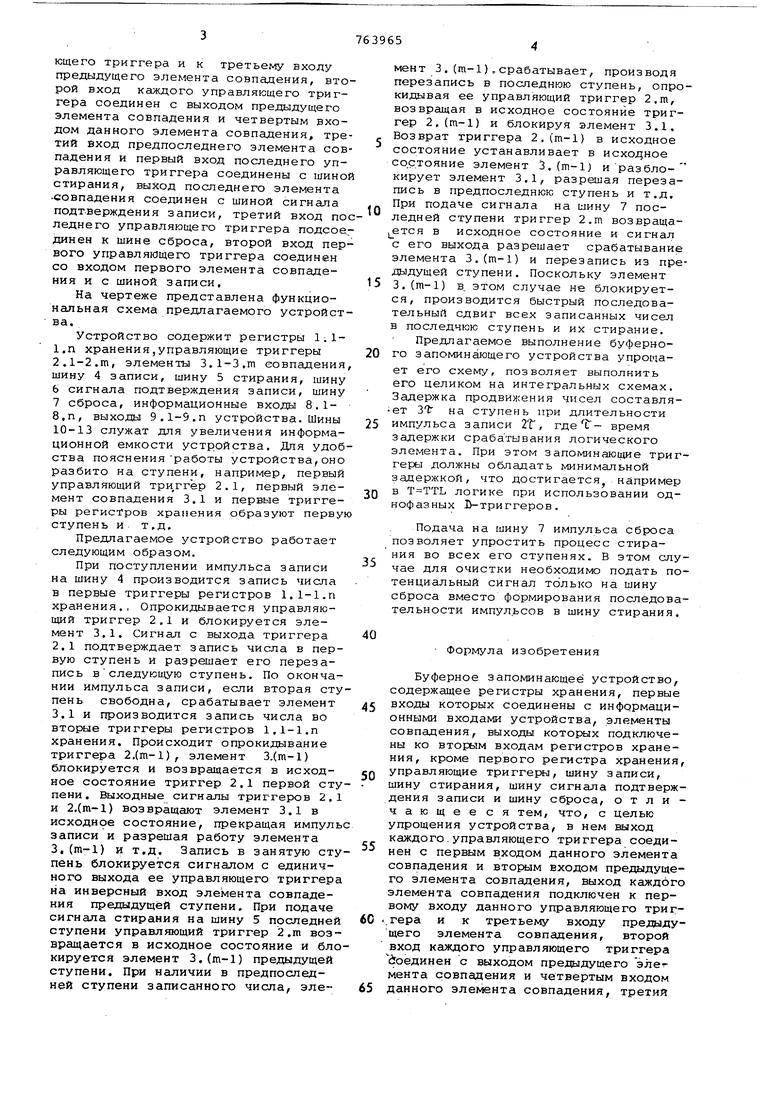

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит регистры 1.11,п хранения,управляющие триггеры 2.1-2.т, элементы 3.1-3.т совпадения, шину 4 записи, шину 5 стирания, шину

6сигнала подтверждения записи, шину

7сброса, информационные входы 8.18.П, выходы 9.1-9,п устройства. Шины 10-13 служат для увеличения информационной емкости устройства. Для удобства поясненияработы устройства,оно разбито на ступени, например, первый управляющий 2.1, первый элемент совпадения 3.1 и первые триггеры регистров хранения образуют первую ступень и т.д.

Предлагаемое устройство работает следующим образом.

При поступлении импульса записи на шину 4 производится запись числа в первые триггеры регистров l.l-l.n хранения., Опрокидывается управляющий триггер 2.1 и блокируется элемент 3.1. Сигнал с выхода триггера 2.1 подтверждает запись числа в первую ступень и разрешает его перезапись вследующую ступень. По окончании импульса записи, если вторая ступень свободна, срабатывает элемент 3.1 и производится запись числа во вторые триггеры регистров l.l-l.n хранения. Происходит опрокидывание триггера 2.(т-1), элемент 3.(т-1) блокируется и возвращается в исходное состояние триггер 2.1 первой ступени. Выходные сигналы триггеров 2.1 и 2.(т-1) возвращают элемент 3.1 в исходное состояние, прекращая импуль записи и разрешая работу элемента 3,(m-l) и т.д. Запись в занятую ступень блокируется сигналом с единичного выхода ее управляющего триггера на инверсный вход элемента совпадения предыдущей ступени. При подаче сигнала стирания на шину 5 последней ступени управляющий триггер 2.т возвращается в исходное состояние и блокируется элемент 3.{m-l) предыдущей ступени. При наличии в предпоследней ступени записанного числа, элемент 3.(m-l),срабатывает, производя перезапись в последнюю ступень, опрокидывая ее управляющий триггер 2.т, возвращая в исходное состояние триггер 2.(m-l) и блокируя элемент 3.1. Возврат триггера 2.(m-l) в исходное состояние устанавливает в исходное состояние элемент 3.(iTi-l) иразбло- кирует элемент 3.1, разрешая перезапись в предпоследнюю ступень и т.д. При подаче сигнала на шину 7 последней ступени триггер 2.ш возвраща ется в исходное состояние и сигнал с его выхода разрешает срабатывание элемента 3.(т-1) и перезапись из предыдущей ступени. Поскольку элемент

5 3.(т-1) в. этом случае не блокируется, производится быстрый последовательный сдвиг всех записанных чисел в последнюю ступень и их стирание. Предлагаемое выполнение буферно0 го запоминающего устройства упрощает его схему, позволяет выполнить его целиком на интегральных схемах. Задержка продвижения чисел составляет 3t на ступень при длительности

5 импульса записи 2t, где Т- время задержки срабатывания логического элемента. При этом запоминающие триггеры должны обладать IИHимaльнoй задержкой, что достигается например

Q в логике при использовании однофазных D-триггеров.

Подача на шину 7 импульса сброса позволяет упростить процесс стирания во всех его ступенях. В этом случае для очистки необходимо подать потенциальный сигнал только на шину сброса вместо формирования последовательности импульсов в шину стирания.

Формула изобретения

Буферное запоминающее устройство, содержащее регистры хранения, первые

входы которых соединены с информационными входами устройства, элементы совпадения, выходы которых подключены ко вторым входам регистров хранения, кроме первого регистра хранения,

управляющие триггеры, шину записи,

шину стирания, шину сигнала подтверждения записи и шину сброса, отличающее ся тем, что, с целью упрощения устройства, в нем выход каждого.управляющего триггера соедииен с первым входом данного элемента совпадения и вторым входом предыдущего элемента совпадения, выход каждого элемента совпадения подключен к первому входу данного управляющего триг, гера и к третьему входу предыдущего элемента совпадения, второй

вход каждого управляющего триггера

Соединен с выходом предыдущего эле мента совпадения и четвертым входом

данного элемента совпадения, третий

вход предпоследнего элемента совпадения и первый вход последнего управляющего триггера соединены с шиной стирания, выход последнего элемента совпадения соединен с шиной сигнала подтверждения записи,, третий ВХРД последнего управляющего триггера подсоединен к шине сброса, второй вход первого управляющего триггера соединен со входом первого элемента совпадения и с шиной записи.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании

№ 1387882, кл. G 11 С 19/00, опуСлик. 1972.

2.Патент Великобритании

tt 1427993, кл. G 11 С 19/00, опублик. 1973.

3.Патент Франции № 2050467, кл. G 11 С 19/00, опублик. 1970 (прототип).

o

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1981 |

|

SU1003145A1 |

| Буферное запоминающее устройство | 1977 |

|

SU763970A1 |

| Буферное запоминающее устройство | 1980 |

|

SU858109A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Сдвиговый регистр | 1983 |

|

SU1624528A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1462421A1 |

| Стековое запоминающее устройство | 1979 |

|

SU881863A1 |

| УСТРОЙСТВО для УСРЕДНЕНИЯ ВЫЗВАННЫХ ОТКЛИКОВ!,:k.-. | 1973 |

|

SU361461A1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1274002A1 |

Авторы

Даты

1980-09-15—Публикация

1977-07-11—Подача