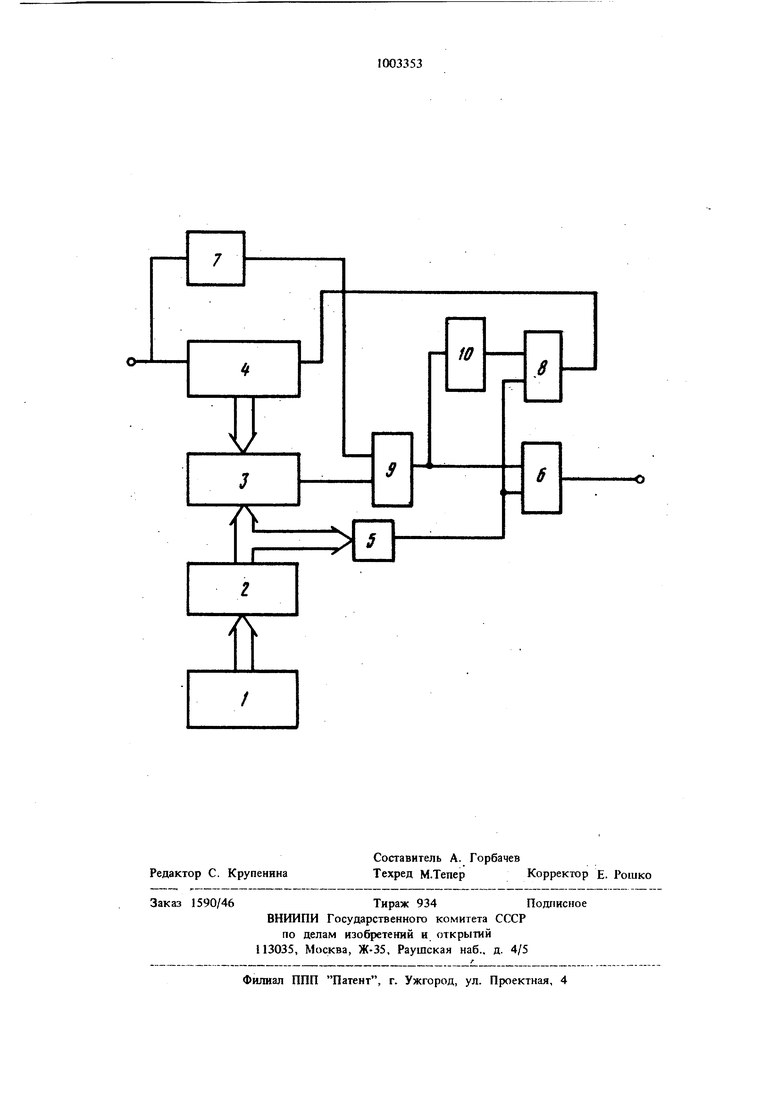

Изобретение относится к импульсной техни ке и может быть использовано, например, в цифровых, импульсных генераторах и синтезаторах частоты. Известен делитель частоты, содержащий блок управления, выходы которого подключены к входам запоминающего элемента, выходы которого соединены с первыми входами элемента сравнения кодов, вторые входы которого соединены с выходами счетчика импульсов, и элемент И 1. Недостатком указанного устройства является отсутствие неискаженной передачи длительности входных импульсов. Наиболее близким к предлагаемому является делитель частоты следования импульсов, содержащий блок управления, выходы которого подключены к входам запоминающего элемента, выходы которого соединены с первыми входами элемента сравнения кодов вторые входы которого соединены с выходами счетчика импульсов, дещифратор кода исходно го состояния, входы которого соединены с пе выми входами элемента сравнения кодов, - с первым входом первого элемента И, и элемент задержки 2. Недостатком устройства является отсутствие неискаженной передачи длительности импульсов. Цель изобретения обеспечение неискажён-. ной передачи длительности импульсов. Поставленная цель достигается тем, что в делитель частоты следования импульсов, содержащий блок управления, выходы которого подключены к входам запоминающего элемента, выходы которого соединены с первыми входами элемента сравнения кодов, вторые . входы которого соединены с выходами счетчика импульсов, дещифратор кода исходного состояния, входы которого соединены с первыми входами элемента сравнения кода выход с первым входом первого элемента ИЛИ, и элемент задержки, введены второй элемент ИЛИ, элемент И, элемент выделения заднего фронта импульса, выход которого соединен с первым входом второго элемента ИЛИ, вход с вторым входом первого элемента ИЛИ и I выходом элемента И, первый вход которого 3100 соединен с выходом элемента сравнения кода, второй вход через элемент задержки - со счетным входом счетчика нлтульсов, устано вочный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с первым входом первого элемента ИЛИ. На чертеже приведена структурная электрическая схема устройства. Устройство содержит блок 1 управления, элемент 2 запоминающий, элемент 3 сравнения кода, счетчик 4 импульсов, дешифратор 5 кода исходного состояния, первый элемент ИЛИ 6, элемент 7 задержки, второй элемент ИЛИ 8, .элемент И 9 и элемент 10 выделения эаднего фронта импульса. Устройство работает следующим образом. На ввдд счетчика 4 поступает последовательность импульсов, подлежащая делению. Поступление каждого импульса изменяет код счетчика 4 на единицу. В момент совпадения кодов на выходе счетчика 4 и установленного -в запоминающем элементе 2 на выходе элемен та 3 сравнения кодов воэникает потенциал, который поступает на первый вход элемента И 9. На второй вход этого элемента через элемент задержки с задержкой на время переходного процесса в счетчике 4 и элементе 3 сравнения поступает входной импульс. Длительность импульса на выходе элемента И 9 в момент совпадения кодов целиком определя ется величиной длительности входного сигнала В момент появления заднего среза импульса на выходе элемента И 9 сигнал с выхода элемента 10 формирования .заднего фронта им пульса череэ элемент ИЛИ 8 устанавливает счетчик 4 в начальное состояние. Далее весь цикл деления частоты повторяется. Таким образом, на выходе элемента ИЛИ 6 формируются импульсы, длительность которых равна длительности входных сигналов, а частота следования определяется частным от деления входной частоты на коэффициент деления,, установленный в блоке 1 управления Дещифратор 5 кода исходного состояния необходим для, того, чтобы при установке кода начального состояния в элементе 2 эапоминания на выходе деигафрато()а 5 и одновременно на выходе делителя частоты появлялся постоянный потенциал, свидетельствующий о невозможности деления частоты при равенстве начальных кодов счетчика и кода в элементе 2 запоминания. Этот уровень подтверждает начальное состояние кода счетчика 4 через второй элемент ИЛИ 8. В больщинстад случаев, когда начальные коды счетчика 4 и дешифратора 5 вь1бираются равными нулю и устанавливается код нуля в элементе 2 запоминания, на выходе делителя появляется сигиальный уровень, указывающий на невозможнобть деления частоты входных импульсов на нуль. Использование предлагаемой структуры делителя частоты позволяет сохранять длительность выходного импульса, равную длительности входного. Формула изобретения Делитель частоть след;ования импульсов, содержащий блок управления, выходы которого подклочены к входам запоминающего элемента, выходы которого соединены с первыми входами элемента сравнения кодов, вторые входы которого соединены с выходами счетчика импульсов, дещифратор кода исходного состояния, входы которого соединены с первыми входами элемента сравнения кодов, выход - с первым входом первого элемента ИЛИ, и элемент задержки, отличающийся тем, что, с целью обеспечения неискаженной передачи длительности импульсов, в него введены второй элемент ИЛИ, элемент И, элемент вьщеления заднего фронта импульса, выход которого соединен с первым входом второго элемента ИЛИ, вход - с вторым входом первого элемента ИЛИ и выходом элемента И, первый вход которого соединен с выходом элемента сравнения кода, второй вход череэ элемент задержки - со счетным входом счетчика импульсов, установочный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с первым входом первого элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Заявка Япониии N 51-37862, кл. 98(5) С 32, 30.12.71. 2.Авторское свидетельство СССР по заявке № 3331276/21, кл. Н 03 К 23/00, 20.08.81.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1981 |

|

SU1003354A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Устройство для задержки импульсов | 1986 |

|

SU1322437A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Формирователь управляющего сигнала для компенсации искажений типа "преобладание | 1989 |

|

SU1676109A2 |

| Функциональный генератор | 1979 |

|

SU794628A1 |

| Электростимулятор дыхания | 1990 |

|

SU1766421A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

Авторы

Даты

1983-03-07—Публикация

1981-08-20—Подача