1

Изобретение относится к мам автоматического управления и направлено на улучшение динамичёс- ; ких свойств систем при наличии периодических помех в первичных си1- налах.

Во многих системах автоматического управления технологическими процессами, например, горнотранспортного оборудования непрерывного действия VB частности карьерных роторных комплексов, рудоусреднительных машин, мельниц извлечения на обогатительных, фабриках и т.п. ) технолЬгические и конструктивные особенности оборудования вызывают периодические колебания параметров, по которым ведется управление в системе. При этом сигналы, получаемые в результате измерения таких параметров, содержат полезную для целей управления составляющую и периодическую помеху. Выделение полезных составляющих сигналов осуществляется в систе-,

мах управления при помощи различного рода устройств.

Известны устройства для фильтрации помех, основанные на принципе ограничения амплитуды периодической . помехи С 3Однако эти устройства не обеспечивают достаточной точности выделения полезной составляющей сигнала, так как при изменяющейся в процессе фильтрации частоте помехи .необходимо производить автоматическое изменение соответствующих параметров фильтра для того, чтобы точность фильтрации существенно не изменилась, а известные устройства такой адаптацией не обладают.

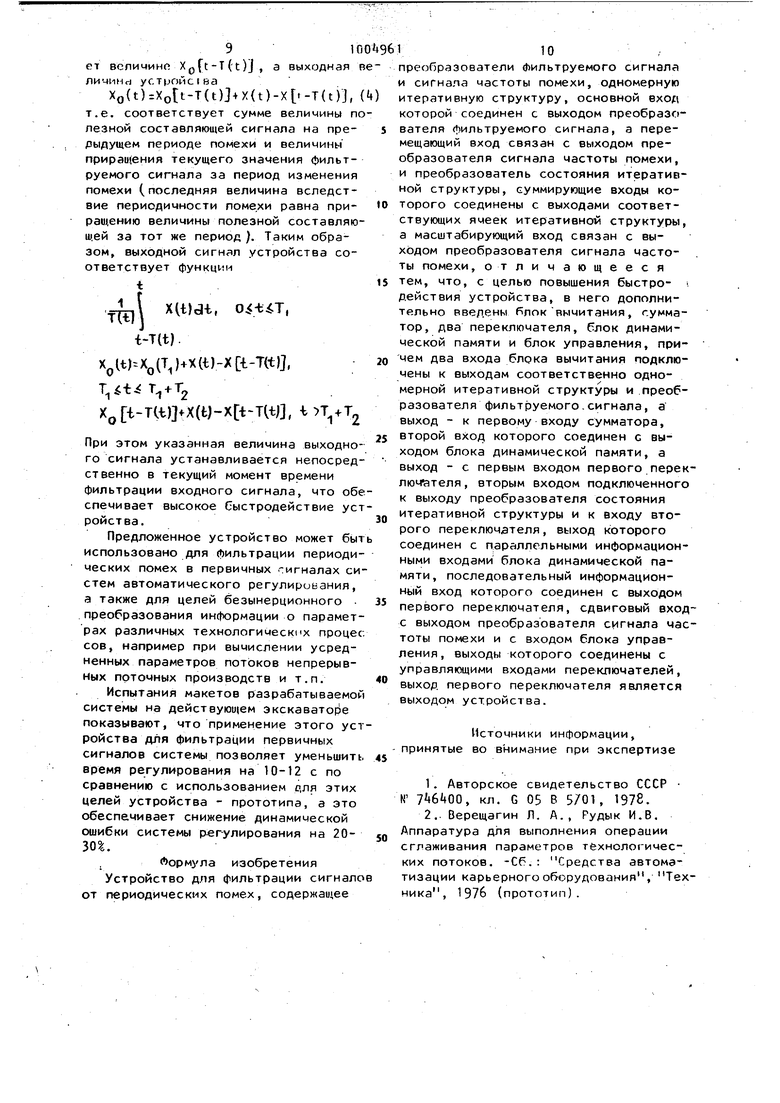

Недостатком указанных устройств, также является их низкое быстродействие при переходных процессах, что обусловлено наличием значительной постоянной времени в передаточной Функции устройства. Высокая точность фильтрации поме хи в широком диапазоне частот обеспечена в устройстве для фильтрации сигнала от периодических помех, дей ствие которого .основано на принципе скользящего интегрального усреднения величины фильтруемого сигнала. Наиболее близким к изобретению я ляется устройство, содержащее преобразователи фильтруемого сигнала и сигнала частоты помехи, выходы которых соединены соответственно с ос новным и перемещающим входами одномерной итеративной структуры, напри мер сдвигового регистра, и преобразователя состояния итеративной стру туры (сумматор состояний итеративной структуры и обратный преобразователь с соответствующей связью ду ними), суммирующие входы которого (входы сумматора состояний) соединены с соответствующими поразрядными выходами итеративной структуры, масштабирующий вход (вход обрат ного преобразователя) связан с выходом преобразователя сигнала .часTotu помехи, а выход ЯЁляется вь1ходом устройства 2. I, . Недостатком известного устройства является низкое быстродействие в переходных режимах, связанное с тем что постоянная времени фильтрации такого устройства равна величине периода помехи T(t) и при низких частотах помехи может быть значительной, что будет отрицательно сказыват ся на динамических свойствах системы автоматического; управления, в которой применяется устройство фильтрации.. . Цель изобретения - повышение быст родействия устройства фильтрации и, следовательно, уменьшение динамической ошибки системы. Указанная цель достигается тем, что в устройство для фильтрации си|- налов от периодических помех, содержащее преобразователи фильтруемого сигнала и сигнала частоты помехи, од номерную итеративную структуру, основной вход которой соединен с выходом пре:образователя фильтруемого сиг нала, а перемещающий вход связан с выходом преобразователя сигнала частоты помехи, и преобразователь состояния итеративной структуры, суммирующие входы которого соединены с вы ходами соответствующих ячеек итеративной структуры, а масштабирующий ВХОД связан с выходом преобразователя сигнала частоты помехи, введены блок вычитания, сумматор, два переключателя, блок динамической памяти и блок управления, причем два входа блока вычитания подключены к выходам соответственно одномерной итеративной структуры и преобразователя фильтруемого сигнала, а выход - к первому входу сумматора, второй вход которого соединен q выходом блока динамической памяти, а выход - с первым входом первого переключателя, вторым входом подключенного к ВЫХОДУ преобразователя состояния итеративной структуры и к входу второго переключателя, выход которого соединен с.параллельными информационными входами блока динамической памяти, последовательный информационный вход которого соединен с выходом первого переключателя, сдвиговый входс выходом преобразователя сигнала частоты помехи и с входом блока управления , выходы которого соединены с управляющими входами переключателей, выход первого переключателя является выходом устройства. Достижение поставленной цели обеспечивается путем определения текущего значения полезной составляющей фильтруемого сигнала как суммы этой величины, определенной на предыдущем периоде изменения помехи, и приращения текущего значения этой величины за период изменения помехи. При этом введение в устройство блока вычитания с соответствующими связями обеспечивает определение .величины приращения текущего значения полезной составляющей фильтруемого сигнала за период изменения помехи, введения блока динамической памяти, последовательный информационный вход которого связан с выходом устройства, а сдвиговый вход - с преобразователем сигнала частоты помехи, обеспечивает скользящее запоминание текущего значения полезной составляющей сигнала, получаемого на выходе устройства, на период, равный фактическому периоду изменения помехк, введение блока суммирования с соответствующими связями обеспечивает формирование сигнала суммы текущего знамения полезной составляющей фильтруемого сигнала, измеренного в предыдущий период изменения помехи и получаемого на выходе блока динамической памяти, и приращения величины полезной составляющей за период изменения помехи, сигнал которого формируется на выходе блока вычитания, введение двух управляемых пе реключателей и узла управления с соответствующими связями обеспечивает формирование начального значения сигнала осле запуска устройства. Таким образом, введение в устройство новых блоков и связей обеспечивает получение на выходе устройства текущего значения полезной составляющей фильтруемого сигнала непосредственно в момент измерения текущего зна . чения фильтруемого сигнала, а не чере период помехи, как в прототипе, т.е. приводит к повышению быстродействия устррйства фильтрации по сравнению с прототипом и, связанному с этим уменьшению динамкческой ошибки системы, в которой используется устройство фильт рации. На чертеже приведена блок-схема предложенного устройства для фильтрации сигнала от периодической помехи Устройство содержит преобразователи 1 и 2 фильтруемого-сигнала и сигнала ч.астоты помехи, одномерную итеративную структуру 3, основной вхо которой связан с выходом преобразователя 1, сдвиговый вход - с выходом преобразователя 2, а выходы всех ячеек структуры соединены с соответствующими суммирующими входами преобразователя t состояний итеративной стру туры, масштабирующий вход которого связан с выходом преобразоеателя 2 сигнала частоты помехи, блок 5 вычита ния, вход уменьшаемого которого соединен с выходом преобразователя 1 фильтруемого сигнала, а вход вычитаемого - с выходом последней ячейки ит ративной структуры 3, сумматор 6, пер вый вход которого связан с выходом блока 5 вычитания, блок 7 управления, вход которого соединен с выходом преобразователя 2 сигнала частоты помехи, переключатель 8, основные входы которого соединень соответственно с в выходом сумматора 6 и преобразователя А состояний итеративной структуры, уп равляющий вход соединен с одним из вы ходов блока 7 управления, а выход является выходом устройства, переключатель 9 основной вход которого связан с выходом преобразователя состояний итеративной структуры, а управ ляющий вход - с вторым выходом блока 7 управления, а также блок 10 динамической памяти, последовательнь Й информационный вход которого связан с выходом переключателя 8, параллельные Информационные входы соединены с выходом переключателя 9, сдвиговый-.вход соединен с выходом преобразователя 2 сигнала частоты помехи, а выход связан со вторым входом сумматора 6. Преобразователь k состояний итеративной структуры состоит из сумматора состояний итеративной структуры, выполненного, например, из весовых сопротивлений 11, подключенных к каждой ячейке итеративной структуры 3 и соединенных с суммирующим сопро-. тивлением 12, и обратного преобразователя, выполненного, например, в виде блока 13 умножения, Точка соединения сопротивлений 11 и 12 связана с одним из входов блока 13 умножения, второй вход которого соединен с выхо|Дом преобразователя 2 сигнала частоты помехи (этот вход является масшт.эбирующим входом преобразователя i/, а выход блока 13 является выходом преобразователя . При. работе устройства выходные токовые сигналь всех ячеек итеративной структуры-3, соответствующие распределению величины фильтруемого сигнала на интервале, равном периоду помехи, через одинаковые весовые сопротивления 11 , поступают на суммирующее сопротивление 12, При этом напряжение, снимаемое с сопротивления 12, пропорционально интегралу за период помехи от величины фильтруемого сигнала. Сигнал соответствующий этой величине, поступает на один вход блока 13 умножения, а на .второй вход последнего посЧупает сигнал с выхода преобразователя 2 сигнала частоты помехи, величина которого обратно пропорциональна периоду помехи. Таким образом, на выходе преобразователя 4 состояний итеративной структуры формируется сигнал величина которого соответствует среднему за период помехи интегральному значению фильтруемого сигнала. Одномерная итеративная структура 3 может быть выполнена, например, в виде многоразрядного сдвигового ре- гистра. Блок 7 управления ,может быть выполнен, например, в виде счетчика, выход которого подключен ко входу формирователя управляющих сигналов, содержащего, например, два триггера. Блок 10 динамической памяти может быть выполнен, например, аналогично одномерной итеративной структуре. Устройство работает следующим образом. - . Первичная информация фильтруемого сигнала и сигнала частоты периодической помехи с выхода преобразова телей 1 и 2 поступает соответственно на основной и перемещающий входы ите ративной структуры 3, в которой осуществляется распределение текущих величин фильтруемого сигнала на интервале, равном фактическому периоду помехи T(t), причем сигнал на выходе последней ячейки структуры 3 со ответствует величине фильтруемого сигнала в момент времени - T(t). В Преобразователе k состояния итератив ной структуры в текущий момент времени t осуществляется суммирование поступающих на его суммирующие входы сигналов состояния всех ячеек структуры 3 и умножение полученной суммы на величину частоты помехи, которая обратно пропорциональна периоду T(t) и сигнал которой поступает на вход масштабировании преобразователя с выхода преобразователя 2, т.е. на вы ходе преобразователя состояний итеративной структуры формируется сигнал величины Xo(t), определяемой выражением , . )d-t где T{t) - период помехи, изменяющийся в процессе фильтрации;Bx(t) величина входного фильтру емого сигнала; t - текущий момент времени. В исходном состоянии при включении устройства .на его выход через переключатель 8 подается выходной си нал преобразователя состояний итеративной структуры. Одновременно на вход блока 7 управления поступает импульсный сигнал с выхода преобразователя 2 сигнала частоты помехи и сче чик, ВХОДЯЩИЙ в состав блока 7, начинает отсчитывать импульсы этого сигна от момента включения устройства. Емкость счетмика подобрана так, что по окончании первого после включения уст РОИСТва периода помехи на выходе его плследнего разряда поярляется импульс запускающий формирователь управляющих сигналов, который при этом формирует и выдает на управляющий вход переключателя 9 импульс малой длительности, а по заднему фронту этого импульса формирует потенциальный сигнал, поступающий на управляющий вход переключателя 8. Первый из указанных управляющих сигналов переводит переключатель 9 в замкнутое состояние на время, достаточное для записи выходного сигнала преобразователя , поступающего при этом на параллельные входы всех ячеек блока 10 динамической памяти, а после записи переводит переключатель 9 в исходное разомкнутое состояние. Второй управляющий сигнал переводит, переключатель 8 в состояние, при котором на выход устройства подается выходной сигнал сумматора. На входы сум матора 6 поступают соответственно выходной сигнал блока 5 вычитания и выходной сигнал блока 10 динамической памяти. В блоке 5 вычитания при этом производится определение разности меж ДУ текущей величиной фильтруемого сигнала X(t), поступающего на вход уменьшаемого блока 5 с выхода преобразователя 1, и величиной фильтруемого сигнала, задержанного на период по мехи xCt-T(t) и поступающего на вход вычитаемого блока 5 с выхода последней ячейки итеративной структуры 3. Выходной сигнал блока 5 вь1читания соответствует, таким образом, величине приращения фильтруемого сигнала aX(t) за период помехи dl(t)X{t) t-T(t). В блоке 10 динамической памяти осуществляется запись информации, поступающей на последовательный информационный вход в первую ячейку, и последующий сдвиг этой информации в направлении к последней ячейке выходным сигналом преобразователя 2 сигнала частоты помехи, поступающим на сдвиговый вход блока 10 динамической памяти, в результате чего сигнал на выходе последней ячейки соответствует входной величине блока 10 динамической памяти, остается неизменным. При этом -выходной сигнал сумматора f являющийся выходным сигналом устройства, соответствует величине X(t)«Xo(T) +X{t)(t)J. (3) В дальнейшем (по окончании периода 12) выходной сигнал блока lb соотеегству9100ет величина Xpft-Т (t)J , а выходная в ли чип d устройс1ва Xo(t)Xott-T(t)3+x{t)-xt.-T(t)J, W т.е. соответствует сумме величины по лезной составляющей сигнала на прерыдущем периоде помехи и величины приращения текущего значения фильтруемого сигнала за период изменения помехи (последняя величина вследствие периодичности поме.хи равна приращению величины полезной составляющей за тот же период ). Таким образом, выходной сигнал устройства соответствует функции xuidi, , t-Tlt). (Ti), T,.t.T,T2 Xj,i-Ta)X(t)-X t-ntj, T + T2 При этом указанная величина выходного сигнала устанавливается непосредственно в текущий момент времени фильтрации входного сигнала, что обе спечивает высокое быстродействие уст ройства. Предложенное устройство может быт использовано для фильтрации периодических помех в первичных сигналах систем автоматического регулирования, а также для целей безынерционного .преобразования информации о параметрах различных технологических процес сов, например при вычислении усредненных параметров потоков непрерывных поточных производств и т.п. Испытания макетов разрабатываемой системы на действующем экскаваторе показывают, что применение этого уст ройства для фильтрации первичных сигналов системы позволяет уменьшить время регулирования на 10-12 с по сравнению с использованием для этих целей устройства - прототипа, а это обеспечивает снижение динамической ошибки системы регулирования на 2030%. . Формула изобретения Устройство для фильтрации сигнало от периодических помех, содержащее 10, преобразователи Фильтруемого сигнала и сигнала частоты помехи, одномерную итеративную структуру, основной вход которой соединен с выходом преобразователя фильтруемого сигнала, а перемещающий вход связан с выходом преобразователя сигнала частоты помехи, и преобразователь состояния итеративной структуры, суммирующие входы которого соединены с выходами соответствующих ячеек итеративной структуры, а масштабирующий вход связан с выходом преобразователя сигнала частоты помехи, отличающееся тем, что, с целью повышения быстро- . действия устройства, в него дополнительно ввел.ены блок вычитания , сумматор, два переключателя, блок динамической памяти и блок управления, причем два входа блока вычитания подключены к выходам соответственно одномерной итеративной структуры и .преобразователя фильтруемого.сигнала, а выход - к первому входу сумматора, второй вход которого соединен с выходом блока динамической памяти, а выход - с первым входом первого переключателя , вторым входом подключенного к выходу преобразователя состояния итеративной структуры и к входу второго переключателя, выход которого соединен с параллельными информационными входами блока динамической памяти, последовательный информационный вход которого соединен с выходом первого переключателя, сдвиговый входс выходом преобразователя сигнала частоты помехи и с входом блока управления , выходы которого соединены с управляющими входами переключателей, выход первого переключателя является выходом устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N , кл. G 05 В 5701, 1978. 2.. Верещагин Л. А., Рудык И.В. Аппаратура для выполнения операции сглаживания параметров технологических потоков. -Сб.: Средства автоматизации карьерного оборудования, Техника, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фильтрации сигналов от периодических помех | 1983 |

|

SU1148019A2 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

| Интегратор хроматографических данных | 1981 |

|

SU991443A1 |

| Устройство для программного управления | 1985 |

|

SU1249482A1 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

| ЦИФРОВОЕ УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ | 1974 |

|

SU1839793A1 |

| Способ подавления импульсных помех в видеосигнале изображения | 1989 |

|

SU1727210A1 |

| Устройство для измерения электромагнитных параметров объемных экранов | 1987 |

|

SU1583981A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

Авторы

Даты

1983-03-15—Публикация

1981-08-26—Подача