вымвходом второго регистра адреса и единичным входом второго триггера пуска, единичный и нулевой выходы которого соединены с третьим и четвертым входами блока запуска генератора тактовых импульсов соответственно, первый, второй и третий ВЫХОДЫблока запуска генератора тактовых импульсов соединены соответственно с первыми входами третьего и четвертого элементов:И и входом запуска-генератора тактовых импульсов, четвертый выход запуска генератора тактовых импульсов соединен с управляющими входайи первого и второгокоммутаторов состояний, выход которых соединен с единичными входами соответственно первого и второго триггеров состояний процессов, единичный выход первого триггера состояний-прессов соединен непосредственно с первыми управляющими входами коммутаторов логических условий и микроопераций, первым входом первого элемента ИЛИ, через первый элемент задержки - с первым инверсным управляющим входом первого коммутатора адреса и через второй элемент задержки - с вторым входом четвертого элемента И, единичный выход второго триггера состояний процессов соединен непосредственно с вторыми управляющими входами коммутаторов логических условий и микроопераций, вторым входом первого элемента ИЛИ и через третий элемент задержки - с вторым входом третьего элемента И, выход которого.соединен с первым прямым управляющим входом первого коммутатора адреса, первым информационным входом первого коммутатора состояний и через первый одновибратор - с первыми входами первого элемента И и второго элемента

ИЛИ, выход первой метки первого регистра микрокоманд соединен с вторым

управляющим входом первого коммутатора адреса, вторым входом первого элемента И .и первым входом пятого элемента И, выход которого соединен с вторым входом второго элемента ИПИ выход пятого элемента И соединен с первым входом третьего элемента ИЛИ, единичным входом третьего триггера состояний процессов, первым информационным входом второго коммутатора состояний и через второй одновибратор - с пятым входом блока запуска генератора токтовых импульсов, пер98520

выми входами второго элемента И и четвертого элемента ИЛИ, третьим входом второго элемента ИЛИ, выход которого соединен с входом синхронизации первого счетчика адреса, нулевые выходы первого и второго триггеров состояний процессов соединены с первыми входами соответственно шестого и седьмого элементов И, выход седьмого элемента И соединен с вторым входом третьего элемента ИЛИ, единичным входом четвертого триггера состояний процессов, вторым информационным входом первого коммутатора состояний, через третий одновибратор - с четвертым входом второго элемента ИЛИ . и вторым входом четвертого элемента ИЛИ, выход третьего элемента ИЛИ соединен с третьимуправляющим входом первого и первым управляющим входом второг.о коммутаторов адреса, выход пятого элементам ИЛИ соединен с первым входом восьмого элемента И. и нулевыми входами первого и второго ; триггеров состояний, единичный выход которого через четвертый элемент задержки соединен с четвертым инверсным управляющим входом первого коммутатора состояний, выходы второй метки и кода логических условий первого регистра микрокоманд соединены соответственно с первым входом пятого элемента ИЛИ и управляющим входом первого мультиплексора, выход которого соединен с вторым входом пятого элемента ИЛИ, выход первой метки второго регистра микрокоманд соединен с вторым управляющим входом второго коммутатора адреса, вторым входом второго и пер-« вым входом девятого элементов И, выход которого соединен с третьим входом четвертого элемента ИЛИ, выход которого соединен с входом синхронизации второго счетчика адреса, выход первого элемента ИЛИ соединен с первым входом десятого элемента И и вторым входом восьмого элемента И, выход которого соединен с третьим входом первого элемента И, выход второго регистра адреса соединен с четвертым информационным входом первого коммутатора адреса, выход четвертого элемента И соединен с четвертым прямым управляющим входом первого коммутатора адреса, вторым информационным входом второго коммутатора состояний, через четвертый одновибратор - с пятым входом второго элемента ИЛИ и четвертым входом.

первого элемента И, первый выход генератора тактовых импульсов соединен с пятым входом первого , третьим входом второго, вторыми входами пятого и девятого элементов И, выходы второй метки и кода логических условий второго, регистра микрокоманд соединены соответственно с первьш входом шестого элемента ИЛИ и управляющим входом второго мультиплексора, выход которого соединен с вторым входом шестого элемента ИЛИ, выход шестого элемента ИЛИ соединен с нулевыми входами третьего и четвертбго триггеров сое тояний процессов и первыми входами одиннадцатого и двенадцатого элемен тов И, единичный выход четвертого триггера состояний процессов соединен с вторым входом седьмого элемен та ИЛИ и четвертыми управляющими входами коммутатора логических усло ВИЙ и коммутатора микроопераций, первый и второй выхода конца процессов коммутатора микроопераций соединены с нулевыми входами соответственно первого триггера пуска и первого регистра адреса, второй выход генератора тактовых импульсов соединен с вторыми входами десятого

198520

и двенадцатого элементов И, выходы которых соединены с входами синхрониэации соответственно первого и второго регистров микрокоманд, первый и второй ВХОДЫ логических условий устройства соединены соответственно с первым и вторым информационными входами коммутатора логических условий, первый и второй выходы первой группы выходов которого соединены с информационными входами первого и второго мультиплексоров соответственно, нулевые выходы третьего и четвертого триггеров состояний соединены с вторыми входами соответственно шестого и седьмого элементов И, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора микроопераций, вторая группа выходов которого является второй группой выходов микроопераций устройства, первый и второй управляющие выходы второйгруппы выходов коммутатора микроопераций соединены с нулевым входом второго триггера пуска и входом сброса вто,рого регистра адреса соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

УСТРОЙСТВО ДОЯ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ,содержащее первый и второй блоки постоянной памяти, первый и второй регистры адреса, первый и второй счетчики адреса, первый и второй регистры микрокоманд, первый и второй триггеры пуска, коммутатор микроопераций, первый и второй коммутаторы адреса,, первый и второй элементы И, причем первый и второй входы кода операций устройства соединены с информационнымк входами первого и второго регистров адреса соответственно, выход первого регистра адреса соединен с первым информационным входом первого коммутатора.адреса, выход которого соединен с информационным входом первого счетчика адреса, выход элемента И соединен со счетным входом первого счетчика адреса, выход которого соединен с адресным входом первого блока постоянной памяти, выход адреса первого регистра микрокоманд соединен с первым информационным входом второго коммутатора адреса и вторым информационным входом первого коммутатора адресд, выход адреса второго регистра микрокоманд соединен с третьим информационным входом первого коммутатора адреса и вторым информационным входом второго коммутатора адреса, выход которого соединен с информационным входом второго счетчика адреса, вьрсод второго элемента И соединен со счетным входо.м второго счетчика адреса, выход которого соединен с адресным входом второго блока постоянной памяти, информационные выходы первого и второго блоков постоянной памяти соединены с информационными входами соответственно первого и второго регистров микрокоманд, первая группа выходов коммутатора микроопераций является первой группой выходов микроопераций устройства, отличающееся тем, что, с целью повьппения быстродействия, в устройство введены блок запуска генератора тактовых импульсов, коммутатор логических усФ ловий, первый и второй мультиплексо х ры, первый, второй, третий и четверел iNd тый триггеры состояния процессов, первь1й и второй коммутаторы состояний, генератор тактовых импульсов, десять элементов И, семь элементов ИЛИ, четыре одновибратора, четыре элемента задержки, причем первый вход пуска устройстйа соединен с тактовым входом первого регистра адреса и единичным входом первого триг гера пуска, единичный и нулевой выходы которого соединены с первым и вторым входами блока запуска генератора соответственно, второй вход пуска устройства соединен с такто

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных и управляющих устройств и систем

Цель изобретения - повьппение быстродействия устройства.

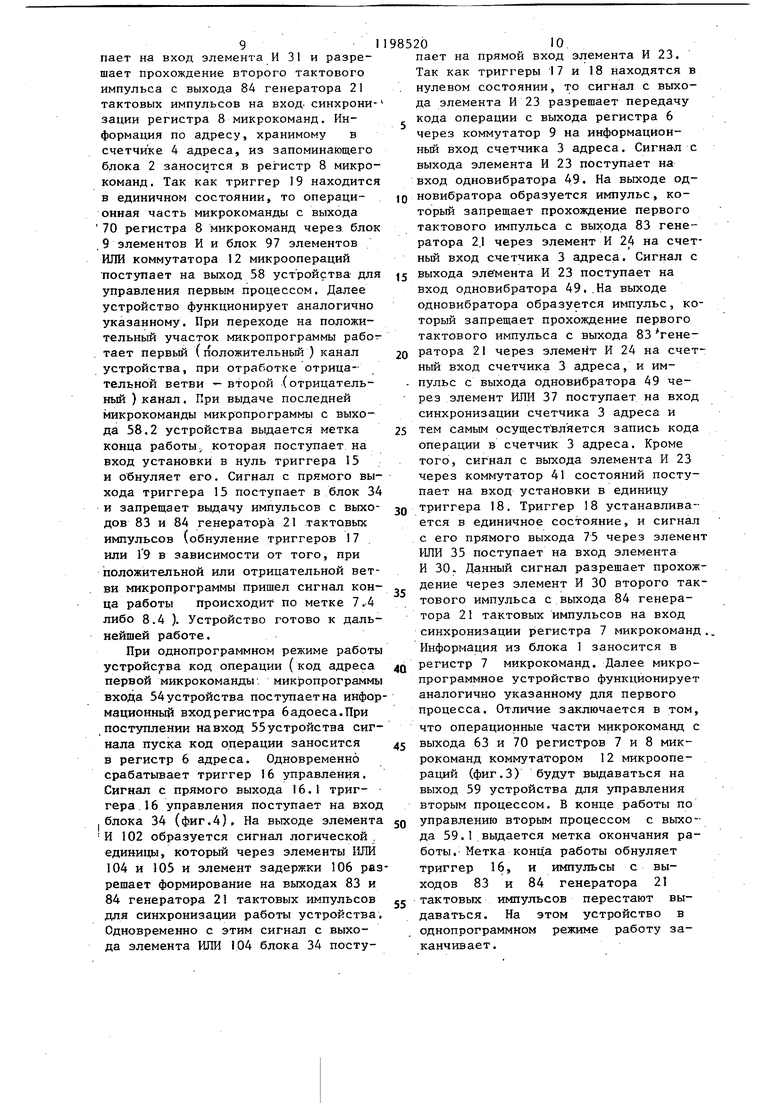

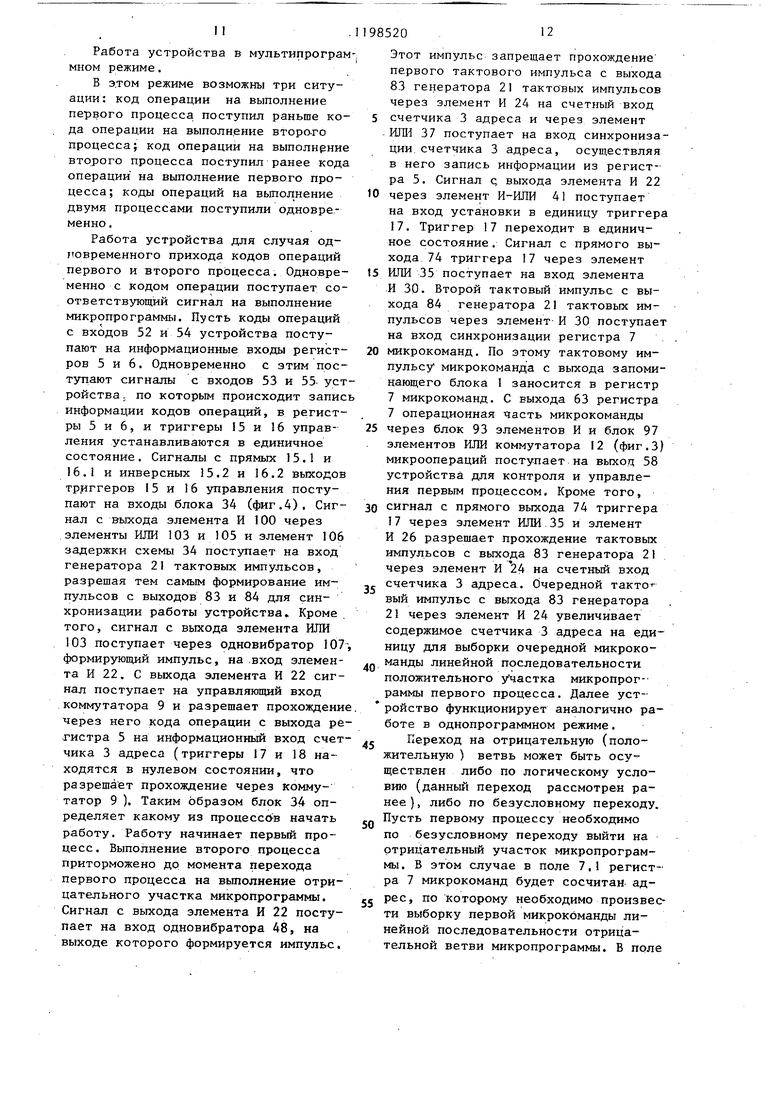

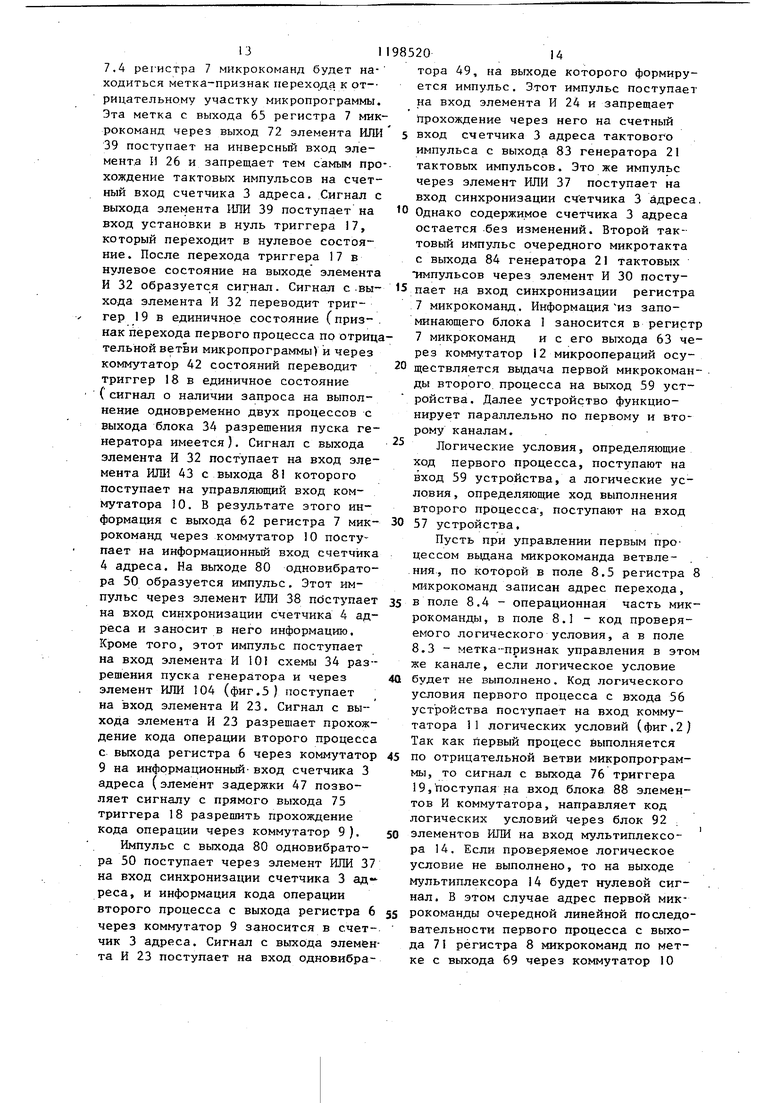

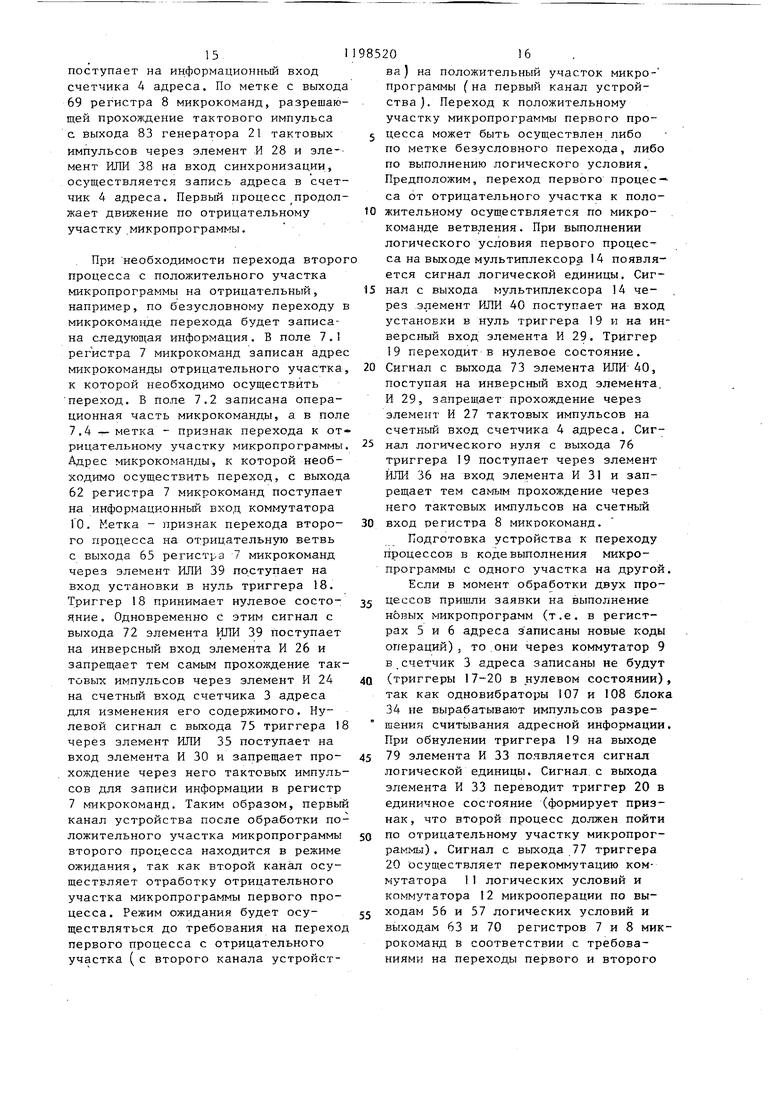

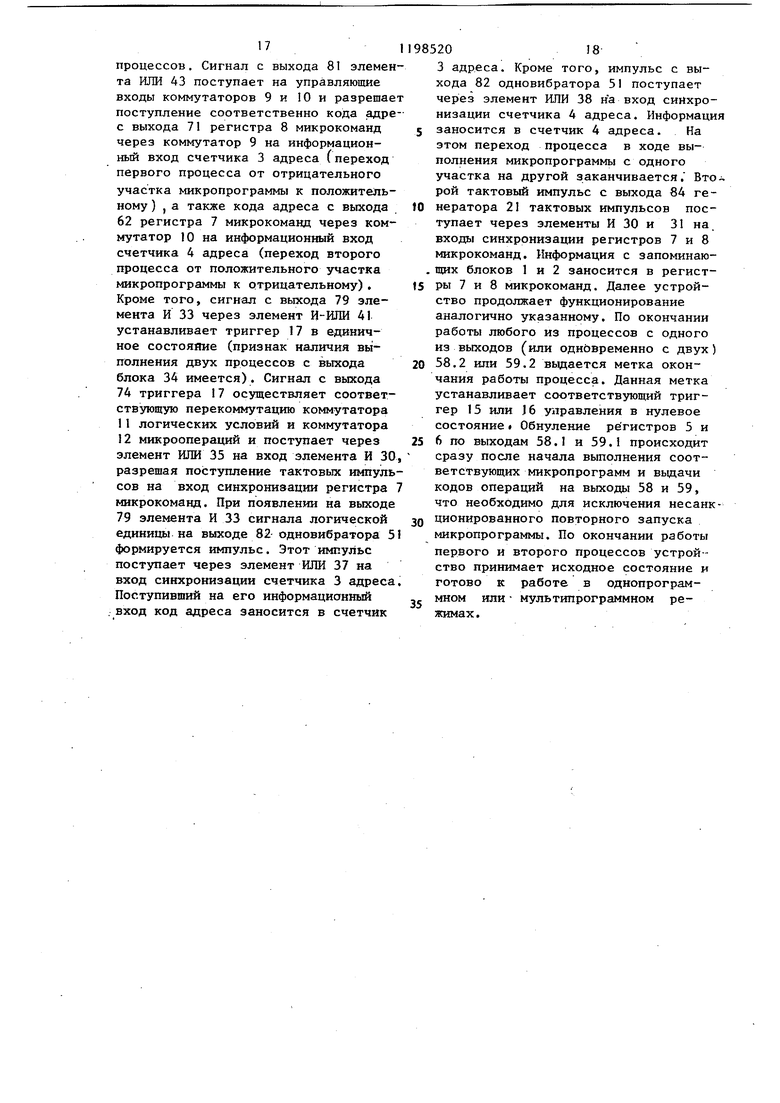

На фиг,1 приведена функциональная схема устройства, на фиг.2-4 - функциональные схемы коммутатора логических условий, коммутатора микроопераций и схемы разрешения пуска генера-тора соответственно.

Устройство (фиг.I) содержит первый и второй 2 блоки постоянной памяти, первый 3 и второй 4 счетчики адреса, первый 5 и второй 6 регистры адреса, первый 7 и второй 8 регистры микрокоманд с полями адреса 7.1 и 8.5 меток и логических условий 7.5 и 8,1 соответственно, первый 9 и второй

10 коммутаторы адреса, коммутаторы логических условий 1I и микроопераций 12, первый 13 и второй 14 мультиплексоры, первый 15 и второй 16 триггеры пуска с единичным 15.1 (16.1) и . . нулевым 15.2 (16.2) выходами, первыйчетвертьш 17-20 триггеры состояния процессов, генератор 21 тактовых импульсов, третий 22, четвертьй 23,

первый 24, пятый 25, восьмой 26, второй 27, девятый 28, одиннадцатый 29, десятый 30, двенадцатый 31, шестой 32 и седьмой 33 элементы И, блок 34 запуска генератора тактовых импульсов, первый 35, седьмсЙ 36, второй 37, четвертый 38,пятый 39 и шестой 40 элементы ИЛИ, первый 41 и второй 42 коммутаторы состояний, третий элемент ИЛИ 43, третий 44, первый 45,

второй 46 и четвертьй 47 элементы задержки, . первый 48, четвертый 49,

3

второй 50 и третий 51 одновибраторы, первые входы кода операции 52 и пуска 53 устройства, вторые входы кода операции 54 и пуска 55 устройства, первый 56 и второй 57 входы кода логических условий, первый 58 и второй 59 выходы устройства, первый 58.1 (59.1) и второй 58.2 (59.2) управляющие выходы первого (второго ) выхода коммутатора микроопераций, первый 60 и второй 61 выходыкоммутатора логических; условий, выходы адреса 62, микроопераций 63, первой 64 и второй 65 меток и кода логических условий 66 первого регистра микрокоманд, выхода кода логических условий 67,.второй 68 и первой 69 меток, микроопераций 70 и адреса 71 второго регистра микрокоманд, выходы пятого 72 и шестого 73 элементов ИЛИ, единичные выходы первого - четвертого 74-77 триггеров состояний процессов, выходы шестого 78 и седьмого 79 элементов И, выходы второго одновибратора 80, третьих элементов ИЛИ 81 и одновибратора 82, первый 83 и второй 84 выходы генератора 21 тактовых импульсов, выходы третьего 85 и четвертого 86 элементов И.

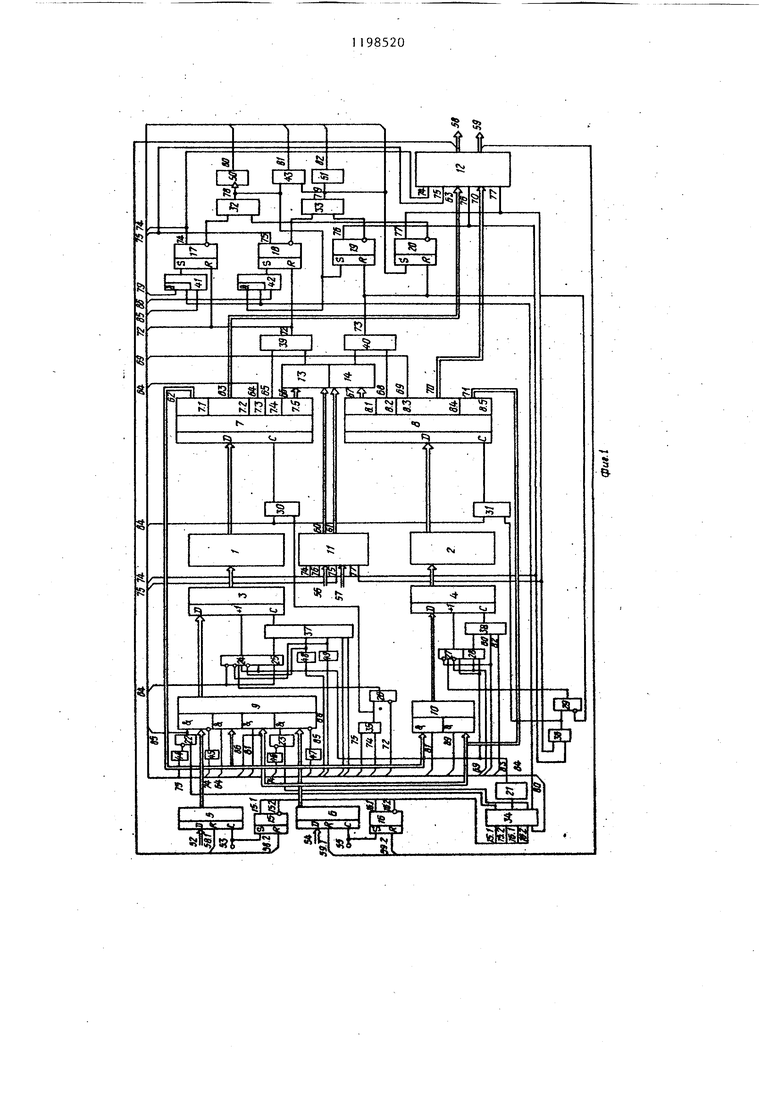

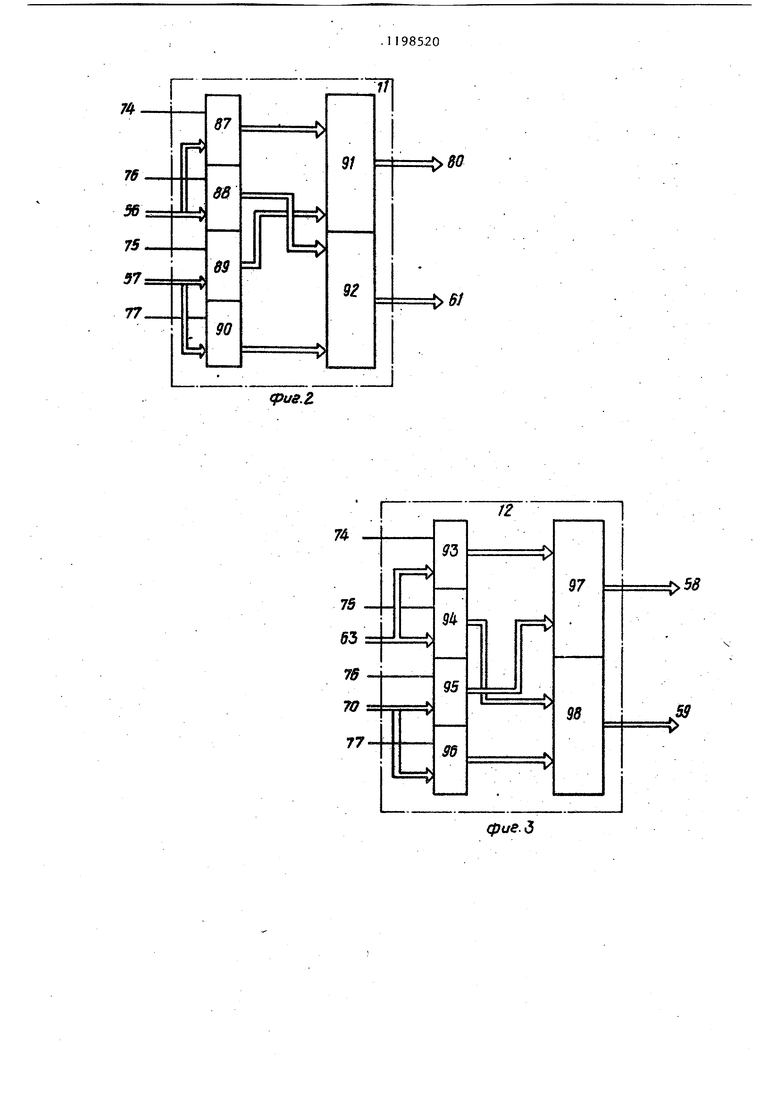

Коммутатор логических условий (фиг.2) содержит первый - четвертый 87-90 блоки элементов И, первый 91 и второй 92 блоки элементов ИЛИ. Коммутатор микроопераций (фиг.З) содержит первый - четвертый 93 - 96 блоки элементов И, первый 97 и второй 98 блоки элементов ИЛИ.

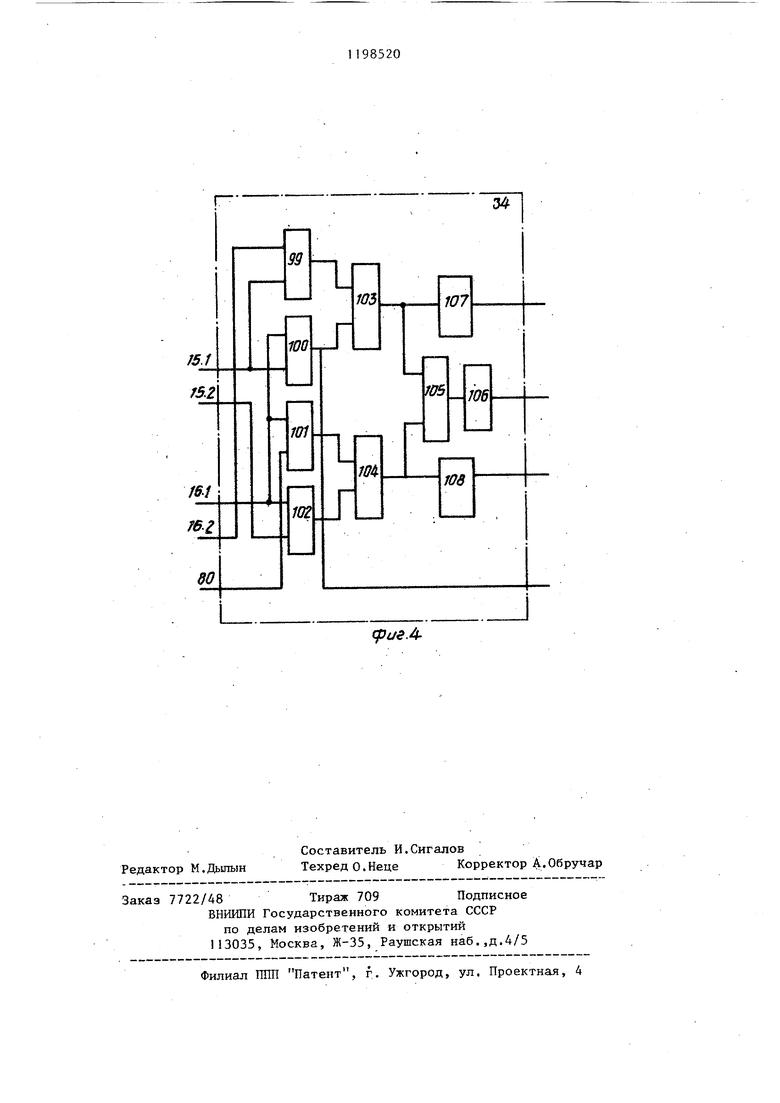

Схема разрешения пуска генератора (фиг.4) содержит первый 99, второй 100, четвертый 101 и третий 102 элементы И, первый - третий 103.105 элементы ИЛИ, элемент 106 задержки, первый 107 и второй 108 одновибраторы.

Блоки 1 и 2 постоянной памяти предназначены для хранения положительных и отрицательных участков микропрограмм соответственно.

Регистры микрокоманд 7 и 8 служат для хранения кодов считываемых микрокоманд и содержат адресное (7.1, 8,5), операционное (7.2, 8.4) поля и поле кода логических условий (7.5, 8.1). Кроме того, эти регистры имеют два разряда первой и второй меток Ml и М2 (поля 7,3, 8.3 и 7.4, 8,2 соответственно), причем , если осуществляется безусловньй переход в данном запоми85204

нающем блоке к однотипному участку микропрограмм, , в противном случае; , если осуществляется безусловный переход к другому запоминающему блоку (участку с противоположной полярностью ); в противном случае.

Регистры 5 и 6 адреса предназначены для записи и хранения начального адреса (кода операции).

Счетчики 3 и 4 адреса служат для формирования и хранения адресов очередных микрокоманд, считываемых из . запоминающих блоков 1 и 2.

Коммутаторы адреса 9 и 10 используются для коммутации адресных цепей положительного и отрицательного каналов устройства. Коммутатор II логических условий предназначен для

2Q коммутации сигналов логических условий ,- поступающих от объектов управления, в зависимости от трго, в каком из каналов реализуется соответствующий процесс, Коммутатор 12

25 микроопераций используется для коммутации сигналов микроопераций, поступающих от регистров микрокоманд на соответствующий объект управления (выходы 58 и 59). Мультиплексоры 13 и 14 предназначены для выделения значения проверяемого логического условия в соответствии с кодом логических условий. Триггеры 15 и 16 предназначены для запоминания сигналов пуска соответствующих процессов,

5 поступающих на входы 53 и 55 устройства. Триггеры 17-20 осуществляют запоминание местоположения процессов в каналах, причем триггеры 17 (18) и 19(20) устанавливаются в едидиничное состояние, если первым (вторым) процессором реализуются положительный и отрицательный участки микропрограмм соответственно. Генератор 21 тактовых импульсов

предназначен для синхронизации работы устройства. По импульсу на выходе 83 осуществляется запись информации в счетчики 3 и 4, а по импульсу на выходе 84 - занесение информации в регистры 7 и 8.

Коммутаторы состояний 41 и 43 служат дпя управления установкой в единицу триггеров 17 и 18, т.е. разрешением захвата процессами

5 положительного канала.

Элементы ИЛИ 39 и 40 предназначены дпя формирования сигналов перехода процессов к участку микропрограммы противоположной полярности. Элементы И 32 и 33, ИЛИ 43 и одновибраторы 50 и 51 используются для анализа состояния триггеров 17 20 и формирования управляющих сигналов в соответствии с их состоянием. Элементы И 24, 25 и 26, ИЛИ 35 и 37 и одновибраторы 48 и 49 предназначены Для управления счетом и записью информации в счетчик 3, Элементы И 27, 28 и 29 и ИЛИ 36 и 38 используются для управления записью и счетом информации в счет те 4. Элементы И 30 и 31 служат для управления записью информации в регистре 7 и 8. Элементы И 22 и 23 и элементы 44-47 задержки, предназначены для формирования управляющих сигналов на первый коммутатор 9 адреса Схема 34 (фиг.4) разрешения пуска генератора необходима для управления передачей кодов операций из регистров 5 и 6 в счетчик 3, пуском генератора 21 и управления коммутаторами 41 и 42. Работа устройства осуществляется следуннцим образом. Работа устройства возможна в сле дующих режимах: однопрограммном (уп равление одним процессором или конт роль одного объекта) и мультипрограммном (управление двумя процессорами или контроль двух идентичных объектов). В однопрограммном режиме работы устройства может выполняться либо последовательно одна микропрограмм за другой, либо параллельно с вьтол нением одной может начаться выполне ние другой микропрограммы по управлению одним и тем же процессом (контролю объекта) . В мультипрограммном режиме работы устройства вьтолняются две программы для двух различных объектов управления и контроля. ; При последовательном выполнении программы устройство работает следу щим образом. В исходном положении элементы памяти устройства находятся в нулев состоянии. Первый код операции про раммы (код адреса первой микрокоманды микропрограммы) поступает на информационный вход 32 регистра 5 адреса. При поступлении на вход 53 устройства сигнала на начало работы срабатывает (переходит в единичиое состояние) триггер 15 управления. Сигнал с прямого выхода триггера 15 через блок 34 запуска генератора поступает на управляющий вход генератора 21 тактовых импульсов и разрешает тем самым генерацию импульсов с выходов 83 и 84 генератора 21 для синхронизации работы устройства.Триггер 18 находится в нулевом состоянии. Поэтому сигнал с его прямого выхода через элемент 44 задержки и инверсный вход элемента И 22 разрешает прохождение кода операции с выхода регистра 5 через коммутатор 9 на информационный вход счетчика 3 адреса. Ка выходе элемента И 22 формируется сигнал разрешения прохождения операции через коммутатор 9. Одновременно этот сигнал поступает на вход одновибратора 48, на выходе которого формируется импульс. Импульс с выхода одновибратора 48 через элемент ИЛИ 37 поступает на вход синхронизации счетчика 3 адреса. По заднему фронту поступившего импульса код адреса первой микропрограммы заносится в счетчик 3 адреса. По поступившему в счетчик 3 адресу начинается выборка информации из запоминающего блока 1. Сигнал с выхода элемента И 22 через элемент ИЛ{ 41 поступает на вход установки в единицу триггера 17 и устанавливает его вединичное состояние. Триггер 17 является флажковым (признаковым ) триггером, характеризующим выполнение первого процессора по положительному участку микропрограммы. Сигнал с прямого выхода триггера 17 поступает на вход 74 коммутатора I2 микроопераций (фиг.З ) подготавливая его к прохождению микроопераций на выходе 58 устройства. Сигнал с прямого выхода триггера 17 поступает через элемент.ИЛИ 35 на вход элемента И 30 и разрешает прохождение второго тактового импульса с выхода 84 генератора 21 на вход синхронизации регистра 7 микрокоманд . Информация из блока 1 заносится в регистр 7 микрокоманд. Операционная часть микрокоманды с поля 7.2 регистра 7 поступает (фиг.З ) на вход 63 коммутатора 12 и через блок 93 элементов И к блоку 97 элементов ИЛИ поступает на выход 58 устройства для управлеиия про7цессом, например операционным блоком процессора.

Очередной тактовый импульс с выхода 83 генератора 21 тактовых импульсов поступает через элемент И 24 на счетный вход счетчика 3 адреса и увеличивает его содержимое на единицу (сигналы на выходах одновибраторов 48 и 49 отсутствуют, что разрешает прохождение тактового импульса через злемент И 24 ). По сформированному адресу на счетчике 3 адреса производится выборка из запоминающего блока 1, Второй тактовый импульс с выхода 84 генератора 21 тактовых импульсов поступает через злемент И 30 на вход синхронизации регистра 7 микрокоманд и заносит в него информацию с запоминающего блока 1. Информация с выхода 63 регистра 7 микрокомайд через коммутатор 12 микроопераций поступает на выход 58 устройства. Аналогичным образом ni3oисходит выдача микрокоманд линейной последовательности.

При выдаче микрокоманды ветвления в регистре 7 микрокоманд в поле 7.1 записан адрес первой микрокоманды очередной линейной последователь ности. В цоле 7.2 регистра 7 записана операционная часть микрокоманды, в поле 7.5 - код проверяемого логического условия. Код логического условия первого процесса поступает на вход 56 коммутатора 1I логических условий (фиг.2).Так как триггер 17 находится в единичном состоянии то сигнал с его прямого 74 разрешает прохождение кода логических условий через блок 87 элементов И и блок 91 элементов ИЛИ на выход 60 коммутатора 11 логических условий и с него на вход мультиплексора 13 логических условий,

Мультиплексор 13(14) логических условий обеспечивает коммутацию каналов.

При истинности логического условия устройство переходит на функционирование по другому каналу, т.е. на реализацию отрицательной ветви микропрограммы, если логическое условие ложно, то устройство функционирует в первом канале (реализует положительную ветвь микропрограмм ). В микрокоманде ветвления в поле 7.3 регистра 7 микрокоманд имеется метка, которая поступает на управляющи вход коммутатора 9 и разрешает про85208

хождение кода адреса с поля 7.1 регистра 7 микрокоманд на информационный вход счетчика 3 адреса. Метка с выхода 64 регистра 7 микрокоманд

г поступает на вход элемента К 24 и вход элемента И 25 и тем самым запрещает прохождение первого тактового импульса через элемент И 24 на счетный вход счетчика 3 адреса и разре0 щает прохождение первого тактового импульса через элемент И 25 и эле. мент ИЛИ 37 на вход синхронизации счетчика 3 адреса. Очередной первый тактовый импульс поступает на вход

5 синхронизации счетчика 3 адреса, разрешает запись в него нового кода адреса микрокоманды очередной линейной последовательности. По второмутактовому импульсу происходит запись

Q информации из запоминающего блока 1 в регистр 7 микрокоманд, и устройство функционирует аналогично указанному .

При выдаче микрокоманды ветвления

5 и истинности логического условия сигнал с выхода мультиплексора 13 через элемент ИЛИ 39 поступает на вход установки в нуль триггера 17 и инверсный вход И 26. Сигнал с выхода элемента ИЛИ 39 запрещает прохождение тактовых импульсов на счетный вход счетчика 3 адреса и вход синхронизации регистра 7 микрокоманд. Тем самым осуществляется переход к функционированию устройства по второму

каналу (т.е. обработке отрицательной ветви микропрограммы ).

Триггер 17 переходит в нулевое состояние. На выходе элемента И 32 образуется сигнал логической единицы. По переднему фронту этого сигнала устанавливается в единицу триггер 19, указывающий на то, что.первый процесс идет по отрицательному участку микропрограммы. На выходе

одновибратора 50 образуется импульс, которьй через элемент ИЛИ 38 поступает на вход синхронизации счетчика 4 адреса. Кроме того, сигнал с выхода элемента И 32 через элемент

0 ИЛИ 43 поступает на управляющий вход коммутатора 10. Информация об адресе первой микрокоманды очередной линейной последовательности с выхода 62 регистра 7 микрокоманд через

5 коммутатор 10 заносится в счетчик 4 адреса.

Сигнал с прямого выхода 76 триггера 19 через элемент ИЛИ 36 посту91

пает на вход элемента И 31 и разре

шает прохождение второго тактового импульса с выхода 84 генератора 21 тактовых импульсов на вход- синхронизации регистра 8 микрокоманд. Информация по адресу, хранимому в счетчике 4 адреса, из запоминающего блока 2 заносится в регистр 8 микрокоманд . Так как триггер 9 находится в единичном состоянии, то операционная часть микрокоманды с выхода 70 регистра В микрокоманд через блок .9 элементов И и блок 97 элементов ИЛИ коммутатора 12 микроопераций поступает на выход 58 устройства для управления первым процессом, Далее устройство функционирует аналогично указанному. При переходе на положительный участок микропрограммы работает первый (положительный ) канал устройства, при отработке отрицательной ветви - второй (отрицательный ) канал. При выдаче последней микрокоманды микропрограммы с выхода 58.2 устройства выдается метка конца работы, которая поступает на вход установки в нуль триггера 15 и обнуляет его. Сигнал с прямого выхода триггера 15 поступает в блок 34 и запрещает выдачу импульсов с выходов 83 и 84 генератора 21 тактовых импульсов (обнуление триггеров 17 или Г9 в зависимости от того, при положительной или отрицательной ветви микропрограммы пришел сигнал конца работы происходит по метке 7.4 либо 8.4 ). Устройство готово к дальнейшей работе.

При однопрограммном режиме работы устройства код операции (код адреса первой микрокоманды-, микропрограммы входа 54устройства постзтаетна информационный входрегистра бадоеса.При поступлении на вход 55устройства сигнала пуска код операции заносится в регистр 6 адреса. Одновременно срабатывает триггер 16 управления. Сигнал с прямого выхода 16.1 триггера. 16 управления поступает на вход блока 34 (фнг.4). На выходе элемента И 102 образуется сигнал логической . единшда, который через элементы ИЛИ 104 и 105 и элемент задержки 106 разрещает формирование на выходах 83 и 84 генератора 21 тактовых импульсов для синхронизации работы устройства. Одновременно с этим сигнал с выхода элемента ИЛИ 104 блока 34 посту852010

пает на прямой вход элемента И 23.

Так как триггеры 17 и 18 находятся в нулевом состоянии, то сигнал с выхода элемента И 23 разрешает передачу кода операции с выхода регистра 6 через коммутатор 9 на информационный вход счетчика 3 адреса. Сигнал с выхода элемента И 23 поступает на вход одновибратора 4:9. На выходе одO новибратора образуется импульс, который запрещает прохождение первого тактового импульса с выхода 83 генератора 2.1 через элемент И 24 на счетный вход счетчика 3 адреса. Сигнал с

5 выхода элемента И 23 поступает на вход одновибратора 49..На выходе одновибратора образуется импульс, который запрещает прохождение первого тактового импульса с выхода 83 генератора 21 через элемент И 24 на счетный вход счетчика 3 адреса, и им-пульс с выхода одновибратора 49 через элемент ИЛИ 37 поступает на вход синхронизации счетчика 3 адреса и

5 тем самым осуществляется запись кода операции в счетчик 3 адреса. Кроме того, сигнал с выхода элемента И 23 через комьгутатор 41 состояний поступает на вход установки в единицу

0 триггера 18. Триггер 18 устанавливается в единичное состояние, и сигнал с его прямого выхода 75 через элемент ИЛИ 35 поступает на вход элемента И 30. Данный сигнал разрешает прохождение через элемент И 30 второго тактового импульса с выхода 84 генератора 21 тактовых импульсов на вход синхронизации регистра 7 микрокоманд.. Информация из блока 1 заносится в

Q регистр 7 микрокоманд. Далее микропрограммное устройство функционирует аналогично указанному для первого процесса. Отличие заключается в том, что операционные части микрокоманд с

5 выхода 63 и 70 регистров 7 и 8 микрокоманд коммута тором 12 микроопераций (фиг.З) будут выдаваться на выход 59 устройства для управления вторым процессом. В конце работы по

0 управлению вторым процессом с выхода 59.1 выдается метка окончания работы .- Метка конца работы обнуляет триггер 16, и импульсы с выходов 83 и 84 генератора 21

5 тактовых импульсов перестают выдаваться. На этом устройство в однопрограммном режиме работу заканчивает.

Работа устройства в мультипрограммном режиме.

В Э.ТОМ режиме возможны три ситуации: код операции на выполнение первого процесса поступил раньше кода операции на выполнение второ-го процесса; код операции на выполнение второго процесса поступил ранее кода операции на выполнение первого процесса; коды операций на вьтолнение двумя процессами поступили одновременно .

Работа устройства для случая одновременного прихода кодов операций первого и второго процесса. Одновременно с кодом операции поступает соответствующий сигнал на выполнение микропрограммы. Пусть коды операций с входов 52 и 54 устройства поступают на информационные входы регистров 5 и 6, Одновременно с этим постуцают сигналы с входов 53 и 55- устройства; по которым происходит запис информации кодов операций, в регистры 5 и 6, и триггеры 15 и 16 управления устанавливаются в единичное состояние. Сигналы с прямых 15.1 и 16.1 и инверсных 15.2 и 16.2 выходов триггеров 15 и 16 управления поступают на входы блока 34 (фиг.4). Сигнал с выхода элемента И 100 через элементы ИЛИ 103 и 105 и элемент 106 задержки схемы 34 поступает на вход генератора 21 тактовых импульсов, разрешая тем самым формирование импульсов с выходов 83 и 84 для синхронизации работы устройства Кроме того, сигнал с выхода элемента ИЛИ 103 поступает через одновибратор 107 формирующий импульс, на .вход элемента И 22, С выхода элемента И 22 сигнал поступает на управляющий вход коммутатора 9 и разрешает прохождени Через него кода операции с выхода регистра 5 на информационный вход счетчика 3 адреса (триггеры 17 и 18 находятся в нулевом состоянии, что разрешает прохождение через коммутатор 9 ). Таким образом блок 34 определяет какому из процессО в начать работу. Работу начинает первьш процесс . Выполнение второго процесса приторможено до момента перехода первого процесса на вьтолнение отрицательного участка микропрограммы. Сигнал с выхода элемента И 22 поступает на вход одновибратора 48, на выходе которого формируется импульс.

Этот импульс запрещает прохождение первого тактового импульса с выхода 83 генератора 21 тактовых импульсов через элемент И 24 на счетный вход счетчика 3 адреса и через элемент ИЛИ 37 поступает на вход синхронизации счетчика 3 адреса, осуществляя в него запись информации из регистра 5. Сигнал с; выхода элемента И 22 через элемент И-ИЛИ 41 поступает на вход установки в единицу триггера 17. Триггер 17 переходит в единичное состояние. Сигнал с прямого выхода 74 триггера 17 через элемент ИЖ 35 поступает на вход элемента И 30. Второй тактовый импульс с выхода 84 генератора 21 тактовых импульсов через элемент И 30 поступает на вход синхронизации регистра 7 микрокоманд. По этому тактовому импульсу микрокоманда с выхода запоминающего блока 1 заносится в регистр 7 микрокоманд. С выхода 63 регистра 7 операционная часть микрокоманды через блок 93 элементов И и блок 97 элементов ИЛИ коммутатора 12 (фиг.З) микроопераций поступает на выход 58 устройства для контроля и управления первым процессом. Кроме того, сигнал с прямого выхода 74 триггера 17 через элемент ИЛИ 35 и элемент И 26 разрешает прохождение тактовых импульсов с выхода 83 генератора 21 через элемент И 24 на счетный вход счетчика 3 адреса. Очередной тактовый импульс с выхода 83 генератора 21 через элемент И 24 увеличивает содержимое счетчика 3 адреса на единицу для выборки очередной микрокоманды линейной последовательности положительного участка микропрограммы первого процесса. Далее устройство функционирует аналогично работе в однопрограммном режиме.

Переход на отрицательную (положительную ) ветвь может быть осуществлен либо по логическому условию (данньй переход рассмотрен ранее ), либо по безусловному переходу. Пусть первому процессу необходимо по безусловному переходу выйти на отрицательный участок микропрограммы. В этом случае в поле 7, регистра 7 микрокоманд будет сосчитан адрес, по которому необходимо произвести выборку первой микрокоманды линейной последовательности отрицательной ветви микропрограммы. В поле

131

Импульс с выхода 80 одновибратора 50 поступает через элемент ИЛИ 37 на вход синхронизации счетчика 3 ад« реса, и информация кода операции второго процесса с выхода регистра 6 через коммутатор 9 заносится в счетчик 3 адреса. Сигнал с выхода элемента И 23 поступает на вход одновибра852014

тора 49, на выходе которого формируется импульс. Этот импульс поступает на вход элемента И 24 и запрещает прохождение через него на счетный 5 вход счетчика 3 адреса тактового импульса с выхода 83 генератора 21 тактовых импульсов. Это же импульс через элемент ИЛИ 37 поступает на вход синхронизации счетчика 3 адреса.

О Однако содержимое счетчика 3 адреса остается -без изменений. Второй тактовый импульс очередного микротакта с выхода 84 генератора 21 тактовых импульсов через элемент И 30 поступает н.а вход синхронизации регистра 7 микрокоманд. Информацияиз запоминающего блока 1 заносится в регистр 7 микрокоманд и с его выхода 63 через коммутатор 12 микроопераций осуществляется выдача первой микрокоманды второго, процесса на выход 59 устройства. Далее устройство функционирует параллельно по первому и второму каналам.

Логические условия, определяющие ход первого процесса, поступают на вход 59 устройства, а логические условия , определяющие ход выполнения второго процесса-, поступают на вход

0 57 устройства.

Пусть при управлении первым процессом выдана микрокоманда ветвления, по которой в поле 8.5 регистра 8 микрокоманд записан адрес перехода,

5 в поле 8.4 - операционная часть микрокоманды, в поле 8.1 - код проверяемого логического условия, а в поле 8.3 - метка-признак управления в этом же канале, если логическое условие

Q будет не выполнено. Код логического условия первого процесса с входа 56 устройства поступает на вход коммутатора 11 логических условий (фиг.2) Так как первый процесс выполняется

5 по отрицательной ветви микропрограммы, то сигнал с выхода 76 триггера 19,поступая на вход блока 88 элементов И коммутатора, направляет код логических условий через блок 92

0 элементов ИЛИ на вход мультиплексора 14. Если проверяемое логическое условие не выполнено, то на выходе мультиплексора 14 будет нулевой сигнал. В этом случае адрес первой микрокоманды очередной линейной последовательности первого процесса с выхода 7I регистра 8 микрокоманд по метке с выхода 69 через коммутатор 10 1 5 поступает на информационный вход счетчика А адреса. По метке с выхода 69 регистра 8 микрокоманд, разрешаю щей прохождение тактового импульса с выхода 83 генератора 21 тактовых импульсов через элемент И 28 и элемент ИЛИ 38 на вход синхронизации, осуществляется запись адреса в счет чик 4 адреса. Первый процесс продол жает движение по отрицательному участку микропрограммы. При необходимости перехода второ процесса с положительного участка микропрограммы на отрицательный, например, по безусловному переходу микрокоманде перехода будет записана следующая информация. В поле 7.1 регистра 7 микрокоманд записан адре микрокоманды отрицательного участка к которой необходимо осуществить переход, В поле 7,2 записана операционная часть микрокоманды, а в пол 7.4 -г- метка - признак перехода к от рицательному участку микропрограммы Адрес микрокоманды, к которой необходимо осуществить переход, с выход 62 регистра 7 микрокоманд поступает на информационный вход коммутатора 10, Метка - признак перехода второго процесса на отрицательную ветвь с выхода 65 регистра 7 микрокоманд через элемент ИЛИ 39 поступает на вход установки в нуль триггера 18, Триггер 18 принимает нулевое состо яние. Одновременно С этим сигнал с выхода 72 элемента ИЛИ 39 поступает на инверсный вход элемента И 26 и запрещает тем самым прохождение тактовых импульсов через элемент И 24 на счетный вход счетчика 3 адреса для изменения его содержимого. Нулевой сигнал с выхода 75 триггера 18 через элемент ИЛИ 35 поступает на вход элемента И 30 и запрещает прохождение через него тактовых импульсов для записи информации в регистр 7 микрокоманд. Таким образом, первый канал устройства после обработки положительного участка микропрограммы второго процесса находится в режиме ожидания, так как второй канал осуществляет отработку отрицательного участка микропрограммы первого процесса. Режим ожидания будет осуществляться до требования на переход первого процесса с отрицательного участка ( с второго канала устройст20 6ва) на положительный участок микропрограммы (на первый канал устройства). Переход к положительному участку микропрограммы первого процесса может быть осуществлен либо по метке безусловного перехода, либо по вь полнению логического условия. Предположим, переход первого процес са от отрицательного участка к положительному осуществляется по микрокоманде ветвления, При вьтолнении логического условия первого процесса на выходе мультиплексора 14 появляется сигнал логической единицы, Сигнал с выхода мультиплексора 14 через элемент ИЛИ 40 поступает на вход установки в нуль триггера 19 и на инверсный вход элемента И 29. Триггер 19переходит в нулевое состояние, Сигнал с выхода 73 элемента ИЛИ 40, поступая на инверсный вход элемента. И 29, запрещает прохождение через элемент И 27 тактовых импульсов на счетный вход счетчика 4 адреса, Сигнал логического нуля с выхода 76 триггера 19 поступает через элемент ИЛИ 36 на вход элемента И 31 и запрещает тем самым прохождение через него тактовых импульсов на счетный вход регистра 8 микрокоманд. Подготовка устройства к переходу процессов в коде выполнения микропрограммы с одного участка на другой, Если в момент обработки двух процессов пришли заявки на выполнение новых микропрограмм (т,е, в регистрах 5 и 6 адреса записаны новые коды операций), то.они через коммутатор 9 в счетчик 3 адреса записаны не будут (триггеры 17-20 в нулевом состоянии), так как одновибраторы 107 и 108 блока 34 не вырабатывают импульсов разрешания считывания адресной информации. При обнулении триггера I9 на выходе 79 элемента И 33 появляется сигнал логической единицы. Сигнал с выхода элемента И 33 переводит триггер 20 в единичное состояние (формирует признак, что второй процесс должен пойти по отрицательному участку микропрограммы) . Сигнал с выхода 77 триггера 20осуществляет перекоммутацию коммутатора 11 логических условий и коммутатора I2 микрооперации по выходам 56 и 57 логических условий и выходам 63 и 70 регистров 7 и 8 микрокоманд в соответствии с требованиями на переходы первого и второго

71

процессов. Сигнал с выхода 81 элемента ИЛИ 43 поступает на управляющие входы коммутаторов 9 и 10 и разрешает поступление соответственно кода адре-с выхода 71 регистра 8 микрокоманд через коммутатор 9 на информационный вход счетчика 3 адреса (переход первого процесса от отрицательного участка микропрограммы к положительному ) , а также кода адреса с выхода 62 регистра 7 микрокоманд через комьсутатор 10 на информационный вход счетчика 4 адреса (переход второго процесса от положительного участка микропрограммы к отрицательному), Кроме того, сигнал с выхода 79 элемента И 33 через элемент И-ИПИ 41 устанавливает триггер 17 в единичное состояние (признак наличия выполнения двух процессов с выхода блока 34 имеется). Сигнал с выхода 74 триггера I7 осуществляет соответствующую перекоммутацию коммутатора

11логических условий и коммутатора

12микроопераций и поступает через элемент ИЛИ 35 на вход элемента И 30, разрешая поступление тактовых импульсов на вход синхронизации регистра 7 микрокоманд. При появлении на выходе 79 элемента И 33 сигнала логической единицы на выходе 82 одновибратора 51 формируется импульс. Этот импульс поступает через элемент ИЛИ 37 на вход синхронизации счетчика 3 адреса. Поступивший на его информационный

. вход код адреса заносится в счетчик

852018

3 адреса. Кроме того, импульс с выхода 82 одновибратора 51 поступает через элемент ИЛИ 38 на вход синхронизации счетчика 4 адреса. Информация

5 заносится в счетчик 4 адреса. На этом переход процесса в ходе выполнения микропрограммы с одного участка на другой заканчивается. Вто рой тактовый импульс с выхода 84 геO нератора 21 тактовых импульсов поступает через элементы И 30 и 31 на. входы синхронизации регистров 7 и 8 микрокоманд. Информация с запоминаю. щих блоков 1 и 2 заносится в регистры 7 и 8 микрокоманд. Далее устройство продолжает функционирование аналогично указанному. По окончании работы любого из процессов с одного из выходов (или одновременно с двух)

0 58.2 или 59.2 вьодается метка окончания работы процесса. Данная метка устанавливает соответствующий триггер 15 или J 6 управления в нулевое состояние Обнуление регистров 5 и

5 6 по выходам 58.1 и 59.1 происходит сразу после начала выполнения соответствующих микропрограмм и вьщачи кодов операций на выходы 58 и 59, что необходимо для исключения несанкционированного повторного запуска микропрограммы. По окончании работы первого и второго процессов устройство принимает исходное состояние и готово к работе в однопрограммном или мультипрограммном ре35жимах .

cpus.Z

фие.д

п

т

/5./

/52

/5./

т

76-2.

107

10В

Ю6

108

| Колосов В.Г., Мелехин В.Ф | |||

| Проектирование узлов и систем автоматики и вычислительной техники.-Л.: Энергоатомиздат, J983, с.51-52 | |||

| Перестраиваемое микропрограммноеуСТРОйСТВО упРАВлЕНия | 1979 |

|

SU830383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1983-11-03—Подача