счетчика, выход пятого элемента И через второй элемент задержки - с входами установки в «О регистра номера нанопрограмм, счетчика и нулевым входом триггера управления, выход окончания микропропрограммы второго запоминающего блока - с вторым входом шестого элемента И, выход которого соединен с входом установки

в «О регистра адреса, входом установки в «О буферного регистра и нулевым входом триггера пуска, информационный выход второго запоминающего блока соединен с вторым входом блока элементов И, выход которого соединен с входом регистра наноопераций, выход которого является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Микропрограммное устройство управления | 1981 |

|

SU945866A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

НАНОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее два запоминающих блока, регистр адреса, буферный регистр, регистр номера нанопрограмм, счетчик, формирователь адреса, коммутатор адреса, два дещифратора адреса, триггер пуска, генератор тактовых импульсов, блок элементов И, семь элементов И, причем вход кода операции устройства соединен с первым информационным входом коммутатора адреса, выход которого соединен с информационным входом регистра адреса, первый выход регистра адреса соединен с входом первого дешифратора адреса, выход которого соединен с адресным входом первого запоминающего блока, выход которого соединен с информационным входом буферного регистра, выход адреса которого соединен с вторым информационным входом коммутатора адреса, выход модифицируемого разряда буферного регистра соединен с управляющим входом коммутатора адреса, выход модифицируемого разряда буферного регистра соединен с управляющим входом формирователя адреса, первый информационный вход которого является входом логических условий устройства, выход кода логических условий буферного регистра соединен с вторым информационным входом формирователя адреса, выход которого соединен с вторым информационным входом коммутатора адреса, выход метки конца микрокоманды буферного регистра соединен с управляющим входом коммутатора адреса, выход регистра номера нанопрограмм соединен с входом второго дещифратора адреса, выход которого соединен с адресным входом второго запоминающего блока, вход устройства соединен с единичным входом триггера пуска, единичный выход которого соединен с входом генератора тактовых импульсов, отличающееся тем, что, с целью повыщения быстродействия, оно содержит триггер управления, два элемента задержки, причем первый выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с синхровходом регистра адреса, второй выход которого соединен с информационным входом регистра номера нанопрограмм, второй вы(Л ход генератора тактовых импульсов соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с синхровходом буферного регистра, первый выход генератора тактовых импульсов соединен с прямым входом четвертого элемента И и единичным входом триггера управления, единичный выход котороOQ О го соединен с вторым входом третьего элемента И, выход которого соединен с синхровходами . регистра номера нанопроО5 грамм и счетчика, выход которого соединен с вторым входом второго дещифратора адреса нулевой , выход триггера управления соединен, с вторым входом второго элемента И и входом первого элемента задержки, выход которого соединен с вторым входом первого элемента И и инверсным входом четвертого элемента И, выход которого соединен с первыми входами пятого, шестого, седьмого элементов И и первым входом блока элементов И, выход окончания нанопрограммы второго запоминающего блока соединен с вторым входом пятого элемента И и инверсным входом седьмого элемента И, выход которого соединен с счетным входом

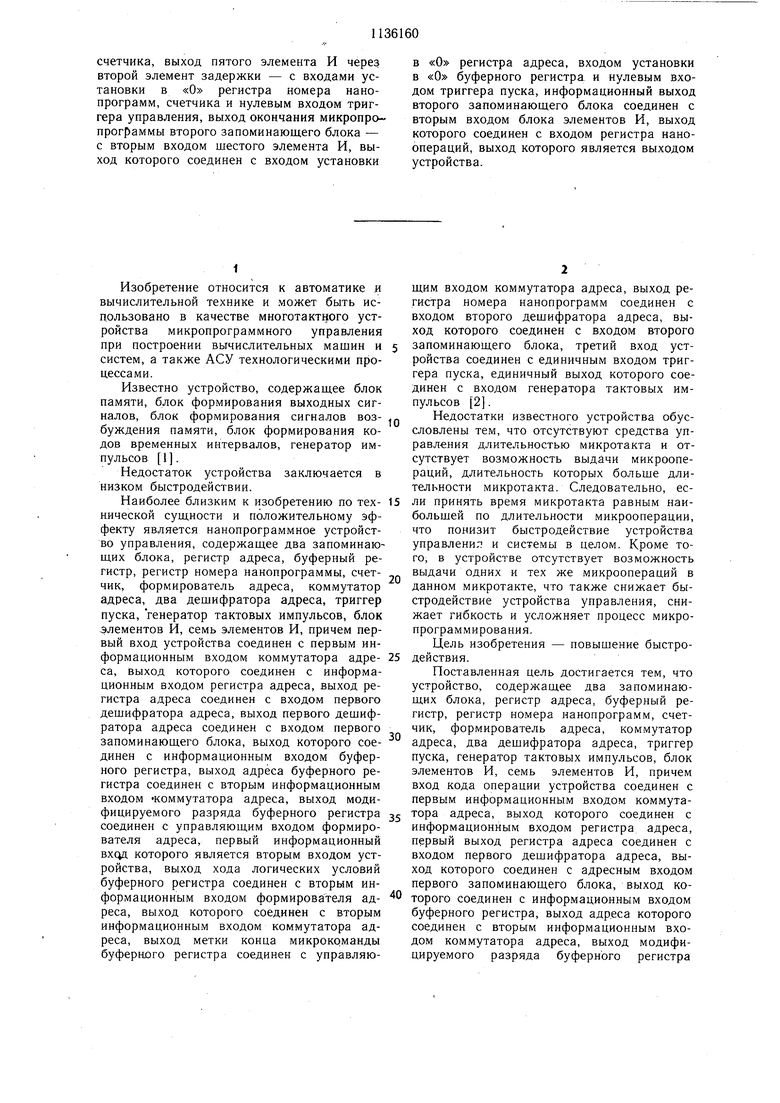

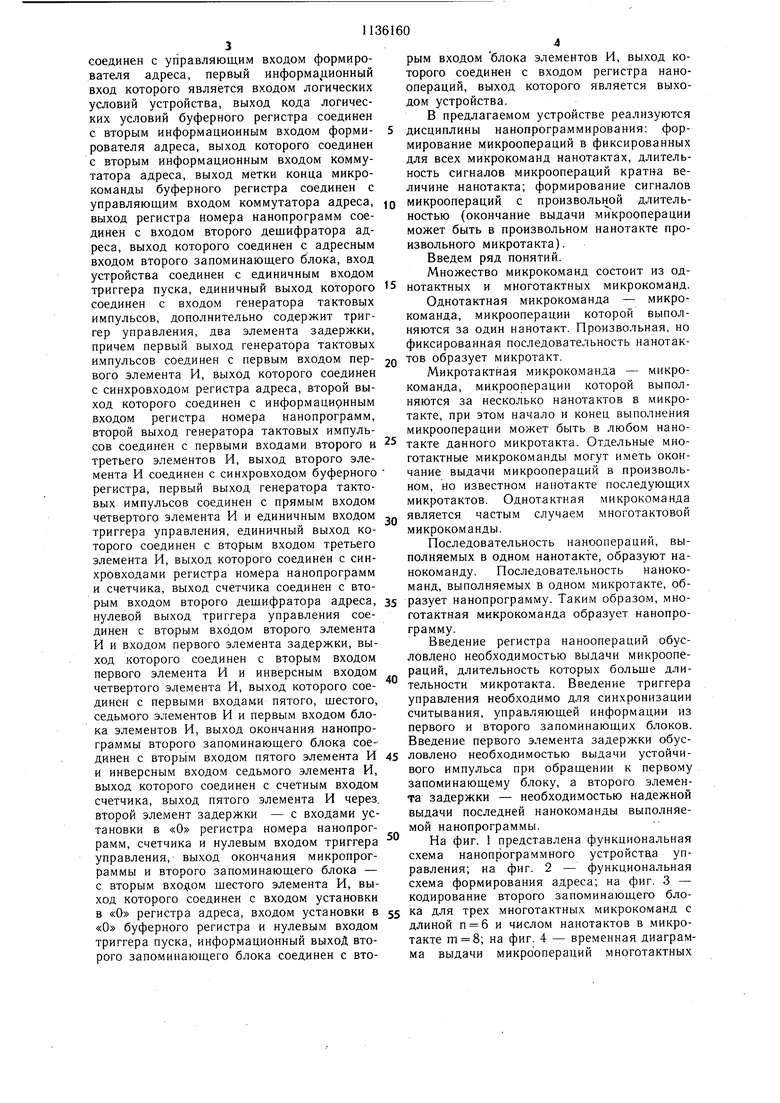

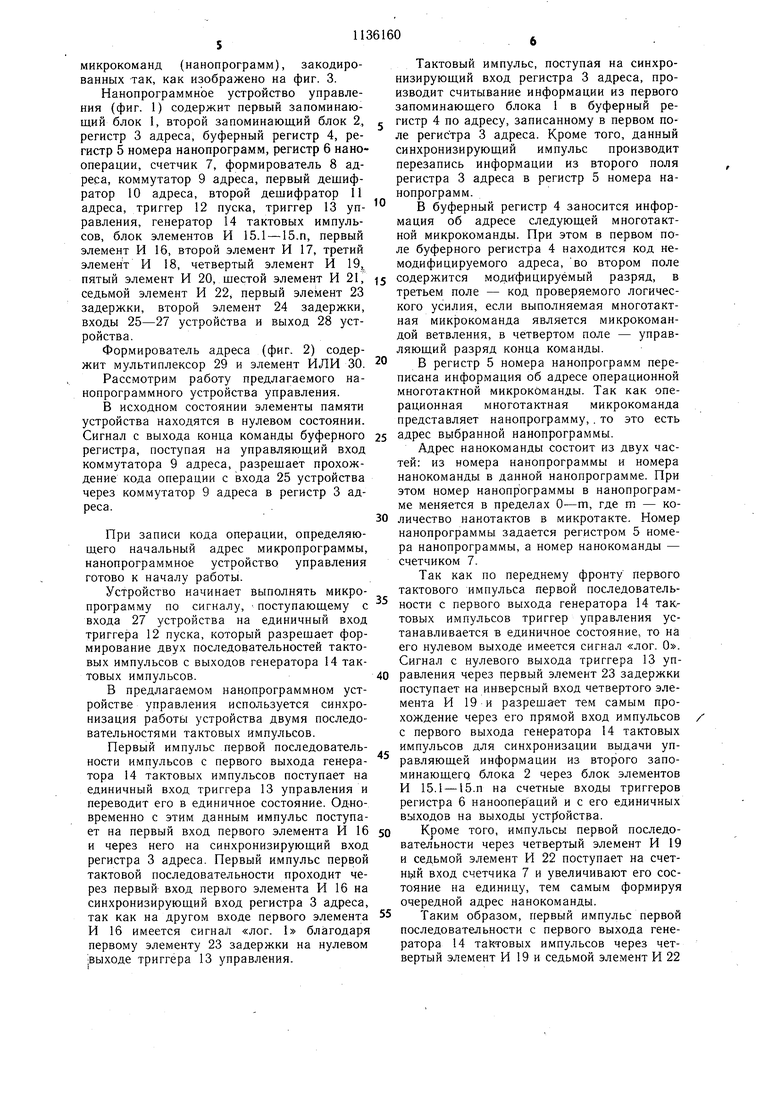

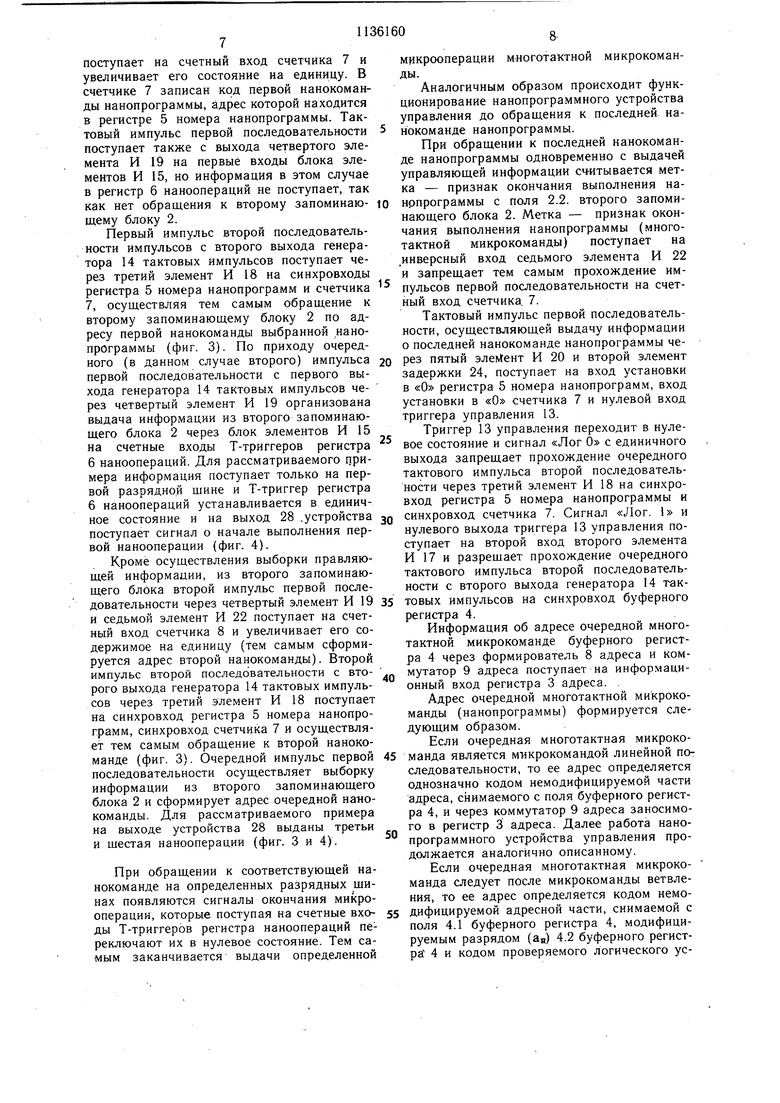

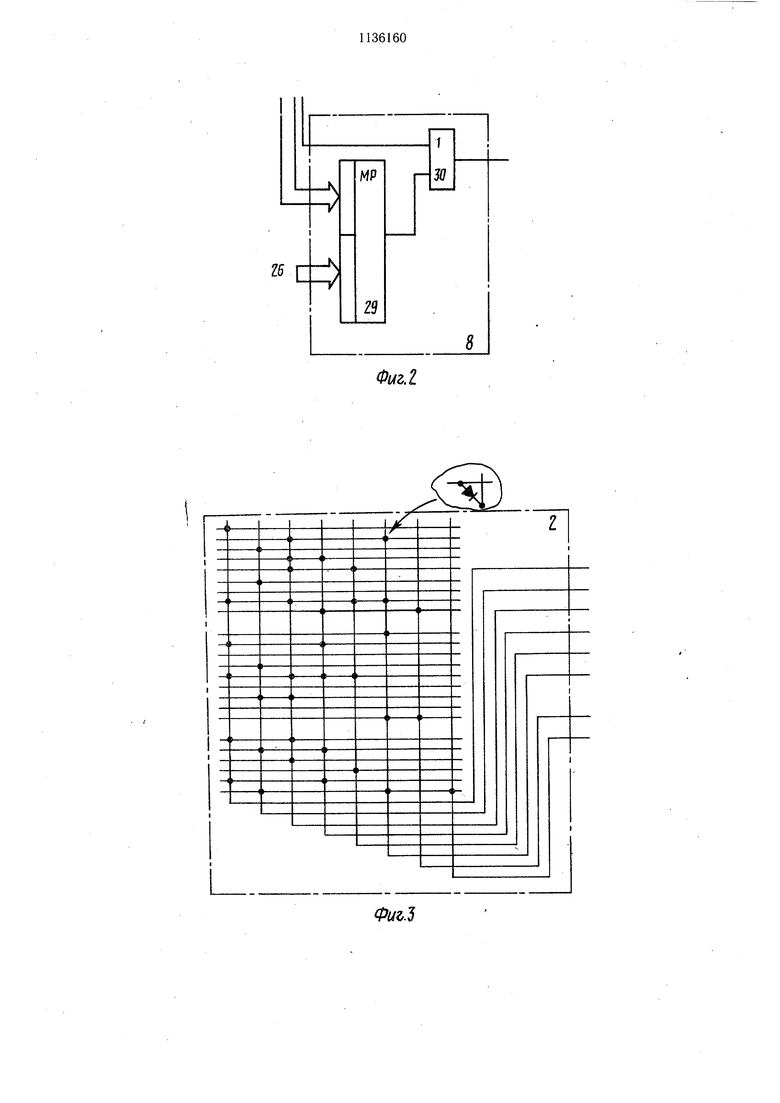

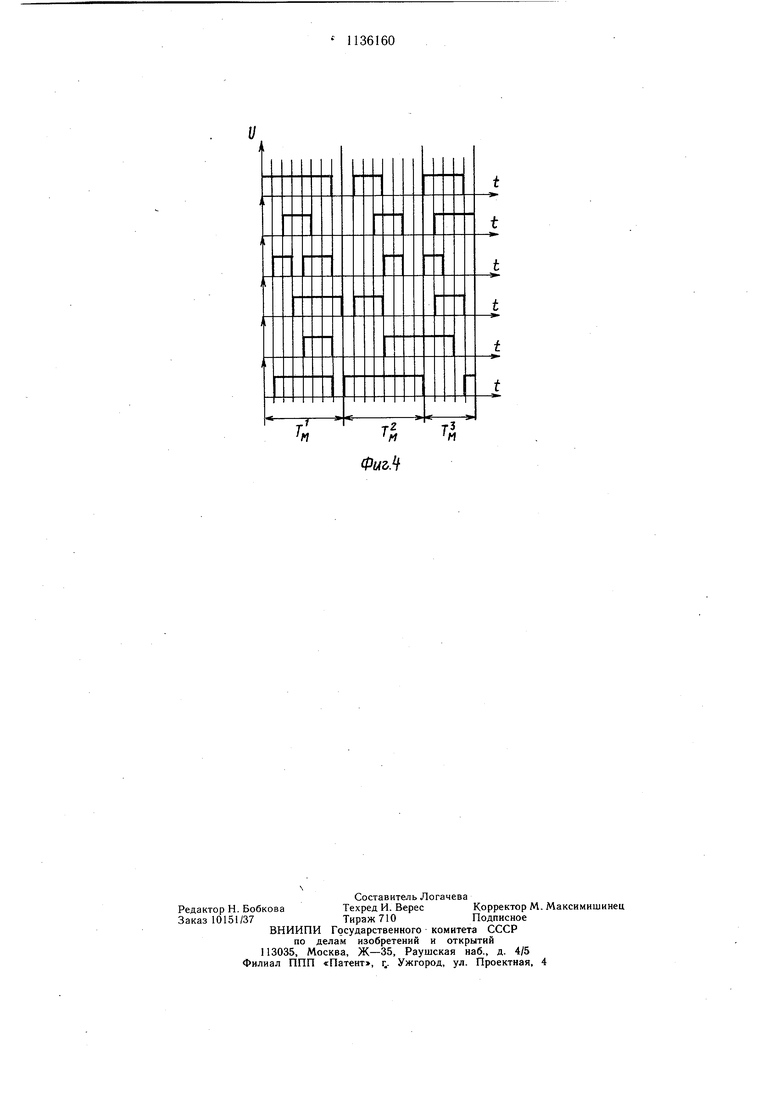

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве многотактного устройства микропрограммного управления при построении вычислительных мащин и систем, а также АСУ технологическими процессами. Известно устройство, содержащее блок памяти, блок формирования выходных сигналов, блок формирования сигналов возбуждения памяти, блок формирования кодов временных интервалов, генератор импульсов 1. Недостаток устройства заключается в низком быстродействии. Наиболее близким к изобретению по технической сущности и положительному эффекту является нанопрограммное устройство управления, содержащее два запоминающих блока, регистр адреса, буферный регистр, регистр номера нанопрограммы, счетчик, формирователь адреса, коммутатор адреса, два дещифратора адреса, триггер пуска, генератор тактовых импульсов, блок элементов И, семь элементов И, причем первый вход устройства соединен с первым информационным входом коммутатора адреса, выход которого соединен с информационным входом регистра адреса, выход регистра адреса соединен с входом первого дещифратора адреса, выход первого дещифратора адреса соединен с входом первого запоминающего блока, выход которого соединен с информационным входом буферного регистра, выход адреса буферного регистра соединен с вторым информационным входом -коммутатора адреса, выход модифицируемого разряда буферного регистра соединен с управляющим входом формирователя адреса, первый информационный вход которого является вторым входом устройства, выход хода логических условий буферного регистра соединен с вторым информационным входом формирователя адреса, выход которого соединен с вторым информационным входом коммутатора адреса, выход метки конца микрокоманды буферного регистра соединен с управляющим входом коммутатора адреса, выход регистра номера нанопрограмм соединен с входом второго дещифратора адреса, выход которого соединен с входом второго запоминающего блока, третий вход устройства соединен с единичным входом триггера пуска, единичный выход которого соединен с входом генератора тактовых импульсов 2. Недостатки известного устройства обуссловлены тем, что отсутствуют средства управления длительностью микротакта и отсутствует возможность выдачи микроопераций, длительность которых больще длительности микротакта. Следовательно, если принять время микротакта равным наибольщей по длительности микрооперации, что понизит быстродействие устройства управления и системы в целом. Кроме того, в устройстве отсутствует возможность выдачи одних и тех же микроопераций в данном микротакте, что также снижает быстродействие устройства управления, снижает гибкость и усложняет процесс микропрограммирования. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство, содержащее два запоминающих блока, регистр адреса, буферный регистр, регистр номера нанопрограмм, счетчик, формирователь адреса, коммутатор адреса, два дещифратора адреса, триггер пуска, генератор тактовых импульсов, блок элементов И, семь элементов И, причем вход кода операции устройства соединен с первым информационным входом коммутатора адреса, выход которого соединен с информационным входом регистра адреса, первый выход регистра адреса соединен с входом первого дешифратора адреса, выход которого соединен с адресным входом первого запоминающего блока, выход которого соединен с информационным входом буферного регистра, выход адреса которого соединен с вторым информационным входом коммутатора адреса, выход модифицируемого разряда буферного регистра соединен с управляющим входом формирователя адреса, первый инфopмa l.иoнный вход которого является входом логических условий устройства, выход кода логических условий буферного регистра соединен с вторым информационным входом формирователя адреса, выход которого соединен с вторым информационным входом коммутатора адреса, выход метки конца микрокоманды буферного регистра соединен с управляющим входом коммутатора адреса, выход регистра номера нанопрограмм соединен с входом второго дешифратора адреса, выход которого соединен с адресным входом второго запоминающего блока, вход устройства соединен с единичным входом триггера пуска, единичный выход которого соединен с входом генератора тактовых импульсов, дополнительно содержит триггер управления, два элемента задержки, причем первый выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с синхровходом регистра адреса, второй выход которого соединен с информационным входом регистра номера нанопрограмм, второй выход генератора тактовых импульсов соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с синхровходом буферного регистра, первый выход генератора тактовых импульсов соединен с прямым входом четвертого элемента И и единичным входом триггера управления, единичный выход которого соединен с вторым входом третьего элемента И, выход которого соединен с синхровходами регистра номера нанопрограмм и счетчика, выход счетчика соединен с вторым входом второго дешифратора адреса, нулевои выход триггера управления соединен с вторым входом второго элемента И и входом первого элемента задержки, выход которого соединен с вторым входом первого элемента И и инверсным входом четвертого элемента И, выход которого соединен с первыми входами пятого, шестого, седьмого элементов И и первым входом блока элементов И, выход окончания нанопрограммы второго запоминающего блока соединен с вторым входом пятого элемента И и инверсным входом седьмого элемента И, выход которого соединен с счетным входом счетчика, выход пятого элемента И через, второй элемент задержки - с входами установки в «О регистра номера нанопрограмм, счетчика и нулевым входом триггера управления, выход окончания микропрограммы и второго запоминающего блока - с вторым входом шестого элемента И, выход которого соединен с входом установки в «О регистра адреса, входом установки в «О буферного регистра и нулевым входом триггера пуска, информационный выхоД второго запоминающего блока соединен с втоpbiM входом блока элементов И, выход которого соединен с входом регистра наноопераций, выход которого является выходом устройства. В предлагаемом устройстве реализуются дисциплины нанопрограммирования: формирование микроопераций в фиксированных для всех микрокоманд нанотактах, длительность сигналов микроопераций кратна величине нанотакта; формирование сигналов микроопераций с произвольной длительностью (окончание выдачи ми крооперации может быть в произвольном нанотакте произвольного микротакта). Введем ряд понятий. Множество микрокоманд состоит из однотактных и многотактных микрокоманд. Однотактная микрокоманда - микрокоманда, микрооперации которой выполняются за один нанотакт. Произвольная, но фиксированная последовательность нанотак ов образует микротакт. Микротактная микрокоманда - микрокоманда, микрооперации которой выполняются за несколько нанотактов в микротакте, при этом начало и конец выполнения микрооперации может быть в любо.м нанотакте данного микротакта. Отдельные многотактные микрокоманды могут иметь окончание выдачи микроопераций в произвольном, но известном нанотакте последующих микротактов. Однотактная микрокоманда является частым случаем многотактовой микрокоманды. Последовательность наноопераций, выполняемых в одном нанотакте, образуют нанокоманду. Последовательность нанокоманд, выполняемых в одном микротакте, образует нанопрограмму. Таким образом, многотактная микрокоманда образует нанопрограмму. Введение регистра наноопераций обусловлено необходимостью выдачи микроопераций, длительность которых больше длительности микротакта. Введение триггера управления необходимо для синхронизации считывания, управляющей информации из первого и второго запоминающих блоков, Введение первого элемента задержки обусловлено необходимостью выдачи устойчивого импульса при обращении к первому запоминающему блоку, а второго элемента задержки - необходимостью надежной выдачи последней нанокоманды выполняемой нанопрограммы. На фиг. представлена функциональная схема нанопрограммного устройства управления; на фиг. 2 - функциональная схема формирования адреса; на фиг. 3 - кодирование второго запоминающего блока для трех многотактных микрокоманд с длиной п 6 и числом нанотактов в микротакте ш 8; на фиг. 4 - временная диаграмма выдачи микроопераций многотактных

микрокоманд (нанопрограмм), закодированных так, как изображено на фиг. 3.

Нанопрограммное устройство управления (фиг. 1) содержит первый запоминающий блок 1, второй запоминающий блок 2, регистр 3 адреса, буферный регистр 4, регистр 5 номера нанопрограмм, регистр 6 нанооперации, счетчик 7, формирователь 8 адреса, коммутатор 9 адреса, первый дешифратор 10 адреса, второй дещифратор 11 адреса, триггер 12 пуска, триггер 13 управления, генератор 14 тактовых импульсов, блок элементов И 15.1 - 15.п, первый элемент И 16, второй элемент И 17, третий элемент И 18, четвертый элемент И 19,, пятый элемент И 20, щестой элемент И 21, седьмой элемент И 22, первый элемент 23 задержки, второй элемент 24 задержки, входы 25-27 устройства и выход 28 устройства.

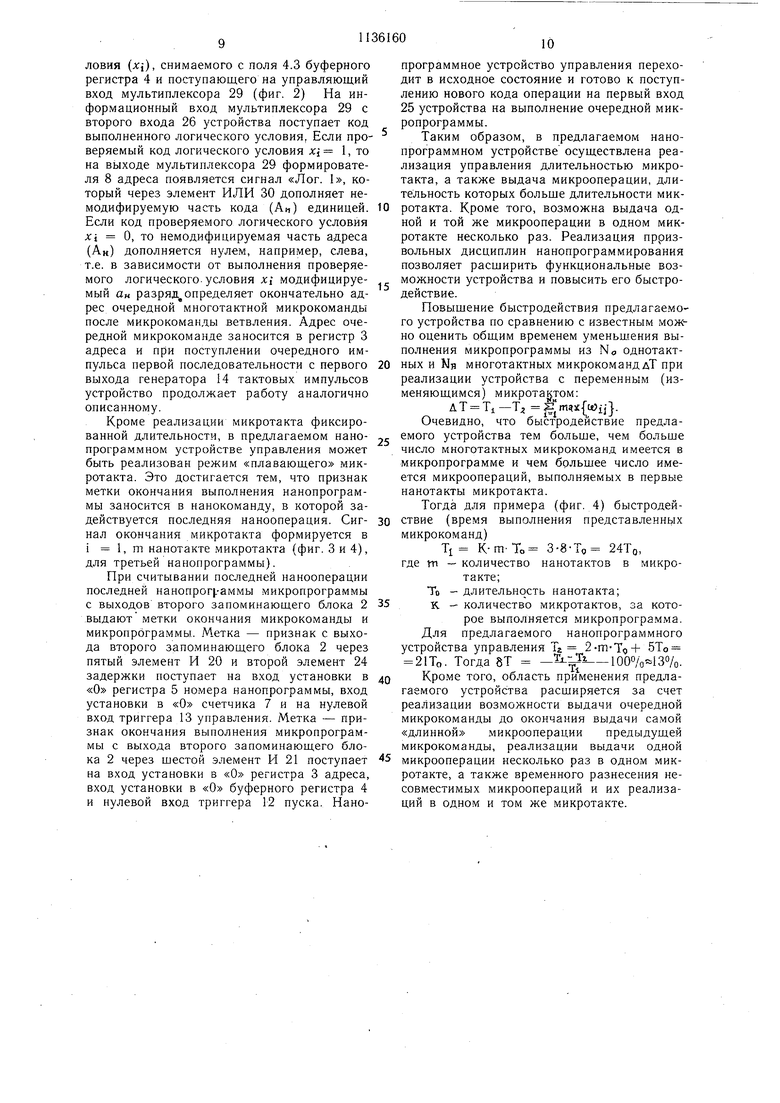

Формирователь адреса (фиг. 2) содержит мультиплексор 29 и элемент ИЛИ 30.

Рассмотрим работу предлагаемого нанопрогра.ммного устройства управления.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии. Сигнал с выхода конца команды буферного регистра, поступая на управляющий вход коммутатора 9 адреса, разрещает прохождение кода операции с входа 25 устройства через коммутатор 9 адреса в регистр 3 адреса.

При записи кода операции, определяющего начальный адрес микропрограммы, Нанопрограммное устройство управления готово к началу работы.

Устройство начинает выполнять микропрограмму по сигналу, поступающему с входа 27 устройства на единичный вход триггера 12 пуска, который разрешает формирование двух последовательностей тактовых импульсов с выходов генератора 14 тактовых импульсов.

В предлагаемом нанопрограммном устройстве управления используется синхронизация работы устройства двумя последовательностями тактовых импульсов.

Первый импульс первой последовательности импульсов с первого выхода генератора 14 тактовых импульсов поступает на единичный вход триггера 13 управления и переводит его в единичное состояние. Одновременно с этим данным импульс поступает на первый вход первого элемента И 16 и через него на синхронизирующий вход регистра 3 адреса. Первый импульс первой тактовой последовательности проходит через первый вход первого элемента И 16 на синхронизирующий вход регистра 3 адреса, так как на другом входе первого элемента И 16 имеется сигнал «лог. 1 благодаря первому элементу 23 задержки на нулевом выходе триггера 13 управления.

Тактовый импульс, поступая на синхронизирующий вход регистра 3 адреса, производит считывание информации из первого запоминающего блока 1 в буферный регистр 4 по адресу, записанному в первом поле регистра 3 адреса. Кроме того, данный синхронизирующий импульс производит перезапись информации из второго поля регистра 3 адреса в регистр 5 номера нанопрограмм.

В буферный регистр 4 заносится информация об адресе следующей многотактной микрокоманды. При этом в первом поле буферного регистра 4 находится код немодифицируемого адреса, во втором поле

содержится модифицируемый разряд, в третьем поле - код проверяемого логического усилия, если выполняемая многотактная микрокоманда является микрокомандой ветвления, в четвертом поле - управляющий разряд конца команды.

В регистр 5 номера нанопрограмм переписана информация об адресе операционной многотактной микрокоманды. Так как операционная многотактная микрокоманда представляет нанопрограмму, . то это есть

адрес выбранной нанопрограммы.

Адрес нанокоманды состоит из двух частей: из номера нанопрограммы и номера нанокоманды в данной нанопрограмме. При этом номер нанопрограммы в нанопрограмме меняется в пределах О-т, где m - количество нанотактов в микротакте. Номер нанопрограммы задается регистром 5 номера нанопрограммы, а номер нанокоманды - счетчиком 7.

Так как по переднему фронту первого тактового импульса первой последовательности с первого выхода генератора 14 тактовых импульсов триггер управления устанавливается в единичное состояние, то на его нулевом выходе имеется сигнал «лог. О. Сигнал с нулевого выхода триггера 13 управления через первый элемент 23 задержки поступает на инверсный вход четвертого элемента И 19 и разрещает тем самым прохождение через его прямой вход импульсов /с первого выхода генератора 14 тактовых импульсов для синхронизации выдачи управляющей информации из второго запоминающего блока 2 через блок элементов И 15.1 - 15.П на счетные входы триггеров регистра 6 наноопераций и с его единичных выходов на выходы устройства.

Кроме того, импульсы первой последовательности через четвертый элемент И 19 и седьмой элемент И 22 поступает на счетнуй вход счетчика 7 и увеличивают его состояние на единицу, тем самым формируя очередной адрес нанокоманды.

Таким образом, первый импульс первой последовательности с первого выхода генератора 14 тактовых импульсов через четвертый элемент И 19 и седьмой элемент И 22 поступает на счетный вход счетчика 7 и увеличивает его состояние на единицу. В счетчике 7 записан код первой нанокоманды нанопрограммы, адрес которой находится в регистре 5 номера нанопрограммы. Тактовый импульс первой последовательности поступает также с выхода четвертого элемента И 19 на первые входы блока элементов И 15, но информация в этом случае в регистр 6 наноопераций не поступает, так как нет обращения к второму запоминающему блоку 2. Первый импульс второй последовательности импульсов с второго выхода генератора 14 тактовых импульсов поступает через третий элемент И 18 на синхровходы регистра 5 номера нанопрограмм и счетчика 7, осуществляя тем самым обращение к второму запоминающему блоку 2 по адресу первой нанокоманды выбранной нанопрограммы {фиг. 3). По приходу очередного (в данном случае второго) импульса первой последовательности с первого выхода генератора 14 тактовых импульсов через четвертый элемент И 19 организована выдача информации из второго запоминающего блока 2 через блок элементов И 15 на счетные входы Т-триггеров регистра 6 наноопераций. Для рассматриваемого примера информация поступает только на первой разрядной шине и Т-триггер регистра 6 наноопераций устанавливается в единичное состояние и на выход 28 .устройства поступает сигнал о начале выполнения первой наноопераций (фиг. 4). Кроме осуществления выборки правляющей информации, из второго запоминающего блока второй импульс первой последовательности через четвертый элемент И 19 и седьмой элемент И 22 поступает на счетныи вход счетчика о и увеличивает его содержимое на единицу (Тем самым сформируется адрес второй нанокоманды). Второй импульс второй последовательности с второго выхода генератора 14 тактовых импульсов через третий элемент И 18 поступает на синхровход регистра 5 номера нанопрограмм, синхровход счетчика 7 и осуществляет тем самым обращение к второй нанокоманде (фиг. 3). Очередной импульс первой последовательности осуществляет выборку информации из второго запоминающего блока 2 и сформирует адрес очередной нанокоманды. Для рассматриваемого примера на выходе устройства 28 выданы третьи и шестая наноопераций (фиг. 3 и 4). При обращении к соответствующей нанокоманде на определенных разрядных шинах появляются сигналы окончания микрооперации, которые поступая на счетные входы Т-триггеров регистра наноопераций переключают их в нулевое состояние. Тем самым заканчивается выдачи определенной многотактнои микрокоманмикрооперацииды. Аналогичным образом происходит функционирование нанопрограммного устройства управления до обращения к последней, нанокоманде нанопрограммы. При обращении к последней нанокоманде нанопрограммы одновременно с выдачей управляющей информации считывается метка - признак окончания выполнения нанрпрограммы с поля 2.2. второго запоминающего блока 2. Метка - признак окончания выполнения нанопрограммы (многотактной микрокоманды) поступает на .инверсный вход седьмого элемента И 22 и запрещает тем самым прохождение импульсов первой последовательности на счетный вход счетчика. 7. Тактовый импульс первой последовательности, осуществляющей выдачу информации о последней нанокоманде нанопрограммы пятый И 20 и второй элемент задержки 24, поступает на вход установки в «О регистра 5 номера нанопрограмм, вход установки в «О счетчика 7 и нулевой вход триггера управления 13. Триггер 13 управления переходит в нулевое состояние и сигнал «Лог О с единичного выхода запрещает прохождение очередного тактового импульса второй последовательности через третий элемент И 18 на синхровход регистра 5 номера нанопрограммы и синхровход счетчика 7. Сигнал «Jlor. 1 и нулевого выхода триггера 13 управления поступает на второй вход второго элемента И 17 и разрешает прохождение очередного тактового импульса второй последовательности с второго выхода генератора 14 тактовых импульсов на синхровход буферного регистра 4. Информация об адресе очередной многотактнои микрокоманде буферного регистра 4 через формирователь 8 адреса и коммутатор 9 адреса поступает на информационный вход регистра 3 адреса. . Адрес очередной многотактнои микрокоманды (нанопрограммы) формируется следующим образом. Если очередная многотактная микрокоманда является микрокомандой линейной последовательности, то ее адрес определяется однозначно кодом немодифицируемой части адреса, снимаемого с поля буферного регистра 4, и через коммутатор 9 адреса заносимого в регистр 3 адреса. Далее работа нанопрограммного устройства управления продолжается аналогично описанному. Если очередная многотактная микрокоманда следует после микрокоманды ветвления, то ее адрес определяется кодом немодифицируемой адресной части, снимаемой с поля 4.1 буферного регистра 4, модифицируемым разрядом (ая) 4.2 буферного регистра 4 и кодом проверяемого логического условия (xj), снимаемого с поля 4.3 буферного регистра 4 и поступающего на управляющий вход мультиплексора 29 (фиг. 2) На информационный вход мультиплексора 29 с второго входа 26 устройства поступает код выполненного логического условия, Если проверяемый код логического условия xi 1, то на выходе мультиплексора 29 формирователя 8 адреса появляется сигнал «Лог. 1, который через элемент ИЛИ 30 дополняет немодифируемую часть кода (Ац) единицей. Если код проверяемого логического условия xi О, то немодифицируемая часть адреса (Ан) дополняется нулем, например, слева, т.е. в зависимости от выполнения проверяемого логического, условия xi модифицируемый Он разряд определяет окончательно адрес очередной многотактной микрокоманды после микрокоманды ветвления. Адрес очередной микрокоманде заносится в регистр 3 адреса и при поступлении очередного импульса первой последовательности с первого выхода генератора 14 тактовых импульсов устройство продолжает работу аналогично описанному.

Кроме реализации микротакта фиксированной длительности, в предлагаемом нанопрограммном устройстве управления может быть реализован режим «плавающего микротакта. Это достигается тем, что признак метки окончания выполнения нанопрограммы заносится в нанокоманду, в которой задействуется последняя нанооперация. Сигнал окончания микротакта формируется в i 1, m нанотакте микротакта (фиг. 3 и 4), для третьей нанопрограммы).

При считывании последней нанооперации последней нанопрог}.-аммы микропрограммы с выходов второго запоминающего блока 2 .выдают метки окончания микрокоманды и микропрограммы. Метка - признак с выхода второго запоминающего блока 2 через пятый элемент И 20 и второй элемент 24 задержки поступает на вход установки в «О регистра 5 номера нанопрограммы, вход установки в «О счетчика 7 и на нулевой вход триггера 13 управления. Метка - признак окончания выполнения микропрограммы с выхода второго запоминающего блока 2 через щестой элемент И 21 поступает на вход установки в «О регистра 3 адреса, вход установки в «О буферного регистра 4 и нулевой вход триггера 12 пуска. Нанопрограммное устройство управления переходит в исходное состояние и готово к поступлению нового кода операции на первый вход 25 устройства на выполнение очередной микропрограммы.

Таким образом, в предлагаемом нанопрограммном устройстве осуществлена реализация управления длительностью .микротакта, а также выдача микрооперации, длительность которых больше длительности микротакта. Кроме того, возможна выдача одной и той же микрооперации в одном микротакте несколько раз. Реализация прризвольных дисциплин нанопрограммирования позволяет расширить функциональные возможности устройства и повысить его быстродействие.

Повышение быстродействия предлагае.мого устройства по сравнению с известным можно оценить общим временем уменьшения выполнения микропрограммы из N, однотактных и NH многотактных микрокоманд дТ при реализации устройства с переменным (изменяющимся) микротактом:

AT TI-T, (u)ii}.

Очевидно, что быстродействие предлаемого устройства тем больше, чем больше число многотактных микрокоманд имеется в микропрограмме и чем большее число имеется микроопераций, выполняемых в первые нанотакты микротакта.

Тогда для примера (фиг. 4) быстродействие (время выполнения представленнь1х микрокоманд)

TI K-m-To 3-8-То 24То, где m - количество нанотактов в микротакте;

То - длительность нанотакта; К - количество микротактов, за которое выполняется микропрограмма.

Для предлагаемого нанопрограммного устройства управления Тг 2тТо+ 5То 21Т„. Тогда 8Т - 100°/,13°/о.

Кроме того, область применения предлагаемого устройства расширяется за счет реализации возможности выдачи очередной микрокоманды до окончания выдачи самой «длинной микрооперации предыдущей микрокоманды, реализации выдачи одной микрооперации несколько раз в одном микротакте, а также временного разнесения несовместимых микроопераций и их реализаций в одном и том же микротакте.

)

-30

Фиг, г

Фи.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1974 |

|

SU519710A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1981 |

|

SU945866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1983-01-11—Подача