участка первого регистра микрокоманд соединен с первым входом четвертого элемента ИЛИ и с вторым инверсным управляющим входом второго коммутатора адреса, выход начала параллельного участка второго регистра микрокоманд соединен с вторьм входом четвертого элемента ИЛИ и вторым инверс ным управляющим входом первого комму татора адреса, выходы управления синхронизацией первого и второго регистров микрокоманд соединены соответственно с первым и вторым входй ми пятого элемента ИЛИ и с вторыми входами второго и третьего элемента ИЖСоответственно, .выход пятого элемента ИЛИ соединен со счетным входом триггера управления синхрони- зацией, единичный и нулевой выходы которого соединены соответственно с первыми и вторыми информационными входами первого и второго коммутаторов управления, выход пятого элемента И -соединен с. первым выходом группы выходов ошибки устройства и с первым входом шестого элемента ИЛИ, выход которого соединен с нулевым входом тригогера пуска, выходы второго и первого коммутаторов управления соединены с первыми входами шеетого и седьмого элементов И соответственно, вьпсод шестого элемента И соединен с входами синхронизации второго регистра адреса и второго регистра микрокоманд, выход седьмого элемента И соединен с входами синхронизации первого регистра адреса и первого регистра микрокоманд, выход четвертого элемента ИЛИ соединен с единичным входом триггера начала параллельного участка, единичньй выход которого соединен с первыми входами восьмого, девятого -и деся того элементов И, первого и второго элементов И-НЕ и с третьими и шестыми информационными входами первого и второго коммутаторов управ ления, выходы конца параллельного участка первого и второго регистров микрокоманд соединены соответственно с единичными входами первого и второго триггеров окончания параллельного участка, единичный выход первого триггера окончания параллельного участка соединен с первым входом одиннадцатого элемента И и с вторым входом второго элемента ИНЕ, нулевой выход пер.вого триггера 64 окончания параллельного участка соединен с вторым чходом восьмого элемента И, выход которого Соединен с третьим входом второго элемента ИЛИ, нулевой выход второго триггера окончания параллельного участка соединен с вторым входом десятого элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ, единичный выход второго триггера окончания параллельного участка соединен с вторыми входами одиннадцатого элемента И и первого элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, выход одиннадцатого элемента И соединен с входом первого одновибратора и с вторыми входами четвертого и пятого элементов И, выход одновибратора соединен с входом первого элемента задержки, выход которого соединен с нулевыми входами триггера начала параллельного участка и первого и второго триггеров окончания параллельного участка, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, группа выходов которого является группой выходов микроопераций устройства, выход конца работы группы выходов блока элементов ИЛИ соединен с вторым входом шестого элемента ИЛИ и с вторым входом девятого элемента И, вькод которого соединен с вторым входом группы выходов ошибки устройства, группа выходов адреса первого регистра микрокоманд соединена с первой группой входов схемы сравнения адресов, с первой группой входов схемы сравнения адресов, с первой группой информационных входов первого коммутатора адреса и первой и второй группами информационных входов второго коммутатора адреса, выходы первого и второго коммутаторов адреса соединены соответственно с вторьми входами первого и второго формирователей адреса микрокоманд, группа выходов адреса второго регистра микрокоманд соединена с второй группой ВХОДОВ- схемы сравнения адресов и второй .группой информационных входов первого коммутатора адреса и третьей группой информационных входов второго коммутатора адреса, выходы модифицируемых разрядов адреса первого и второго регистров микрокоманд соединены с третьими входами первого и второго формирователей адреса микрокоманд соответственно, выходы которых соеj динены с вторыми информационными в&одами первого и второго регистров адреса, выходы первого и второго регистров адреса соединены соответст в.енно с адресными входами первого и второго блоков памяти, выходы кото рых соединены с информационными входами первого и второго регистров микрокоманд соответственно, о т л иЧ а ю щ е е с я тем, что, с целью повьппения достоверности и оперативности контроля устройства, в него введены первый и второй коммутаторы операционных частей, дешифратор, счетчик, первый и второй триггеры ошибок, первый, второй, третий и четвертый блоки элементов И, второй и третий элементы задержки, второй одновибратор, седьмой и восьмой элементы ИЛИ, третий элемент И-НЕ, двенадцатый, тринадцатый, четырнадцатьй, пятнадцатый, шестнадцатый и семнадцатый элементы И, причем вьЕход первого элемента И соединен с первым входом двенадцатого элемента И, с входом второго элемента задержки и с входом второго одновибратора, выход которого соединен с уста новочными входами первого и второго регистров микрокоманд, выход второго элемента задержки соединен с первьм входом тринадцатого элемента И, второй вход которого соединен с вьпсо дом одиннадцатого элемента И, вь1ход тринадцатого элемента И соединен с единичным входом триггера управления синхронизацией, единичный выход триггера начала параллельного участка соединен с вторым входом двенадцатого элемента И, выход которого соединен со счетным .входом счетчика выходы счетчика соединены с входами дешифратора, выходы дешифратора сое динены с соответствующими управляю,дими входами первого и второго коммутаторов операционных частей, выходы которых соединены с первыми входами первой и второй схем сравнения операционных частей соответственно, выход логических условий первого регистра микрокоманд соединен с пер выми входами первого и второго блоков элементов И, вьигод первого блок 1 4 элементов И соединен с первым информа ционным входом первого коммутатора адреса, первым и вторым информационными входами второ.го коммутатора адреса, выход второго.блока элементов И соединен с вторым входом второй схемы сравнения операционных частей, выход неравенства которой соединен с первым входом четырнадцатого элемента И, выход логических условий второго регистра микрокоманд соединен с первыми входами тр.етьего и четвертого блоков элементов И, выход третьего блока элементов И соединен с вторым входом первой схемь сравнения операционных частей, выход которой соединен с первым входом пятнадцатого элемента И, выход четвертого блока элементов И соединен со вторым и третьим информационными входами первого коммутатора-адреса, третьим, информационным входом второго коммутатора адреса, выход начала параллельного участка первого регистра микрокоманд соединен с третьим инверсным управляющим входом первого коммутатора адреса, выход начала параллельного участка второго регистра микрокоманд соединен с третьим инверсным управляющим входом второго коммутатора адреса, нулевой выход триггера начала параллельного участка соединен с первыми входами шестнадцатого и семнадцатого элементов И, с вторыми входами первого и четвертого блоков элементов И и с входом третьего элемента задержки, выход которого соединен с третьими и четвертыми прямыми управляющими входами первого и второго коммутаторов адреса, единичный выход первого триггера окончания параллельного участка соединен с первым входом третьего элемента И-НЕ и с вторым входом шестнадцатого элемента И, выход которого соединен с третьим выходом группы выходов устройства, единичный выход второго триггера окончания параллельного участка соединен с вторым входом третьего элемента И-НЕ и с вторым входом семнадцатого элемента И, выход которого соединен с четвертым выходом группы выходов устройства, выход третьего элемента И-НЕ соединен с вторыт) . входом четырнадцатого и пятнадцатого -элементов И, выходы которых соединены с единичными входами первого и второго триггеров ошибок соответственно, единичные выходы первого и второго триггеров ошибок соединены соответственно с первым и вторым входами седьмого элемента ИЛИ, выход которого соединен с третьим входом шестого элемента ИЛИ, с пятым выходом группы выходов ошибок устрой ства, выход первого одновибратора соединен с первым входом восьмого 1 4 элемента РШИ, второй вход которого соединен с выходом второго элемента И-НЕ, выход восьмого элемента ИЛИ соединен с вторым входом седьмого элемента И, выход двенадцатого элемента И соединен с установочным входом счетчика, единичный выход триггера начала параллельного участка соединен с вторыми входами второго и третьего блоков элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первьй и второй регистры микрокоманд, первьй и второй формирователи адреса микрокоманд, первьй и второй коммутаторы адреса, первьй и второй коммутаторы управления, триггер начала параллельного участка, триггер управления синхронизацией, первьй и второй триггеры окончания параллельного участка, триггер пуска, схему сравнения адресов, генератор тактовых импульсов, первьй, второй, третий, четвертьй, пятьй и шестой элементы ИЛИ, блок элементов ИЛИ, одиннадцать элементов И, первьй и второй элементы И-НЕ, первьй одновибратор и первый элемент задержки, причем вход кода операции устройства соединен с первыми информационными входами первого и второго-регистров адреса и входами первого элемента ИЛИ, выход которого соединен с единичным входом триггера пуска, вход логических условий устройства соединен с первыми входами первого и второго формирователей адреса, вьгходы которых соединены с вторыми информационными входами первого и второго регис;тров адреса соответственно, выход .триггера пуска соединен с первыми входами первого, второго и третьего элементов И, первьй, второй и третий выходы генератора тактовых импульсов соединены с вторыми входами соответственно первого, второго и третьего элементов И, выход первого элемента И соединен с первыми управляющими входами первого и второго коммутаторов управления, выход второго элемента И соединен с вторыми управляющими входами первого и второго коммутаторов, управления, выход третьего элемента И соединен с третьими управляющими входами первого С и второго коммутаторов управления, о выход равенства и выход неравенства 00 схемы сравнения адресов соединены а: с первыми входами соответственно чет4 вёртого и пятого элементов И, выход четвертого элемента И соединен с первыми входами второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первым и вторым прямыми и первыми инверсным управляющими входами первого коммутатора адреса, выход третьего элемента ИЛИ соединен с первым и вторым прямыми и первым инверсным управляющими входами второго коммутатора адреса, выход поля начала параллельного

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке устройст управления параллельными процессами вычислительных и управляющих систем Известны микропрограммные устройства управления, содержащие первый и второй блоки памяти микрокоманд, регистры микрокоманд и адреса, формирователи адреса, триггеры, элементы И 1 и 2. Недостатками указанных устройств являются низкая производительность и узкая область применения, обусловленные их невозможностью управления параллельными процессами, а также низкая достоверность функционирования, обусловленная отсутствием средств контроля адресов при выходе из параллельного режима. Известно микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первый и второй коммутаторы, блок синхронизации, первый и второй триггеры управления, элементы И и ИЛИ СЗЗ. Недостатками данного устройства является низкая производительность, обусловленная отсутствием технических средств для, управления параллельными процессами и перетактовкой устройства при последовательном выполнении двух четных (нечетных) мик .рокоманд, а также низкая достоверность функционирования. Наиболее близким к изобретению по технической сущности и достигаемому положительному эффекту является микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры адреса, первый и второй регистры микрокоманд, схему сравнения, первый - четвертый коммутаторы, формирователь тактовых импульсов, первый и второй формирователи адреса, первый-пятый триггеры управления, первый-восьмой элементы И, перый-седьмой элементы ИЛИ, первый и второй элементы И-НЕ одновибратор,- блок элементов ИЛИ, причем вход логических условий устройства соединен с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первыми входами соответственно первого и второго регистров адреса, вход кода операции устройства соединен со вторыми информационными входами первого и второго регистров адреса, выходы которых соединены с информационными входами соответственно первого и второго блоков памяти микрокоманд, выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно-первого и второго регистров микрокоманд, первый управляющие выходы первого и второго регистров микрокоманд соединенных с единичными входами соответственно первого и второго триггеров управления, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ,

выход которого является выходом микроопераций устройства, выход адреса .первого регистра микрокоманд соединен с первыми информационными ,входами первого.и второго коммутаторов, выход адреса второго регистра микрокоМанд соединен с вторыми информационными входами первого и второго коммутаторов, выходы которых соединены с вторыми информационными входами соответственно первого и второго , формирователей адреса, вход кода операции устройства через первьш элемент ИЛИ соединен с единичным входом третьего триггера управления, единичный выход которого соединен с входом формирователя тактовых импульсов, первый выход формирователя тактовых импульсов соединен с нулевыми входами триггеров полей микроопераций первого и второго регистров микрокоманд и с первыми информационными входами третьего и четвертого коммутаторов, выходы которых соединены с первыми входами соответственно первого и второго-элементов И, второй и третий выходы формирователя тактовых импульсов соединены соответственно с вторымии третьими информационными входами третьегоИ четвертого коммутаторов, единичный выход четвертого триггера управле- ния соединен с первыми управляюгцими входами третьего, четвертого коммутаторов, лервыми входами третьего, четвертого, пятого элементов И и первого и второго элементов И-НЕ, выходы которых соединены с вторыми входами соответственно первого и второго элементов И, второй управляющий выход первого регистра микрокоманд соединен с первыми входами второго и третьего элементов ИЛИ, выход которого соединен с первым управляющим входом первого коммутатора, второй управляющий выход второго регистра микрокоманд соединен с первым входом четвертого и вторым входом второго элементов ИЛИ, .выход которого соединен с Т-входом пятого триггера управления, единичный выход пятого триггера управления соединен с вторыми управляющими входами- третьего и четвертого коммутаторов, а нулевой выход - с третьими управляющими входами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров микрокоманд

30864Л

через пятый элемент ИЛИ соединены с единичным входом четвертого триггера управления, нулевой выход которого соединен с вторым управляющим вхо5 дом первого коммутатора и первым

управляющим входом второго коммутатора, нулевые выходы первого и второго триггеров управления соединены с вторыми входами соответственно треть10 его и пятого элементов И, выходы которых соединены с вторыми входами соответственно третьего и четвертого элементов ИЛИ, выход которого соединен с вторым управляющим вхо(з До второго коммутатора, третьи

управляющие выходы первого и второго регистров микрокоманд соединены с третьими управляющими входами соответственно первого и второго ком20 fyтaтopoв, единичный выход первого

триггера управления соединен с вторым входом первого элемента И-НЕ и первым входом шестого элемента И, единичный вьрсод второго триггера

5 управления соединен с вторым входом второго элемента И-НЕ и вторым входом шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И,

0 а через одновибратор - с нулевыми входами первого, второго и четвертого триггеров обнуления, выходы адреса первого и второго регистров микрокоманд соединены соответствен5 но с первым и вторым входами схемы сравнения, прямой и инверсный выход которой соединены с вторыми входами соответственно седьмого и восьмого элементов И, выход седьмого элемен0 та И соединен с третьими входами

третьего и четвертого элементов ИЛИ, выход восьмого элемента И соединен с первыми входами шестого и седьмого элементов ИЖ, выходы которых

5 соединены соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выход конца операции блока элементов ИЛИ соединен с вторыми входами шестого

0 элемента ИЛИ и четвертого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ ). Недостатками известного устройст ва являются низкая достоверность

5 и оперативность контроля, обусловленные тем, что контроль адресов выхода из параллельного режима осу.ществляется только в конце выполнения параллельных микроподпрограмм. Во время выполнения параллельных микроподпрограмм поля логических условий микрокоманд свободны, т.е. существует естественная структурная .избыточность полей логических условий, которая может быть использована для контроля выполнения параллел ных микроподпрогр.амм не только во время окончания параллельных участков, но и в ходе выполнения самих параллельньк микроподпрограмм. В устройстве полностью отсутствует сонтроль функции выходов устройства поскольку проверкой охвачены лишь адресные цепи. Кроме того, результа контроля при выполнении параллельных микроподпрограмм формируется только в конце их реализации, что существенно увеличивает время обна ружения ошибки и устранения ее последствий. При выполнении параллельных микроподпрограмм известное устройство может перейти в режим зависания одного из каналов, вследствие того, что выход другого канала на последо вательные мйкроподпрограммы не буде обнаружен. Путем перекрестного зада ния частей микрокоманд в свободных полях логических условий и последую щим сравнением кодов частей микроко манд, записанных в поле логических условий одного блока памяти с часть микрокоманд другого блока памяти мо но существенно повысить достоверность и оперативность контроля устройства. Данная возможность в извес ном устройстве не реализована, что и приводит к низкой достоверности и оперативности контроля. Цель изобретения - повышение достоверности и оперативности контрол микропрограммного устройства управления. Поставленная цель достигается те что в микропрограммное устройство управления, содержащее первый и вто рой блоки памяти микрокоманд, первы и второй регистры адреса, первый и второй регистры микрокоманд, первый и второй формирователи адреса микрокоманд, первый и второй коммут торы адреса, первый и второй коммутаторы управления, триггер начала параллельного участка, триггер упра ления синхронизацией, первый и второй триггеры окончания параллельног 1 46 участка, триггер пуска, схему.сравнения адресов, генератор тактовых импульсов, первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, блок элементов ИЛИ, одиннадцать элементов И,первый и второй элементы И-НЕ, первый одновибратор и первый элемент задержки, причем вход кода операции устройства соединен с первыми информационными входами первого и второго регистров адреса и входами первого элемента ИЛИ, выход которого соединен с единичным входом триггера пуска, вход логических условий устройства соединен с первыми входами первого и второго формирователей адреса, выходы которых соединены с вторыми информационными входами первого и второго регистров адреса соответственно, выход триггера пуска соединен с первыми входами первого, второго и третьего элементов И, первый, второй и третий выходы генератора тактовых импульсов соединены с вторыми входами соответственно первого, второго и третьего элементов И, выход первого элемента И соединен с первыми управляющими и второго коммутатовходами первого ров управления, выход второго эяемента И соединен с вторыми управляющими входами первого и второго коммутаторов управления, выход третьего элемента И соединен с третьими управляющими входами первого и второго коммутаторов управления, выход равенства и выход неравенства схемы сравнения адресов соединены с первыми входами соответственно четвертого и пятого элементов И, выход четвертого элемента И соединен с первыми входами второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первым и вторым прямыми и первым инверсным управляющими входами первого коъ1мутатора адреса, выход третьего элемента ИЛИ соединен с первым и вторым прямыми и первым инверсным управляющими входами второго коммутатора адреса, выход поля начала параллельного участка первого регистра микрокоманд соединен с первым входом четвертого элемента ИЛИ и с вторым инверсным управляющим входом второго коммутатора адреса, выход начала параллельного участка второго регистра микрокоманд соединен с вторым входом четвертого эле71мента ИЛИ и вторым инверсным управляющим входом первого коммутатора адреса, выходы управления синхронизацией первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами пятого элемента ИЛИ и с вторыми входами второго и третьего элементов ИЛИ соответственно, выход пятого элемента ИЛИ соединен со счетным входом триггера управления синхронизацией, единичный и нулевой выходы которого соединены соответственно с первыми и вторыми информационными входами первого и второго коммутаторов управ ления, выход пятого элемента И соеди нен с первым выходом группы выходов ошибки устройства и с первым входом шестого элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, выходы вторрго и первого коммутаторов управления соединены с пер выми входами шестого и седьмого элементов И соответственно, выход шестого элемента И соединен с входами синхронизации второго регистра адреса и второго регистра микрокоманд ыход седьмого элемента И соединен с входами синхронизации первого регистра адреса и первого регистра микрокоманд, выход четвертого элемента ИЛИ соединен с единичным входом триггера начала параллельного участка, единичный выход Которого, соединен с первыми входами восьмого девятого и десятого элементов И, .первого и второго элементов И-НЕ и с третьими и шестыми информационными входами первого и второго коммутаторов управления, выходы кон ца параллельного участка первого и второго регистров микрокоманд сое динены соответственно с единичными входами первого и второго триггеров окончания параллельного участка, ед ничный выход первого триггера окончания параллельного участка соедине с первым входом одиннадцатого эл1еме та И и с вторым входом второго элемента И-НЕ,.нулевой выход первого триггера окончания параллельного участка соединен с вторым входом восьмого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, нулевой выход второго триггера окончания параллельного участка соединен с вторым входом десятого элемента И, выход которого соединен с третьим входом третьего элемента ИЛИ, единичный выход второго триггера окончания параллельного участка соединен с .вторыми входами одиннадцатого элемента И и первого элемента И-НЕ, выход которого соединен с- вторым входом шестого элемента И, выход одиннадцатого элемента И соединен с входом первого одновибратора и с вторыми входами четвертого и пятого элементов И, выход одновибратора соединен с входом первого элемента задержки, выход которого соединен с нулевыми входами триггера начала параллельного участка и первого и второго триггеров окончания параллельного участка, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, группа выходов которого является группой выходов микроопераций устройства, выход конца работы группы выходов блока элементов ИЛИ соединен с вторым входом шестого элемента ИЛИ и свторым входом девятого элемента И, выход которого соединен с вторым входом группы выходов ошибки устройства, группа выходов адреса первого регистра микрокоманд соединена с первой группой входов схемы сравнения адресов, с первой группой входов схемы сравнения адресов, с первой группой информационных входов первого коммутатора адреса и первой и второй группами информационных входов второго коммутатора адреса, выходы первого и второго коммутаторов адреса соединены соответственно с вторыми входами первого и второго формирователей адреса микрокоманд, группа выходов адреса второго регистра микрокоманд соединена с второй группой входов схемы сравнения адресов и второй группой информационных входов первого коммутатора адреса и третьей группой информационных входов второго коммутатора.адреса, выходы модифицируемых разрядов адреса первого и второго регистров микрокоманд соединены с третьими входами первого и второго формирователей адреса микрокоманд соответственио, выходы которых соединены с вторыми информационными .входами первого и второго регистров адреса, выходы первого и второго регистров адреса соединены соответственно с адресными входами первого и второго блоков памяти, выходы которых /соединены с информационньши входами первого и второго регистров микрокоманд соответственно, введены первый и второй коммутаторы операционных частейд дешифратор счетчик-, первый и второй триггеры ошибок, первый, второй, третий и чет вертый блоки элементов И, второй и третий элементы задержки, второй одновибратор, седьмой и йосьмой элементы ИЛИ, третий элемент И-НЕ, двенадцатый, тринадцатьй четырнадцатый, пятнадцатый, шестнадцатый и сем

надцатый элементы И,причем выход первого элемента И соединен с первым входом двенадцатого элемента И, : с входом второго элемента задержки и с входом второго одновибратора, выход которого соединен с установочными входами первого и второго регистров микрокоманд, выход второго элемента задержки соединен с первым входом тринадцатого элемента И,, вто- рой вход которогосоединен с выходом одиннадцатого элемента И, выход тринадцатого элемента И соединен с единичным входом триггера управления синхронизацией, единичный выход триг-30 гера начала параллельного участка соединен с вторым входом двенадцатог элемента И, выход которого соединен со счетным входом счетчика, выходы счетчика соединены с входами дешифра тора, выходы дешифратора соединены с соответствуюпщми управляющими входами первого и второго коммутаторов операционных частей, вькоды кото рых соединены с перзымя входами первой и второй схем сравнения операционных частей соответственно, выход логических условий первого регистра микрокоманд соединен с первыми входа ми первого и второго блоков элементов И, выход первого блока элементов И соединен с первым информационным входом первого коммутатора адреса, первым и вторым информационными входами второго коммутатора адреса, выход второго блока элементов И соединен с вторым входом второй .схемы сравнения операционных частей, выход неравенства которой соединен с первым входом четырнадцатого элемента И, выход логических условий второго регистре микрокоманд соединен с первыми входами

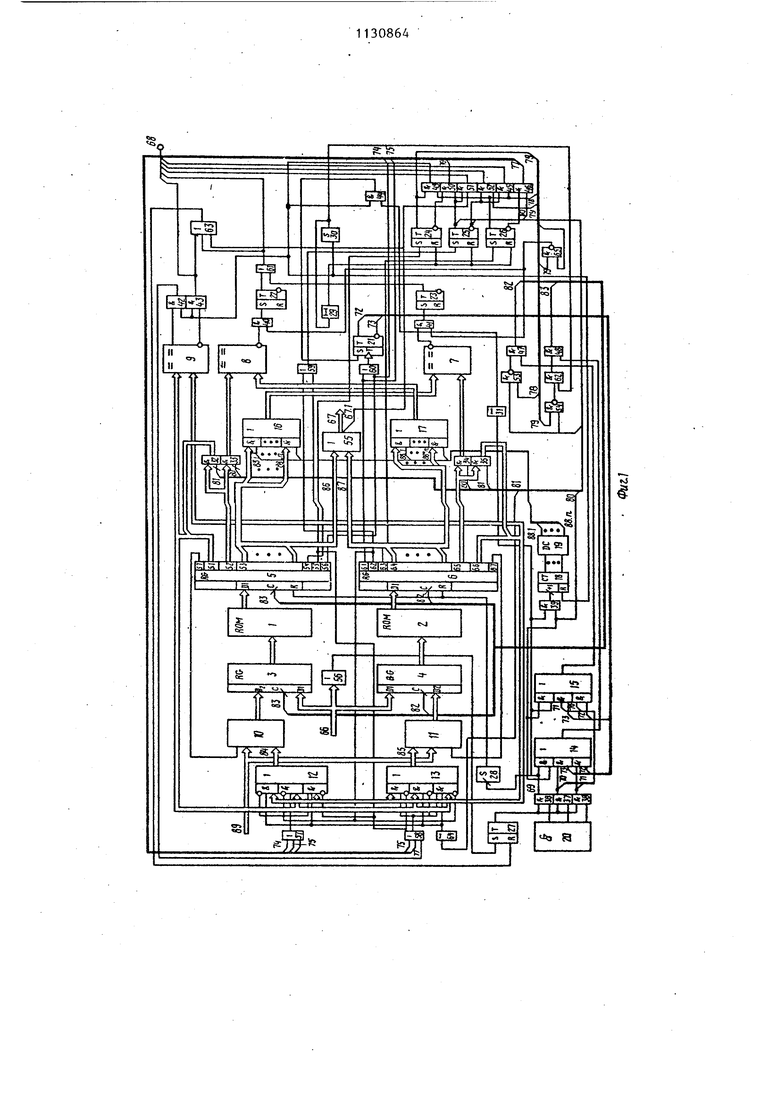

выход начала параллельного участка BTopqro регистра микрокоманд соединен с третьим инверсным управляющим входом второго коммутатора адреса, нулевой выход триггера начала параллельного участка соединен с первыми входами шестнадцатого и семнадцатого элементов И, с вторыми входами первого и четвертого блоков элементов И и с входом третьего элемента задержки, выход которого соединен с третьими и четвертыми прямыми управляющими входами первого и второго коммутаторов адреса, единичный третьего и четвертого блоков элементов И, выход третьего блока элементов И соединен с вторым входом первой схемы сравнения операционных частей, выход которой соединен с первым входом пятнадцатого элемента И, выход четвертого блока элементов И соединен с вторым и третьим информационными входами первого коммутатора адреса, третьим информационным входом второго коммутатора адреса, выход начала параллельного участка первого регистра микрокоманд соединен с третьим инверсным управляющим входом первого коммутатора адреса. выход первого триггера окончания параллельного участка соединен с первым входом третьего элемента И-НЕ и с вторым входом шестнадцатого элемента И, выход которого соединен с третьим выходом группы выходов устройства, единичный выход второго триггера окончания цараллельного участка соединен с вторым входом третьего элемента И-НЕ и с вторым входом семнадцатого элемента И, выход которого соединен с четвертым выходом группы выходов устройства, выход третьего элемента И-НЕ соединен с вторым входом четырнадцатого и пятнадцатого элементов И, выходы которых соединены с- единичными входами первого и второго триггеров ошибок соответственно, единичные выходы первого-и второго триггеров ошибок соединены соответственно с первым и вторым входами седьмого элемента ИЛИ, выход которого соединен с третьим входом шестого элемента ИЛИ, с пятым выходом группы выхоДов ошибок устройства, выход первого одновибратора соединен с первым входом восьмого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И-НЕ, выход восьмого элемента ИЛИ соединен с вторым входом седьмого элемента И, выход двенадцатого элемента И соединен с установочным входом счетчика, единичный выход триггера начала параллельного участка соединен с вторыми входами второго и третьего блоков элементов И Сущность изобретения состоит в по вьшении достоверности и оперативност контроля на основе использования естественной структурной избыточност полей логических условий при выполне нии параллельных участков путем пере крестного задания в свободных полях частей микрокоманд параллельных микроподпрограмм. Введение первого-четвертого блоков элементов И, первого и второго коммутаторов операционных частей, первой и второй схем сравнения, второго одновибратора, третьего элемента И-НЕ, четырнадцатого и пятнадцато го элементов И, первого и второго триггеров ошибок, седьмого элемента ИЛИ и обусловленных ими связей позволяет осуществить контроль микро команд, записанных в первом и втором блоках памяти, и выдачу сигнала ошиб ки при искажении информациии, считываемой из первого или второго блоков памяти. Введение двенадцатого элемента И, счетчика и дешифратора и обусловленных ими связей позволяет осуществлят выбор частей микрокоманд, записанных в первом и второ блоках памяти. Введение восьмого элемента ШШ, тринадцатого элемента И, второго эле мента задержки и обусловленных ими связей позволяет осуществить прохождение тактового импульса с выхода первого коммутатора управления на входы синхронизации первого регистра адреса и первого регистра микрокоман при выходе из параллельного режима, а также осуществлять установку триггера управления синхронизацией в еди ничное состояние с временем задержки после окончания параллельных участков. Введение шестнадцатого и семнадцатого элементов И и обусловленных ими связей позволяет формировать сигналы ошибок в параллельном режиме. Введение третьего элемента задержки и обусловленных им связей позволяет производить блокировку первого и второго коммутаторов адреса нулевым сигналом при входе в параллельный режим. На фиг. 1 приведена функциональная схема устройства; на фиг, 2 функциональная схема первого и второго формирователей адреса; на фиг. 3 - формат микрокоманд, считьгваемых из блоков памяти; на фиг. 4 структурная схема контроля устройства; на фиг. 5 - временная диаграмма работы устройства. Параллельное микропрограммное устройство управления с контролем (фиг. 1) содержит первый блок 1 памя-. ти микрокоманд (ПЗУ 1), второй блок 2 памяти микрокоманд (ПЗУ 2), первый регистр 3 адреса, второй регистр 4 адреса, первый регистр 5 микрокоманд, содержащий поле 5;1 адреса, поле 5.2 логических условий, поле 5.3 микроопераций, поле 5.4 метки М;, конца параллельного участка микропрограммы, поле 5.5 метки Мл начала параллельного участка, поле 5.6 метки Mj управления синхронизацией, поле 5.7 модифицируемого разряда адреса, второй регистр 6 микрокоманд, содержащий поле 6.1 метки Mj управления синхронизацией, поле 6.2 метки Mj начала параллельного участка микропрограммы, поле 6.3 метки М конца параллельного участка микропрограммы, поле 6.4 микроопераций, поле 6.5 логических условий, поле 6.6 адреса, поле 6,7 модифицируемого разряда адреса, первую схему 7 сравнения операционных частей, вторую схему 8 сравнения операционных частей, схему 9 сравне- ния адреса, первый формирователь 10 адреса микрокоманд, второй формирователь 11 адреса микрокоманд, первый коммутатор 12 адреса, второй коммутатор 13 адреса, первый коммутатор 14 управления, второй коммутатор 15 управления, первый коммутатор 16 операционных частей, второй коммутатор 17 операционных частей. счетчик 18, дешифратор 19, генератор 20 тактовых импульсов, триггер 21 управления синхронизацией, первый триггер 22 ошибки, второй триггер 23 ошибки, первый триггер 24 окончания параллельного участка, триггер 25 начала параллельного участка, второй триггер 26 окончания параллельного участка, триггер 27 пуска, второй одновибратор 28, первый элемент 29 задержки, первый одновибратор 30, вторбй элемент 31 задержки, первый блок элементов И 32, второй блок элементов И 33, третий блок элементов И 34, четвертый блок элементов -И 35, первый элемент И 36, второй элемент И 37, третий элемент И 38, двенадцатый элемент И 39, четырнадцатый элемент И 40, пятнадцатый элемент И 41, четвёртьш элет мент И 42, пятый элемент И 43, тринадцатый элемент И 44, семнадцатый элемент И 45, десятый элемент И 46, шестой элемент И 47, седьмой эле-мент И 48, одиннадцатый элемент И 49 восьмой элемент И 50, девятый элемент И 51,. шестнадцатый элемент И 52 первый элемент И-НЕ 53, второй элемент Й-НЕ 54, блок элементов ИЛИ 55, первьй элемент ИЛИ 56, второй элемент ИЛИ 57, третий элемент ИЛИ 58, четвертый элемент ИЛИ 59, пятый элемент ИЛИ 60, седьмой элемент ИЛИ 61, восьмой элемент ИЛИ 62, шестой элемент ИЛИ 63, третий элемент 64 задержки, третий элемент И-НЕ 65. Кроме того, на фиг. 1 показаны: вход 66 кода операции устройства, выход 67 микроопераций устройства, выход 67,1 микрооперации конца работы, группа выходов 68 ошибки устройства, выход 69 первого элемента И 36, выход 70 (71) второго (третьего) элемента И 37 (38), единичный (нулевой) выход 72 (73) триггера 21 управления синхронизацией, выход 74 (75) полей 5.6 (6.1) управления, синхронизацией регистра 5 (6) микрокоманд соответственно, выход 76 (77) восьмого (десятого) элемента И 50.(46), единичный выход 79 (78) первого (второго) триггера 24 (26) управления, единичный (нулевой) выход 80 (81) второго триггера 25 управления, выход 82 (83) шестого (седьмого) элемента И 47 (48), выход 84 (85) первого (второго) коммутатора 12 (13 адреса, выход 86 (87) поля 5.3 (6.4) микроопераций первого (второго) регистра 5 (6) микрокоманд, первый п-й 88.1-88.П выходы дешифратора соответственно, выход 89 логических условий устройства.

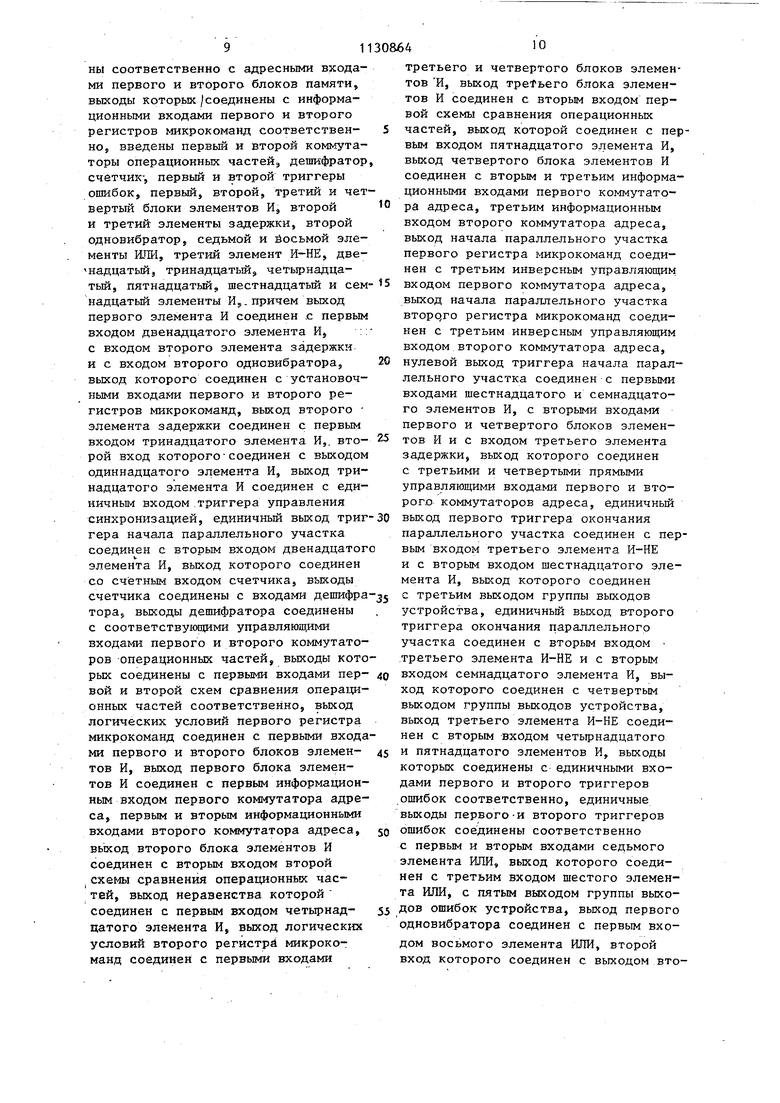

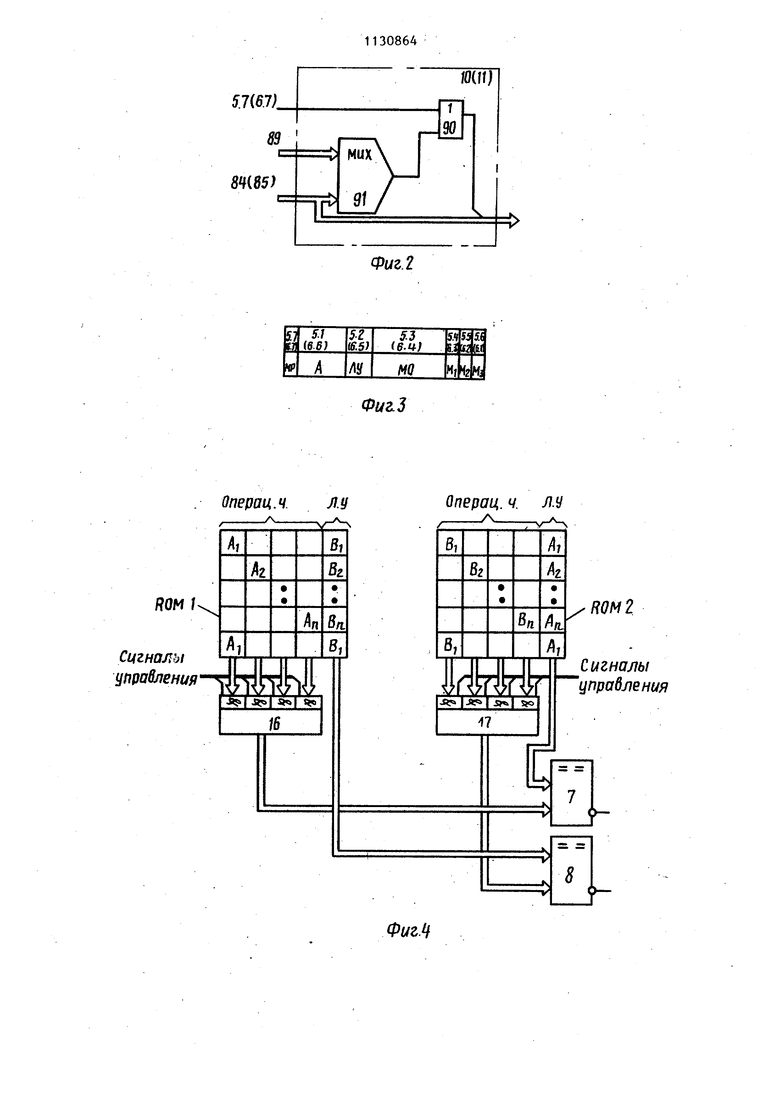

Формирователь 10 (11) адреса (фиг. 2) содержит элемент ИЛИ 90 я мультиплексор 91.

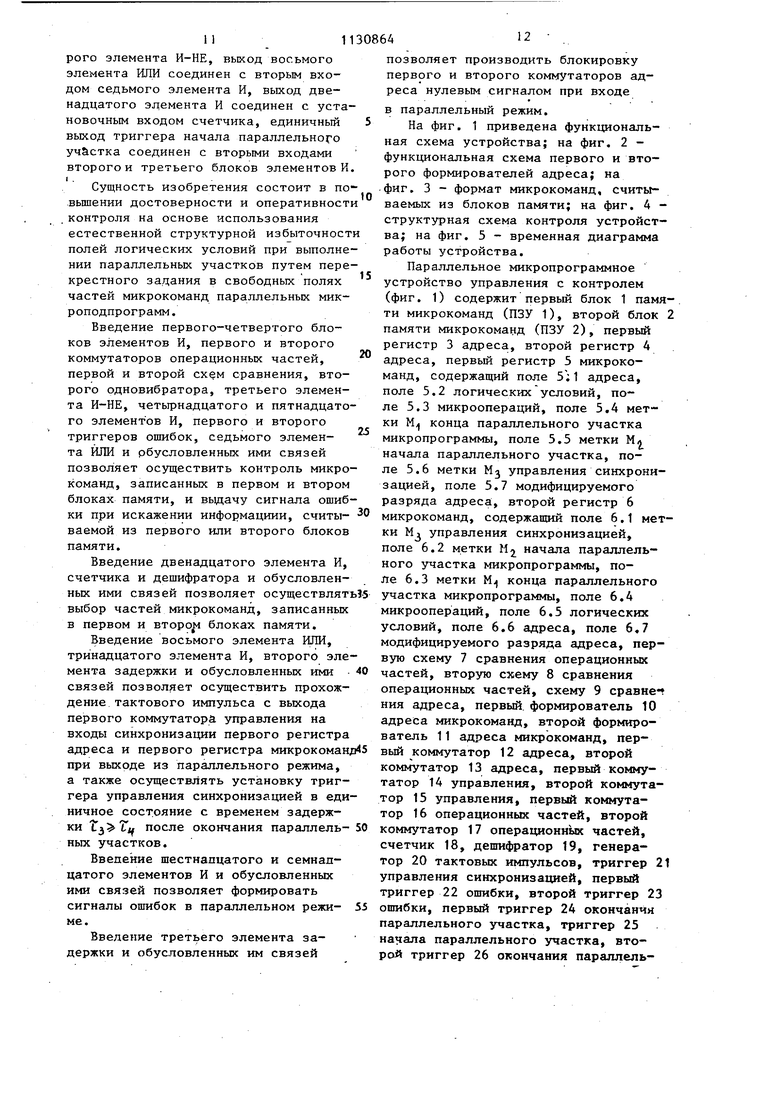

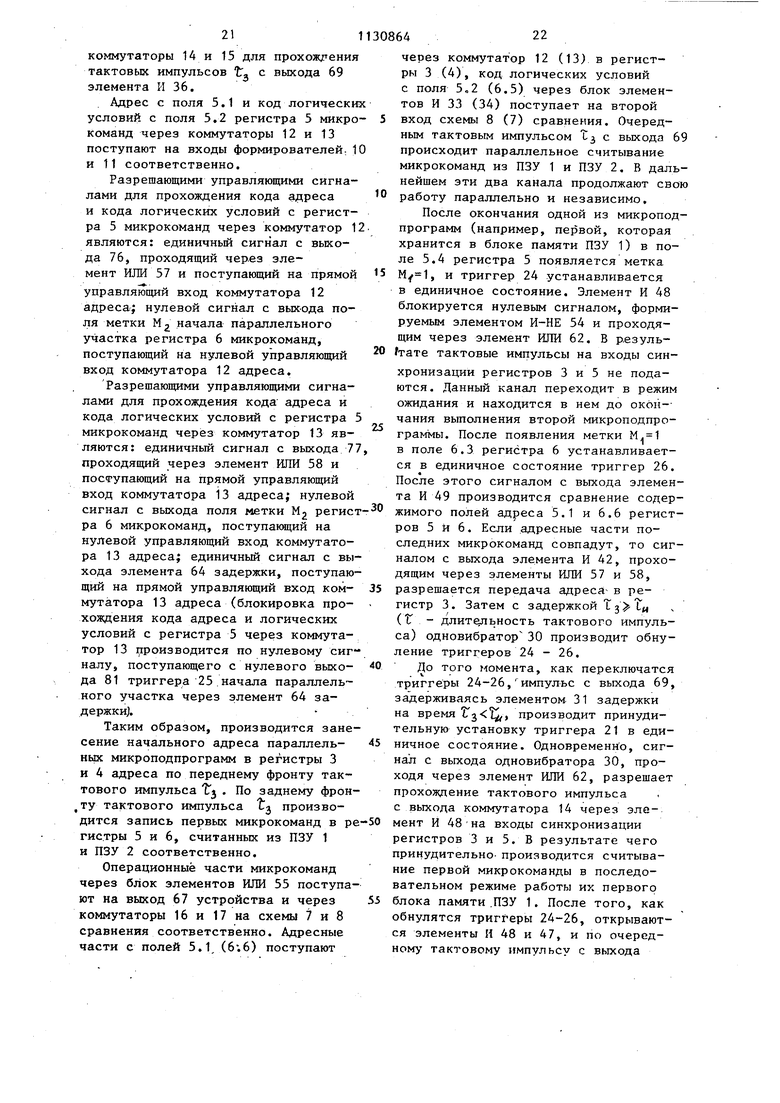

На фиг. 3 показан формат микрокоманд, хранящихся в ПЗУ 1 и ПЗУ 2, которые содержат: поле адреса А, поле микроопераций МО, поле логических условий ЛУ, модифицируемый разряд адреса МР, метки , М и М, (причем:

1, если микрокоманда является последней в параллельной

М. Ч 1 микроподпрограмме;

О, в противном случае; Г 1, если микрокоманда пред- ,, J шествует началу параллельной 2 I микроподпрограммы;

LО, в противном случае;

{1, если после нечетной (четной) должна следовать нечетмая (четная) микрокоманда; О, в противном случае.

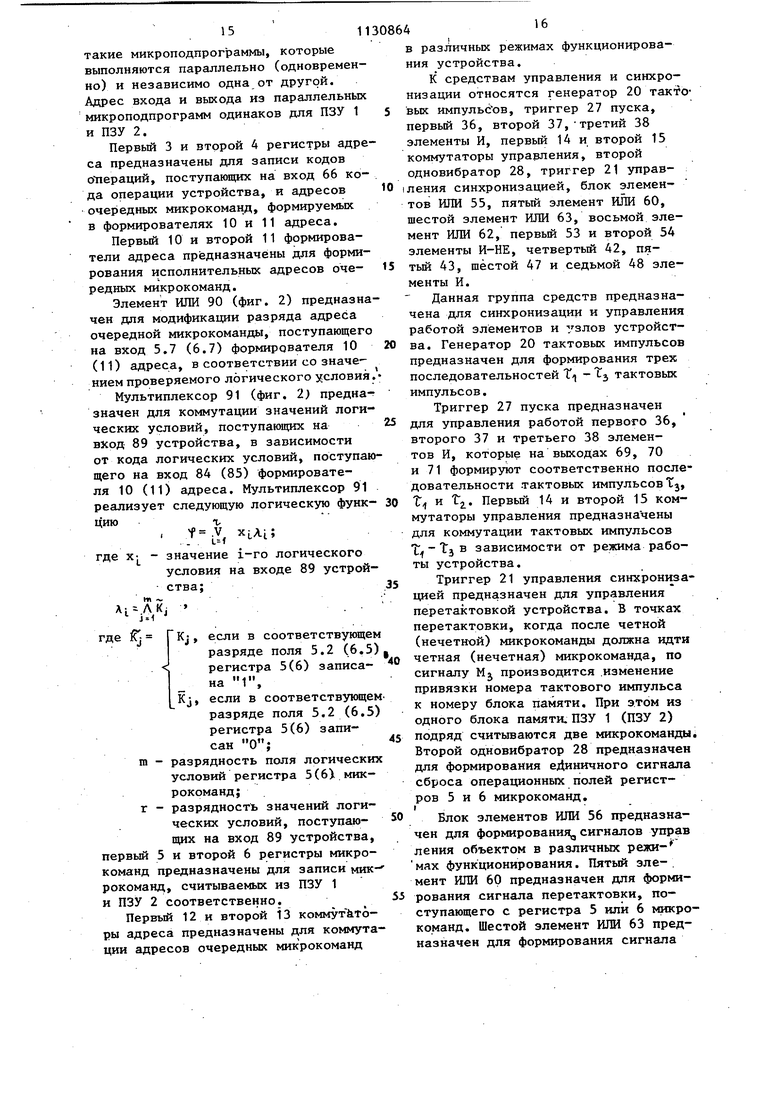

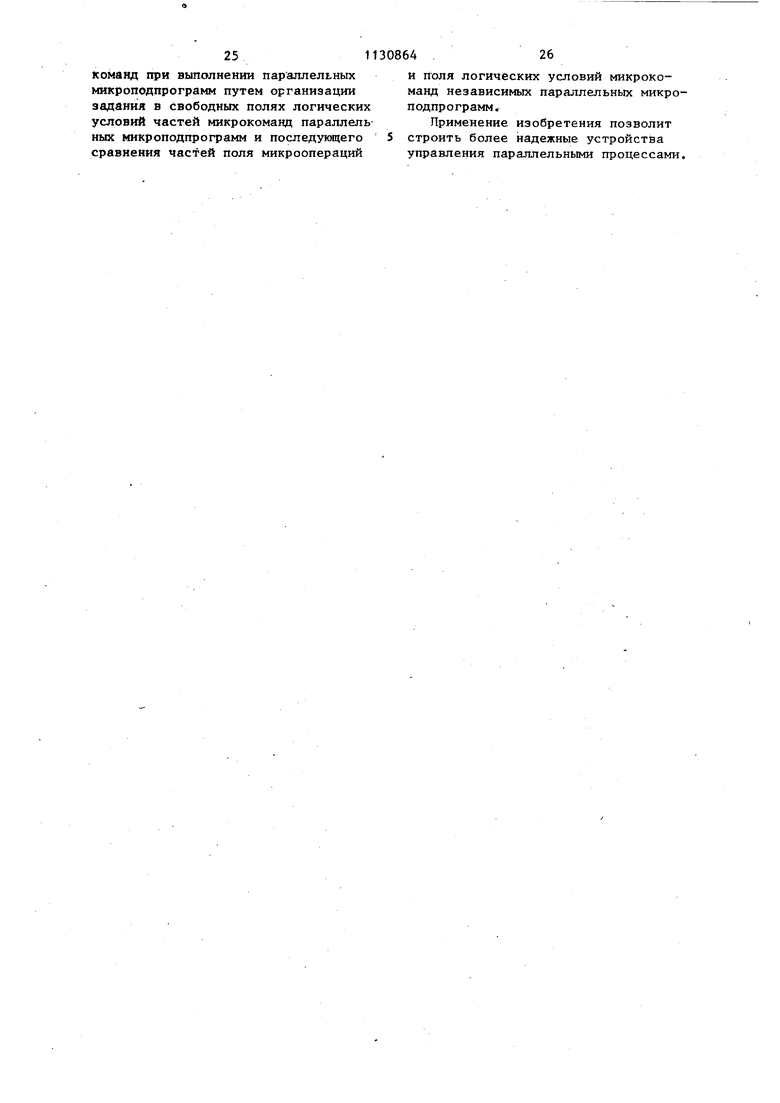

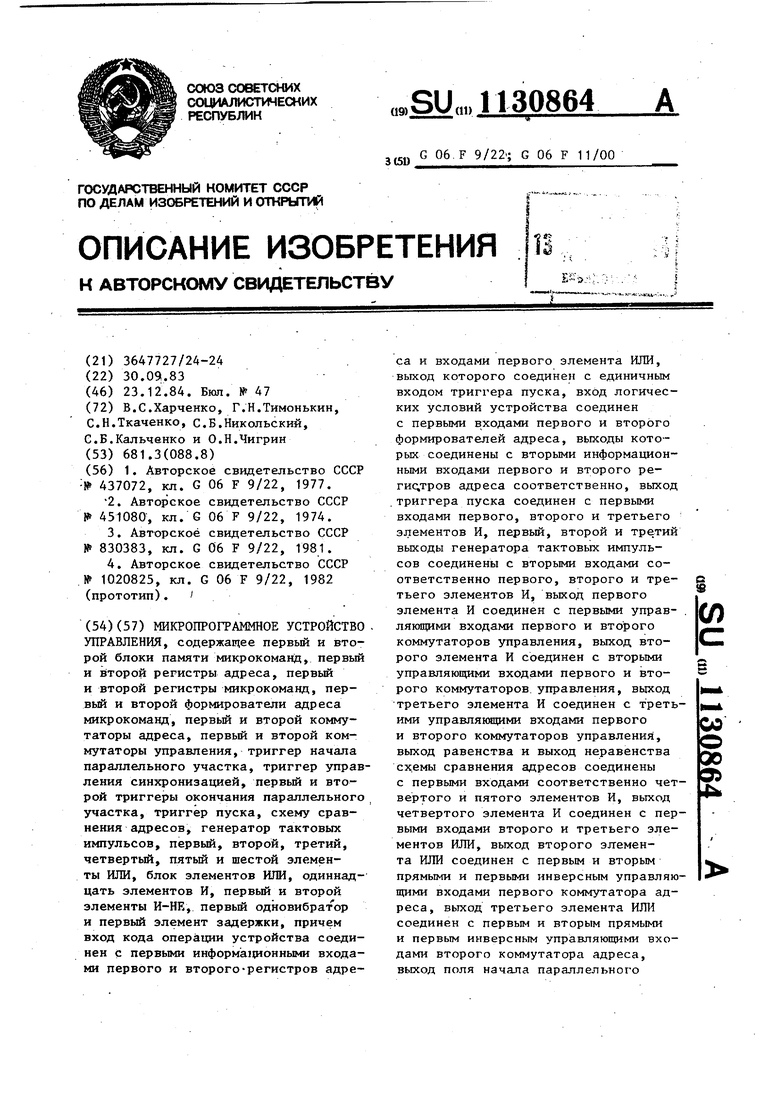

На временной диаграмме (фиг. 5) показаны изменения сигналов на входах-выходах элементов функциональной схемы устройства. Числа на оси ординат указывают номера входов-выходов элементов функциональной схемы устройства. Последовательности синхроимпульсов T/i , Тг, и Тз соответствуют последовательностям синхроимпульсов на выходах 70, 71 и 69 функциональной схемы устройства соответственно. Кроме того, на фиг. 5 приняты следующие сокращения: PAMKi - регистр адреса микрокоманд 3, РМКс - регистр микрокоманд 5. .

Микропрограммное устройство управления содержит .следующие группы технических средств: средства хранения и формирования микрокоманд; Средства управления и синхронизации; средства . управления адресацией и распараллеливанием; средства контроля.

К средствам хранения и формирования микрокоманд относятся ПЗУ 1 и ПЗУ 2, регистры 3 и 4 адреса, регистры 5 и 6 микрокоманд, формирователи 10 и 11 адреса микрокоманд, коммутаторы 12и 13 адреса. Данные средства обеспечивают хранение последовательных И параллельных мик- роподпрограмм, формирование адресов очередных микрокоманд,- а также формирование начальных адресов микроподпрограмм в соответствии с кодом операции.

ПЗУ 1 и ПЗУ 2 предназначены для хранения последовательных и параллельных микроподпрограмм. Параллельными микроподпрограммами назовем такие микроподпрограммы, которые выполняются параллельно (одновременно) и независимо одна от другой. Адрес входа и выхода из параллельных микроподпрограмм одинаков для ПЗУ 1 и ПЗУ 2. Первый 3 и второй 4 регистры адре са предназначены для записи кодов операций, поступающих на вход 66 кода операции устройства, и адресов очередных микрокоманд, формируемых в формирователях 10 и 11 адреса. Первый 10 и второй 11 формирователи адреса предназначены для формирования исполнительных адресов очередных микрокоманд. Элемент ИЛИ 90 (фиг. 2) предназна чен для модификации разряда адреса очередной микрокоманды, поступающего на вход 5.7 (6.7) формирователя 10 (11) адреса, в соответствии со значе нием проверяемого логического условия Мультиплексор 91 (фиг. 2) предназначен для коммутации значений логических условий, поступающих на вход 89 устройства, в зависимости от кода логических условий, поступаю щего на вход 84 (85) формирователя 10 (11) адреса. Мультиплексор 91 реализует следующую логическую функЦИЮ1, t.v xi.Ai; - . L- I где х- - значение 1-го логического условия на входе 89 устройства;л,.лк, . где j Kj, если в соответствующе разряде поля 5.2 (6.5 регистра 5(6) записа- на 1, если в соответствующе разряде поля 5.2 (6.5 регистра 5(6) записанm - разрядность поля логически условий регистра 5(6). микрокоманд;г - разрядность значений логических условий, поступающих на вход 89 устройства, первый 5 и второй 6 регистры микрокоманд предназначены для записи MMKрокоманд, считываемых из ПЗУ 1 и ПЗУ 2 соответственно. . Первый 12 и второй 13 KOMMyTktoры адреса предназначены для коммута ции адресов очередных микрокоманд 1 416 1 в различных режимах функционирования устройства. К средствам управления и синхронизации относятся генератор 20 тактовых импульсов, триггер 27 пуска, первый 36, второй 37,третий 38 элементы И, первый 14 и второй 15 коммутаторы управления, второй одновибратор 28, триггер 21 управления синхронизацией, блок элементов ИЛИ 55, пятый элемент ИЛИ 60, шестой элемент ИЛИ 63, восьмой элемент ИЛИ 62, первый 53 и второй 54 элементы И-НЕ, четвертый 42, пятьй 43, шестой 47 и седьмой 48 элементы И. Данная группа средств предназначена для синхронизации и управления работой элементов и узлов устройства. Генератор 20 тактовых импульсов предназначен для формирования трех последовательностей Т-) - t тактовых импульсов. Триггер 27 пуска предназначен для управления работой первого 36, второго 37 и третьего 38 элементов И, которые на выходах 69, 70 и 71 формируют соответственно последовательности тактовых импульсов Tj, 1 z Первый 14 и второй 15 коммутаторы управления предназначены для коммутации тактовых импульсов Tj в зависимости от режима работы устройства. Триггер 21 управления синхронизацией предназначен для управления перетактовкой устройства. В точках перетактовки, когда после четной (нечетной) микрокоманды должна идти четная (нечетная) микрокоманда, по сигналу Mj производится .изменение привязки номера тактового импульса к номеру блока памяти. При этом из одного блока памяти. ПЗУ 1 (ПЗУ 2) подряд считываются две микрокоманды; Второй одновибратор 28 предназначен для формирования единичного сигнала сброса операционных полей регистров 5 и 6 микрокоманд. I Блок элементов ИЛИ 56 предназначен для формирования, сигналов управ ления объектом в различных режи- мах функционирования. Пятый зле-. мент ИЛИ 60 предназначен для формирования сигнала перетактовки, поступающего с регистра 5 или 6 микрокоманд. Шестой элемент ИЛИ 63 предназначен для формирования сигнала

останова устройства, восьмой элемент ИЛИ 62 предназначен для формирования единичного сигнала, управляющего прохождением тактовых импульсов через элемент И 48 на входы синхронизации регистра 3 адреса и регистра 5 микрокоманд. Первьй 53 и второй 54 элемента И-НЕ предназначены для управления прохождением тактовых импульсов через элементы И 47 и 48. Четвертый элемент И 42 предназначен для формирования управляющего сигнала в момент окончания параллельных микроподпрограмм. Пятый элемент И 43 предназначен для формирования сигнада ошибки в момент окончания параллельных шкроподпрограмм при.несовпадении адресов выхода из параллельного режима, выполнения микроподпрограмм. Шестой 47 и седьмой 48 элементы И предназначены ,цля управления прохождением тактовых импульсоЁ на входы синхронизации регистров 3 и 4 адреса и регистров 5 и 6 микрокоманд

К средствам управления адресацией и распараллеливанием относятся коммутаторы, первый триггер 24 окончания .параллельного участка, триггер 2 начала параллельного участка, второй триггер 26 окончания параллельного ;участка, элемент 29 задержки, одно:вибратор 30, элементы И 46, 49 и 50, элемент.ИЛИ. 59, второй элемент 31 задержки, элемент И 44, которые выполняют функции: управления адресными цепями в зависимости от режима работы и точки микропрограммы; реализации операций распараллеливания при переходе к выполнению параллельных микроподпрограмм} реализации опера ции объединения в точках схождения параллельны: микроподпрограмм«

Элемент 29 задержки предназначен для формирования сигнала сброса триггеров 24 - 26 посл.е выхода из параллельного выполнения микроподпрограмм Адрес выхода записывается в регистр адреса по тактовому импульсу, проходящему через элемент И 48. Разрешающим сигналом для прохождения тактового импульса через элемент И 48 является единичный сигнал, формируемый первьм одновибратором 30 и проходя щий через элемент ИЛИ 62. Затем производится перевод триггеров 24 - 26 в нулевое (исходное) состояние.

Триггер 25 начала параллельного участка предназначен-для управления

работой устройства при одновременном выполнении параллельных микроподпрограмм.

Первый 24 и второй 26 триггеры окончания параллельных участков предназначены для блокировки прохождения тактовых импульсов на входы синхронизации регистров 3,5 и 4,6 после выполнения параллельных участков,

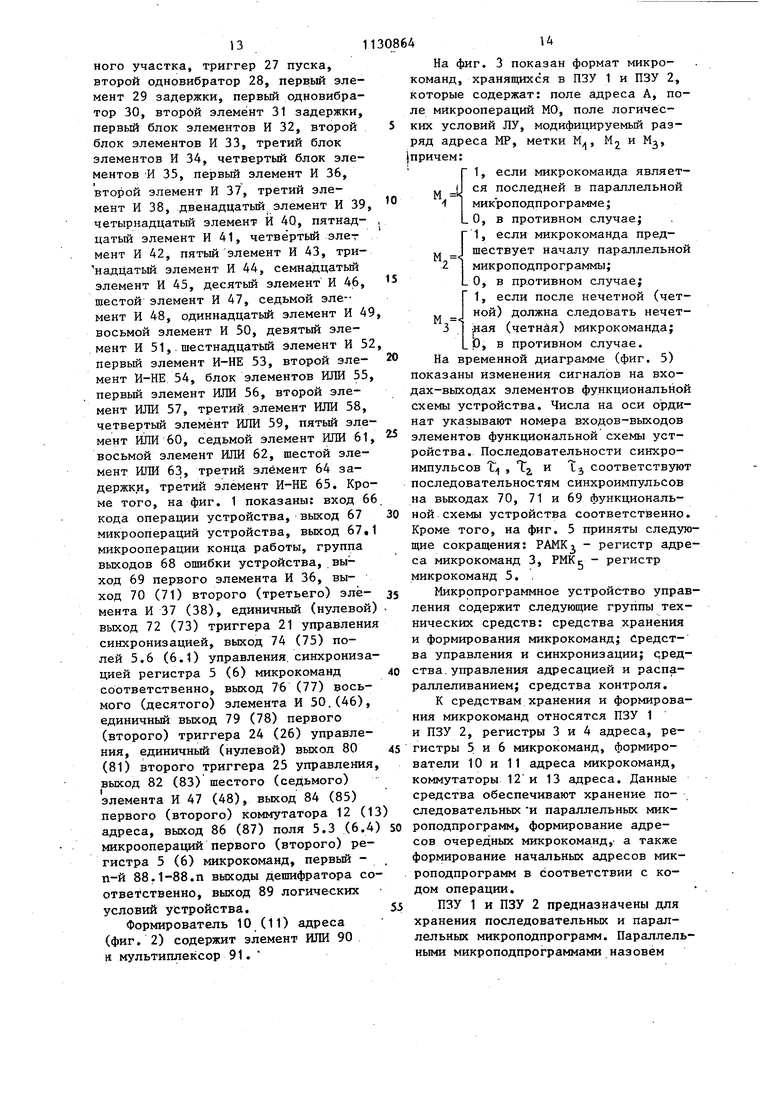

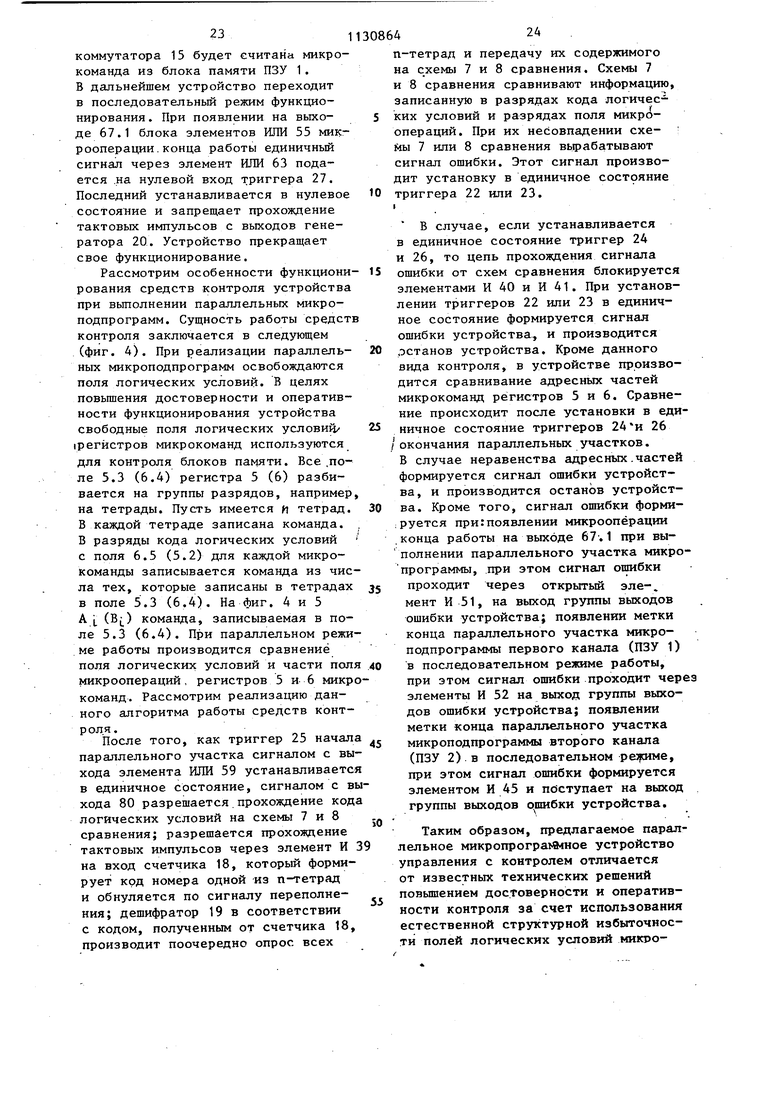

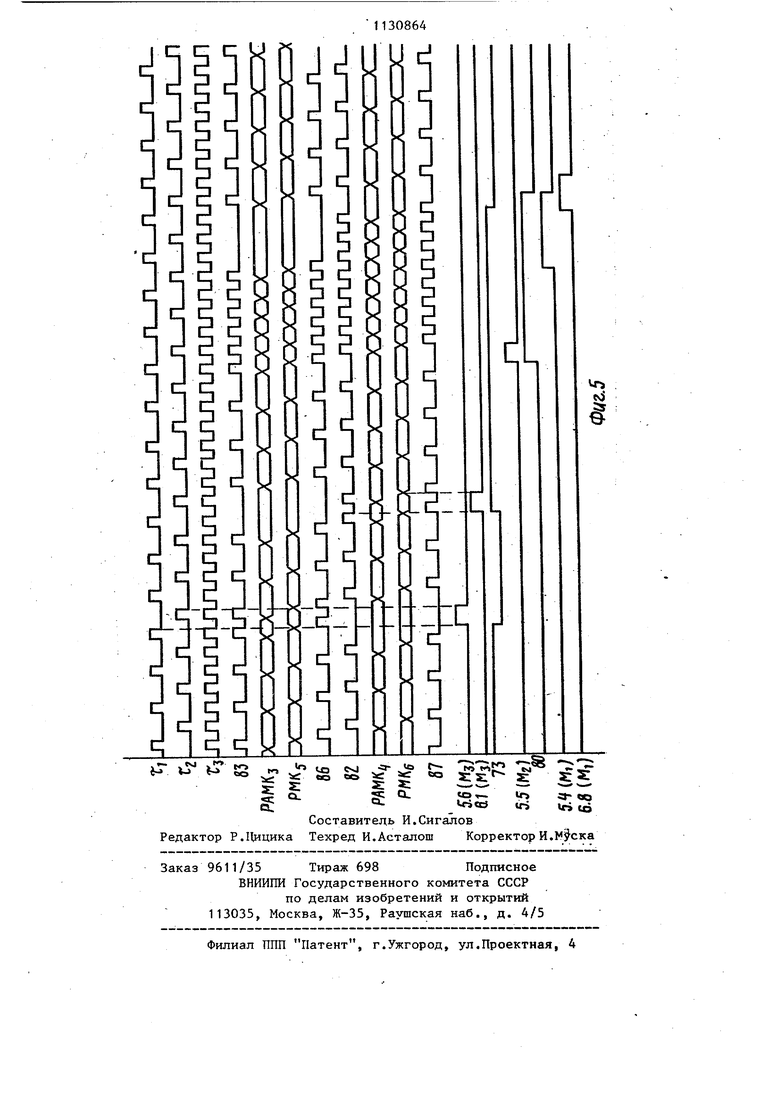

К средствам контроля устройства , относятся схемы 7 и 8 сравнения операционных частей, схема 9 сравнения адресов, коммутаторы 16 и 17 операционных частей, счетчик 18, дешифратор 19, первый и второй триггеры 22 и 23 ошибок, первый-четвертьш блоки 32-35 элементов И, элементы И 39, 40, 41, 42, 43, 45, 51 и 52 элемент ИЛИ 61 и элемент И-НЕ 65. Указанные элементы осуществляют оперативный контроль функционирования устройства при выполнении параллельных микроподпрограмм.

Схема 9 сравнения адресов микрокоманд производит сравнение адресных частей микрокоманд, которые являются последними в параллельных микроподпрограммах, и формирует сигнал ошибки при их несовпадении. Схемы 7 и 8 сравнения операционных частей микрокоманд производят в па;раллельном режиме работы устройства |сравнение групп разрядов операционных частей микрокоманд из одного канала с кодами, записанными в свободньк разрядах логических условий другого канала. При несовпадении контролируемых разрядов происходит формирование сигнала ошибки и останов устройства. Элемент И 51 формирует сигнал ошибки при вьщаче операций конца работы при выполнении параллельньк микроподпрограмм. Элемент И 52 формирует сигнал ошибки при считывании метки М, из ПЗУ 1 в параллельном режиме, элемент И 53 формирует сигнал ошибки при считывании метки Mj из ПЗУ 2 в параллельном режиме. Счетчик 18 и дешифратор 19 предназначены для формирования номеров групп разрядов операционных частей и управления коммутаторов 16 и 17 операционных частей.

Устройство функционирует в следующих режимах: выполнения последовательных микроподпрограмм и выпол нения параллельных микроподпрограмм. 19 .1 Режим выполнения последовательных микроподпрограмм. В исходном состоянии все триггеры и регистры устройства находятся в нулевом состоянии.- После прихода кода операции начального адреса микроподпрограммы на вход 66 устройства сигнал с выхода элемента ИЛИ 56 устанавливает триггер 27 в единичное состояние, который разрешает прохождение последовательностей тактовых импульсов Гз , Tj и T/j через элементы И 36 - 38 соответственно. При этом, перед считыванием очередной микрокоманды тактовый импульс с выхода 69 подается на одновибратор 28, на выходе которого формируется единичный сигнал, производящий обнуление операционных полей регистров 5 и, 6 микрокоманд. Тактовый импульс с выхода 70 (71) элемента И 37 (38) через коммутатор 14. (15) и элемент И 48 .(47) подается на входы синхронизации регистров 3 и 5 (4 и 6), причем запис информации в регистр 3 (4) происходит по переднему фронту тактового импульса, а в регистр 5 (6) - по заднему фронту тактового импульса. По переднему фронту тактового импульса ) происходит обращение к блоку памяти ПЗУ 1 (ПЗУ 2) микрокоманд в соответствии с адресом мик рокоманды, записанным в регистре 3 (4) адреса микрокоманд (РАМК). По заднему фронту t Ci) тактового импульса происходит запись микрокоманды из блока йамяти ПЗУ 1 (ПЗУ 2) микрокоманд в регистр 5 (6) микрЬ-команд. Адресная часть микрокоманды поля 5.1 () регистра 5 (6) подается через коммутатор 13 (12) на вход формирователя 11 (10) адреса микрокоманд. Аналогично, код.логиче ких условий с выхода 5.2(6.5) регис ра 5 (6) через блок элементов И 32 (35) через коммутатор 13 (12) подае ся на вход формирователя 11 (10) ад реса микрокоманд. .В формирователе адреса (фиг. 3) микрокоманд, код логических условий и логические условия с выхода 89 подаются на мультиплексор 91. На вход 6.7 (5.7) форми рователя 11 (10) адреса микрокоманд поступает модифицируемый разряд адреса, который формируется на выходе элемента ИЛИ 90 и поступает на выхо формирователя 11 (10) адреса микро4команд вместе с немодифицируемыми разрядами адреса. Адрес очередной микрокоманды с зыхода формирователя .11(10) адреса подается на информационный вход D2 регистра 4 (3). По очередному тактовому импульсу происходит обращение и считывание информации с ПЗУ 2 (ПЗУ 1). В последующем работа устройства происхо ит аналогично рассмотренным тактам. Если после нечетной (четной) микрокоманды из блока памяти 1 (2) вновь должна быть считана нечетная (четная) микрокоманда, то в поле 5.6 (6.1) этой микрокоманды записывается единица, по которой затем триггер 21 устанавливается в единичное состояние. В результате этого на входе 72 коммутатора 14 (15) появляется разрешающий сигнал, который разрешает прохождение тактового импульса 2. () с выхода 71 (70) элемента И 38 (37) через коммутатор 14 (15) и элемент И 48 (47) на регистры 3 и 5 (4 и 6). Таким образом, из ПЗУ 1 (ПЗУ 2) происходит считывание подряд двух микрокоманд и перетактовка, т.е. привозка синхроимпульсов к соответствующим регистрам без потери одного микротакта. При этом адрес и код логических условий следующей нечётной (четной) микрокоманды с полей 5.1 и 5.2 (6.6 и 6.5) регистра 5 (6) поступает через открытый сигналом с выхода элемента ИЛИ 57 (58) коммутатор 12 (13) в формирователь адреса 10 (11). При появлении очередной метки в поле 5.6 (6.1) вновь осуществляется перетактовка, и из одного блока памяти подряд считьтаются две микрокоманды. Затем работы продолжается аналогично описанным тактам работы: считывание микрокоманд производится по очереди из одного и из другого блока памяти. При появлении метки в поле 5.5(6.2) регистра 5 (6) устройство переходит во второй режим работы. Режим выполнения параллельных микроподпрограмм. При появлении метки М« на выходе 5.5 регистра 5 формируется единичный сигнал, который проходит через элемент ИЛИ 59 и устанавливает триггер 25 в единичное состояние, открывая элементы И 50 и И 46, а также коммутаторы 14 и 15 для прохождения тактовых импульсов t с выхода 69 элемента И 36. Адрес с поля 5.1 и код логических условий с поля 5.2 регистра 5 микро-5 команд через коммутаторы 12 и 13 поступают на входы формирователей; 1 и 11 соответственно. Разрешающими управляющими сигналами для прохождения кода адреса и кода логических условий с регистра 5 микрокоманд через коммутатор 1 являются: единичный сигнал с выхода 76, проходящий через элемент ИЛИ 57 и поступающий на прямой управляющий вход коммутатора 12 адреса; нулевой сигнал с вых-ода поля метки М начала параллельного участка регистра 6 микрокоманд, поступающий на нулевой управляющий вход коммутатора 12 адреса. Разрешающими управляющими сигналами для прохождения кода адреса и кода логических условий с регистра микрокоманд через коммутатор 13 являются: единичный сигнал с выхода 7 проходящий через элемент ИПИ 58 и поступающий на прямой управляющий вход коммутатора 13 адреса; нулевой сигнал с выхода поля метки Mj регис ра 6 микрокоманд, поступакнций на нулевой управляющий вход коммутатора 13 адреса; единичный сигнал с вы хода элемента 64 задержки, поступаю щий на прямой управляющий вход ком- мутатора 13 адреса (блокировка прохождения кода адреса и логических условий с регистра 5 через коммутатор 13 1;1роизводится по нулевому сиг налу, поступающего с нулевого выхода 81 триггера 25.начала параллельного участка через элемент 64 задержки). Таким образом, производится зане сение начального адреса параллельньк микроподпрограмм в регистры 3 и 4 адреса по переднему фронту тактового импульса fj . По заднему фрон ту тактового импульса t производится запись первых микрокоманд в р гистры 5 и 6, считанных из ПЗУ 1 и ПЗУ 2 соответственно. Операционныё части микрокоманд через блок элементов ИЛИ 55 поступа ют на выход 67 устройства и через коммутаторы 16 и 17 на схемы 7 и 8 сравнения соответственно. Адресные части с полей 5.1, (6;6) поступают через коммутатор 12 (13) в регистры 3 (4), код логических условий с поля 5,2 (6.5) через блок элементов И 33 (34) поступает на второй вход схемы 8 (7) сравнения. Очередным тактовым импульсом з с выхода 69 происходит параллельное считывание микрокоманд из ПЗУ 1 и ПЗУ 2. В дальнейшем эти два канала продолжают свою работу параллельно и независимо. После окончания одной из микроподпрограмм (например, первой, которая хранится в блоке памяти ПЗУ 1) в поле 5.4 регистра 5 появляется метка , и триггер 24 устанавливается в единичное состояние. Элемент И 48 блокируется нулевым сигналом, формируемым элементом И-НЕ 54 и проходящим через элемент ИПИ 62. В резуль/тате тактовые импульсы на входы синхронизации регистров 3 и 5 не подаются. Данный канал переходит в режим ожидания и находится в нем до OKOII- чания выполнения второй микроподпрограммы. После появления метки в поле 6.3 регистра 6 устанавливается в единичное состояние триггер 26. После этого сигналом с выхода элемента И 49 производится сравнение содержимого полей адреса 5.1 и 6.6 регистров 5 и 6. Если адресные части последних микрокоманд совпадут, то сигналом с выхода элемента И 42, проходящим через элементы ИЛИ 57 и 58, разрешается передача адреса- в регистр 3. Затем с задержкой Тз Тц (Т - длит ьность тактового импульса) одновибратор 30 производит обнуление триггеров 24 - 26. До того момента, как переключатся триггеры 24-26,импульс с выхода 69, задерживаясь элементом 31 задержки на время з) производит принудительную установку триггера 21 в едияичное состояние. Одновременно, сигнал с выхода одновибратора 30, проходя через элемент ИЛИ 62, разрешает прохождение тактового импульса с вьгхода ком утатора 14 через элемент И 48на входы синхронизации регистров 3 и 5. В результате чего принудительно- производится считывание первой микрокоманды в последовательном режиме работы их первого блока памяти .ПЗУ 1. После того, как обнулятся триггеры 24-26, открываются элементы И 48 и 47, и по очередному тактовому импульсу с выхода 23 коммутатора 15 будет считана микрокоманда из блока памяти ПЗУ 1. В дальнейшем устройство переходит в последовательный режим функционирования. При появлении на выходе 67.1 блока элементов ИЛИ 55 микрооперации, конца работы единичный сигнал через элемент ИЛИ 63 подается .на нулевой вход триггера 27. Последний устанавливается в нулевое состояние и запрещает прохождение тактовых импульсов с выходов генератора 20. Устройство прекращает свое функционирование. Рассмотрим особенности функциони рования средств контроля устройства при вьтолнении параллельных микроподпрограмм. Сущность работы средст контроля заключается в следующем (фиг. 4). При реализации параллельных микроподпрограмм освобождаются поля логических условий. В целях повьппения достоверности и оперативности функционирования устройства свободные поля логических условий/ 1регйстров микрокоманд используются для контроля блоков памяти. Все .поле 5.3 (6.4) регистра 5 (6) разбивается на группы разрядов, например на тетрады. Пусть имеется ц тетрад. В каждой тетраде записана команда. В разряды кода логических условий с поля 6.5 (5.2) для каждой микрокоманды записывается команда из чис ла тех, которые записаны в тетрадах в поле 5.3 (6.4). На Лиг. 4 и 5 А i (Вц) команда, записываемая в поле 5.3 (6.4). При параллельном режи ме работы производится сравнение поля логических условий и части пол микроопераций, регистров 5 и 6 микр команд. Рассмотрим реализацию данного алгоритма работы средств контроля. После того, как триггер 25 начал параллельного участка сигналом с вы хода элемента ИЛИ 59 устанавливаетс в единичное состояние, сигналом с в хода 80 разрешается.прохождение код логических условий на схемы 7 и 8 сравнения; разрешается прохождение тактовых импульсов через элемент И на вход счетчика 18, который формирует код номера одной из п-тетрад и обнуляется по сигналу переполнения; дешифратор 19 в соответствии с кодом, полученным от счетчика 18, производит поочередно опрос всех 4 п-тетрад и передачу их содержимого на схемы 7 и 8 сравнения. Схемы 7 и 8 сравнения сравнивают информацию, записанную в разрядах кода логических условий и разрядах поля микроопераций. При их несовпадении схейы 7 или 8 сравнения вырабатывают сигнал ошибки. Этот сигнал производит установку в единичное состояние триггера 22 или 23. I В случае, если устанавливается в единичное состояние триггер 24 и 26, то цепь прохождения сигнала ошибки от схем сравнения блокируется элементами И 40 и И 41. При установлении триггеров 22 или 23 в единичное состояние формируется сигнал ошибки устройства, и производится .останов устройства. Кроме данного вида контроля, в устройстве производится сравнивание адресных частей микрокоманд регистров 5 и 6. Сравнение происходит после установки в единичное состояние триггеров 24и 26 окончания параллельных участков. В случае неравенства адресных.частей формируется сигнал ошибки устройства, и производится останов устройства. Кроме того, сигнал ошибки форми;руется при:появлении микрооперации .конца работы на выходе 67, 1 при вы- полнении параллельного участка микро программы, при этом сигнал ошибки проходит через открытый эле-, мент И 51, на выход группы выходов ошибки устройства; появлении метки конца параллельного участка микроподпрограммы первого канала (ПЗУ 1) в последовательном режиме работы, при этом сигнал ошибки проходит через элементы И 52 на выход группы выходов ошибки устройства; появлении метки конца параллельного участка микроподпрограммы второго канала (ПЗУ 2) . в последовательном , при этом сигнал ошибки формируется элементом И 45 и пбступает на выход группы выходов ршибки устройства. Таким образом, предлагаемое паралельное микропрогра1в4ное устройство управления с контролем отличается от известных технических решений повышением достоверности и оперативности контроля за счет использования естественной структурной избыточности полей логических условий микро25 113086426

команд при выполнении параллельныхи поля логических условий микрокомикроподпрограмм путем организацииманд независимых параллельных микрозадания в свободных полях логическихподпрограмм,

условий частей микрокоманд параллельПрименение изобретения позволит

ных микроподпрограмм и последующего5 строить более надежные устройства

сравнения частей поля микрооперацийуправления параллельными процессами.

57(6.7;,

8(85)

Операц.ч. ЛУ

Фиг. 2

Фиг.3

Операц. ч. л.У

ФигМ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1972 |

|

SU451080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-09-30—Подача