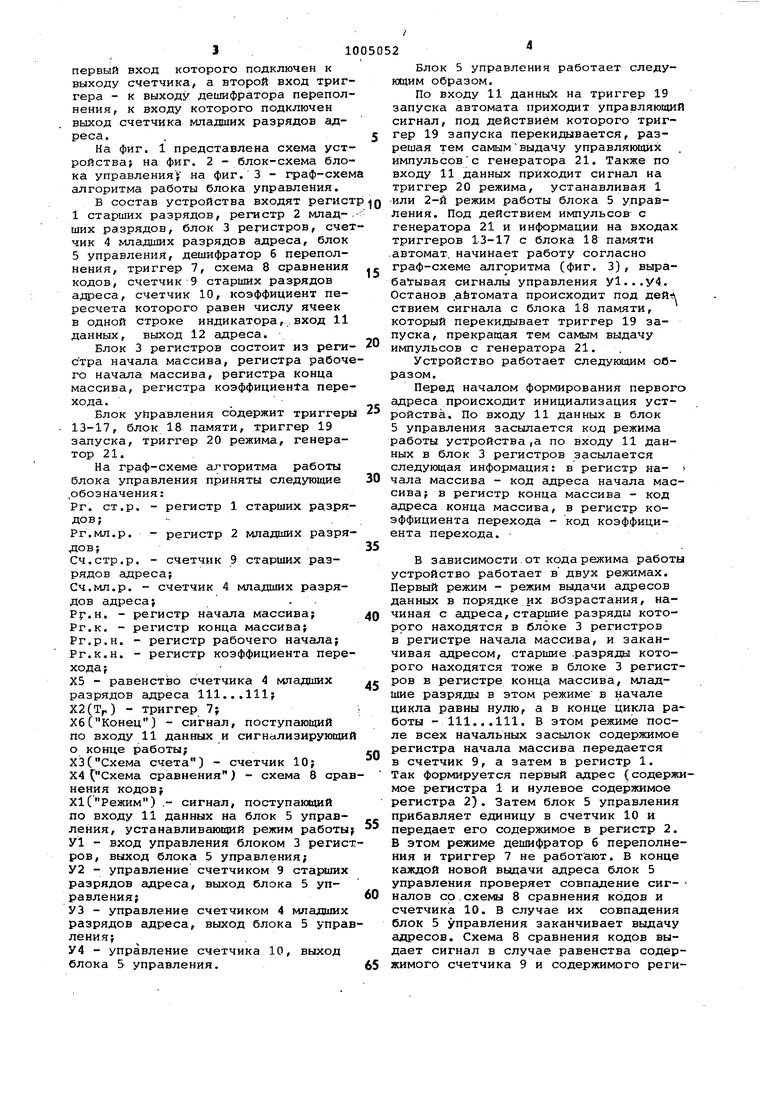

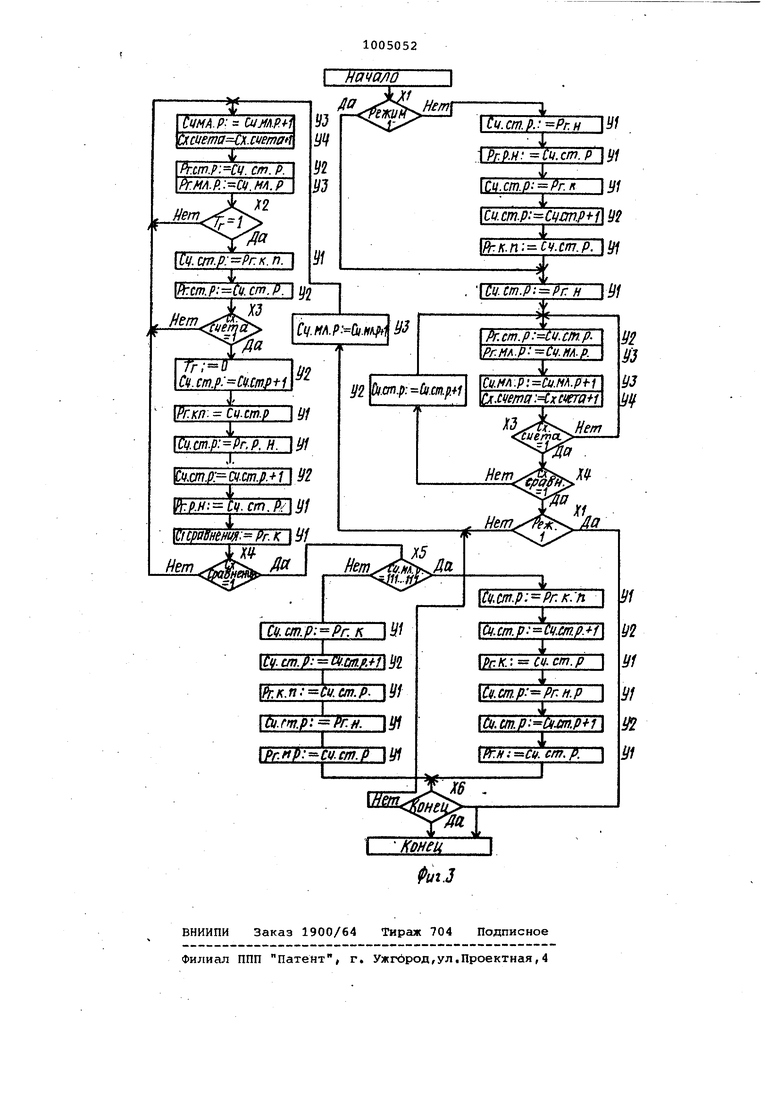

первый вход которого подключен к выходу счетчика, а второй вход триг гера - к выходу дешифратора перепол нения, к входу которого подключен выход счетчика младших разрядов адреса. На фиг. 1 представлена схема уст ройства на фиг. 2 - блок-схема бло ка управления на фиг. 3 - граф-схе алгоритма работы блока управления. В состав устройства входят регис 1 старших разрядов, регистр 2 младших разрядов, блок 3 регистров, сче чик 4 младших разрядов адреса, блок 5 управления, дешифратор б переполнения, триггер 7, схема 8 сравнения кодов, счетчик 9 старших разрядов адреса, счетчик 10, коэффициент пересчета которого равен числу ячеек в одной строке индикатора,.вход 11 данных, выход 12 адреса. Блок 3 регистров состоит из реги стра начсша массива, регистра рабоч го начала массива, регистра конца массива, регистра коэффициента пере хода. Блок управления содержит триггер 13-17, блок 18 памяти, триггер 19 запуска, триггер 20 режима, генератор 21. На граф-схеме атторитма работы блока управления приняты следующие .обозначения: Рг. ст.р. - регистр 1 старших ра.зря дов; -. Рг.мл.р. - регистр 2 младших разря дов; - счетчик 9 старших разСч.стр.р. рядов адреса; Сч.мл.р. - счетчик 4 мпадших разрядов адреса}. Pf.н. - регистр начала массива; Рг.к. - регистр конца массива; Рг.р.н. - регистр рабочего начала; Рг.к.н. - регистр коэффициента пере хода; Х5 - равенство счетчика 4 младших разрядов адреса 111...111; Х2(Тр) - триггер 7; Х6С Конец) - сигнал, поступающий по входу 11 данных и сигнализирующи о конце работы; Х3(Схема счета) - счетчик 10; Х4 (Схема сравнения) - схема 8 сра нения КОДОВ; XIс Режим) .- сигнал, поступающий по входу 11 данных на блок 5 управления, устанавливающий режим работы У1 - вход управления блоком 3 регис ров, выход блока 5 управления; У2 - управление счетчиком 9 старших разрядов адреса, выход блока 5 управления;УЗ - управление счетчиком 4 мпадших разрядов адреса, выход блока 5 упра ления; У4 - управление счетчика 10, выход блока S управления. 1 2 Блок 5 управления работает следующим образом. По входу 11 данных на триггер 19 запуска автомата приходит управляющий сигнал, под действием которого триггер 19 запуска перекидывается, разрешая тем самымвыдачу управляющих импульсов с генератора 21. Также по входу 11 данных приходит сигнал иа триггер 20 режима, устанавливая 1 или 2-й режим работы блока 5 управления. Под действием импульсов с генератора 21 и информации на входах триггеров 13-17 с блока 18 пагляти .автомат, начинает работу согласно граф-схеме алгоритма (фиг. 3), вырабатывая сигналы управления У1...у4. Останов .автомата происходит под дей ствием сигнала с блока 18 памяти, который перекидывает триггер 19 запуска, прекращая тем самым выдачу импульсов с генератора 21. Устройство работает следующим образом. Перед началом формирования первого адреса происходит инициализация устройства. По входу 11 данных в блок 5 управления засьолается код режима работы устройства ,а по входу 11 данных в блок 3 регистров засылается следукицая информация: в регистр на- чала массива - код адреса начала массива; в регистр конца массива - код адреса конца массива, в регистр коэффициента перехода - код коэффициента перехода. В зависимости.от кода режима работы устройство работает в двух режимах. Первый режим - режим вьвдачи адресов данных в порядке их вс5зрастания, начиная с адреса,старшие разряды которого находятся в блоке 3 регистров в регистре начала массива, и заканчивая адресом, старшие .разряды которого находятся тоже в блоке 3 регистров в регистре конца массива, младшие разряды в этом режиме в начале цикла равны нулю, а в конце цикла работы - 111...111. В этом режиме после всех начальных засылок содержимое регистра начала массива передается в счетчик 9, а затем в регистр 1. Так формируется первый адрес (содержимое регистра 1 и нулевое содержимое регистра 2). Затем блок 5 управления прибавляет единицу в счетчик 10 и передает его содержимое в регистр 2. В этом режиме дешифратор б переполнения и триггер 7 не работают. В конце каждой новой выдачи адреса блок 5 управления проверяет совпсщение сиг- налов со схемы 8 сравнения кодов и счетчика 10. В случае их совпгщения блок 5 управления заканчивает выдачу адресов. Схема 8 сравнения кодов выдает сигнал в случае равенства содержимого счетчика 9 и содержимого регистра конца массива. Счетчик 10 выдает сигнал при перейолненни. Второй режим - это циклический режим выдачи адреса, причем порядок выдачи старших разрядов адреса задан коэффициентом перехода в массив. После инициализации блок 5 управ ления передает содержимое регистра начала массива в регистр рабочего на чала массива череэ счетчик 9), а содержимое регистра конца массива пе редает в счетчик 9, прибавляет едини цу и помещает в регистр коэффициента перехода. Затем блок 5 управления управляет формированием адреса как в первом режиме, так и после того как сигнал со счётчика 10 совпадает с сигналом со схемы 8 сравн ения кодов, блок 5 управления прибавляет единицу к счетчику 4 (код в счетчике 4равен 000. ..001) и передает содержи мое счетчика 4 в регистр 2. Затем блок 5 управления помещает в счетчик 9 содержимое регистра начета массива и передает его сразу в регистр 1. Теперь в регистре 1 находится содержимое регистра начала мас сива, в регистре 2 - код 000...001, так формируется первый адрес этого цикла. Затем в счетчик 10 и в счетчик 4 прибавляется единица и содержи мое его передается в регистр 2. Соде жимое регистра 1 остается неизменным пока на блок 5 управления не поступиг сигнал с триггера 7, Триггер 7 опрокидывается .сигналом с дешифратора 6 переполнения, который вырабатывается при переполнении счетчика 4. При опрокидывании триггера 7 блок 5 управления передает содержимое регистра коэффициента перехода счетчик 9, оттуда - в регистр 1.Триггер 7 возвращается в исходное состояние сигналом со счетчика 10. После возврата триггера 7 в исходное состояние блок 5 управления прибавляет к содержимому счетчика 9 единицу и помещает этот код в регистр коэффициента перехода. После этого передает содержимое регистра рабочего начала в счетчик 9, прибавляет единицу и помещает -в регистр рабочего начала. Этими действиями происходит переход к новому участку массива, а также модификация коэффициента пере.хода.. Аналогично предыдущему циклу бло 5управления передает содержимое регистра рабочего канала в счетчик 9, оттуда в регистр 1, а содержимое счетчика 4 в регистр 2. После этого в счетчик 10 и в счетчик 4 прибавляется единица с передачей содержимого счетчика каждый раз в регастр В момент формирования каждого нового адреса блок 5 управления произ водит проверку конца массива. Для этого в счетчик 9 помещается содержи ое регистра рабочего начала и вызывается содержимое регистра конца массива, при этом схема 8 сравнения кодов сравнивает эти два кода и, в случае ихравенства, выдает сигнал . управления на блок 5 уп;равления. Если в этот же момент присутствует сигнал со счетчика 10, то блок 5 управления заканчивает цикл выдачи адреса. После этого, если содержимое счетчика 4 не равно коду 111...111, содержимое регистра начала массива передается в регистр рабочего начала (через счетчик 9), содержимое регистра конца массива передается в счетчик 9, там к нему прибавляется единица и содержимое его передается в регистр коэффициента перехода. Затем в счётчик 4 прибавляется единица и его содержимое становится равным двойке (000...001). Блок 5 управления начинает новый цикл выдачи адреса, но уже не с первого, а с второго номера кода. Так повторяется цикл за циклом, причем начало каждого нового цикла осуществляется с нового адреса, отличающегося от предыдущего на единицу. Если содержимое счетчика 4 после окончания одного из циклов сте.новитгся равным коду 11Д...111, блок 5 управления передаёт содержимое регистра рабочего начала в счетчик 9, прибавляет единицу и помещает этот код в регистр начала массива (этот код является началом нового массива), а также содержимое регистра коэффициента перехода передает в регистр конца массива, производя тем самым модификацию конца массива. После этих передач блок 5 управления прибавляет единицу к. содержимому счетчика 4 (содержимое его становится равным нулю) и все начинается сначала, цикл за циклом. Выход и циклическая выдача адреса осуществляются извне. По входу 11 данных в устройство засылается команда нового режима или останова. Таким образом, данное техническое решение позволяет производить циклическое считывание (записывание) массива информации со сдвигом и с заранее заданным коэффициентом перехода внутри массива, т.е. устройство кро ме функции вывода массива данных с начального адреса до конечного смо-, жет работать в режиме бегущей строки . Формула изобретения Устройство ёщресации для канала прямого доступа к памяти, состоящее из регистров старших и младших разрядов, счетчиков старших .и младших разрядов адреса, счетчика и блока управления, первый выход блока управления соединен через счетчик млад ших разрядов адреса с входом регистра младших разрядов, второй выход с первым входом счетчика старших раз рядов адреса, выход которого соединен с входом регистра .старших разрядов, третий выход - с входом счетчика, выход которого подключен к пер вому а,ходу блока управления, второй вход которого соединен с входом данных устройства, выходы регистров старших и младших разрядов являются выходами адреса устройства, от л и чающееся тем, что, с целью расширения Функциональных возможностей за счет обеспечения работы устройства в режиме бегущей строки, в устройство введены дешифратор переполнения, триггер, схема сравнения кодов, блок регистров, первый вход которого подключен к входу данных устройства, второй вход блока регист ров подключен к четвертому выходу блока управления, третий вход блока регистров - к выходу счетчика старших разрядов адреса и к первому входу схемы сравнения кодов, второй вход которой и второй вход счетчика старишх разрядов ащреса подключены к выходу блока регистров, а выход схемы сравнения кодов подключен к третьему входу блока управления, к четвертому входу которого подсоединен выход триггера, первый вход которого подключен к выходу счетчика, а второй вход триггера - к выходу дешифратора переполнения, к входу которого подключен выход счетчика младших разрядов адреса. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 691840, кл. G, Об F 3/04, 1979. 2.Экспресс-информация, Сер. RJчислительная технк ка, 1978, 37, реф. 225 (прототип).

w

$

мят

H

/5

с

я I

л

«

И

J)

f7

ffWji

-/

-/ .

ЗОПЛСК

r

IS

Л

r

2

Я

начало

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации памяти | 1984 |

|

SU1160410A1 |

| Устройство адресации индикатора | 1984 |

|

SU1320807A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

Авторы

Даты

1983-03-15—Публикация

1981-08-26—Подача