Изобретние относится к цифровой вычислительной технике и может примняться для формирования адресов буфеной памяти систем ввода-вывода инфомации многоканальных измерительных комплексов.

Известно устройство формирования адреса, содержащее блок передачи даных, блок управления, формирования адреса, генераторы констант и два сумматора р} .

. Недостатком этого устройства является большой объем оборудования. Наиболее близким по технической сущности к изобретению является уст ройство адресации для кайала прямого доступа к памяти, содержащее регистры старших и младших разрядов адреса, счетчики старших и младших разрядов адреса, схему сравнения кодов, счетчик, дешифратор переполнения, регистр начала и регистр конца массива, блок управления, блок регистров и триггер, при этом выходы разрядов регистра начала массива соединены с установочными входами счетчика старших разрядов адреса, а выходы разрядов регистра конца массива соединены с первой группой соответствующих входов схемы сравнения кодов, входы регистра старших разрядов адреса и второй группы соответствующих входов схемы сравнения кодов попарно объединены и

подключены к выходам разрядов счетчика старших разрядов адреса, а выходы регистра младших разрядов соединены с выходами разрядов счетчика младших разрядов адреса, первый выход блока управления соединен через счетчик младших разрядов адреса с входом регистра младших разрядов, второй выход - с первым входом счетчика старших разрядов адреса, третий выход - с входом счетчика, выход которого подключен к первому входу блока управления, второй вход которого соединен с входом данных устройства, первый вход блока регистров подключен к входу данных устройства, второй вход блока регистров подключен к четвертому выходу блока управления, третий вход блока регистров - к выходу счетчика старших разрядов адреса, выход схемы сравнения кодов подключей к третьему входу блока управления, к четвертому входу которого подключен выход триггера, пер102

Ечьй ВХОД которого подключен к выходу счетчика, а второй вход триггера - к выходу деиифратора переполнения, к входу которого подключен выход счетчика младших разрядов адреса 2 .

Недостатком известного устройства являются большие аппаратурные затраты.

Цель изобретения - сокраш;ение аппратурных затрат.

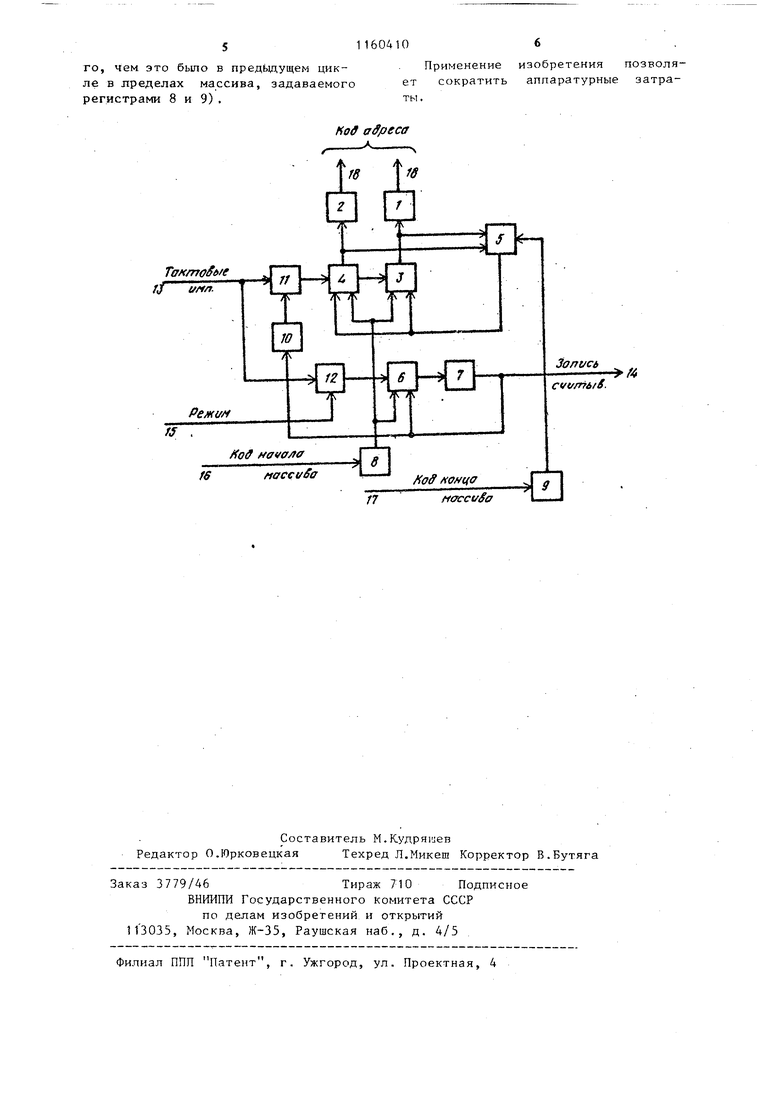

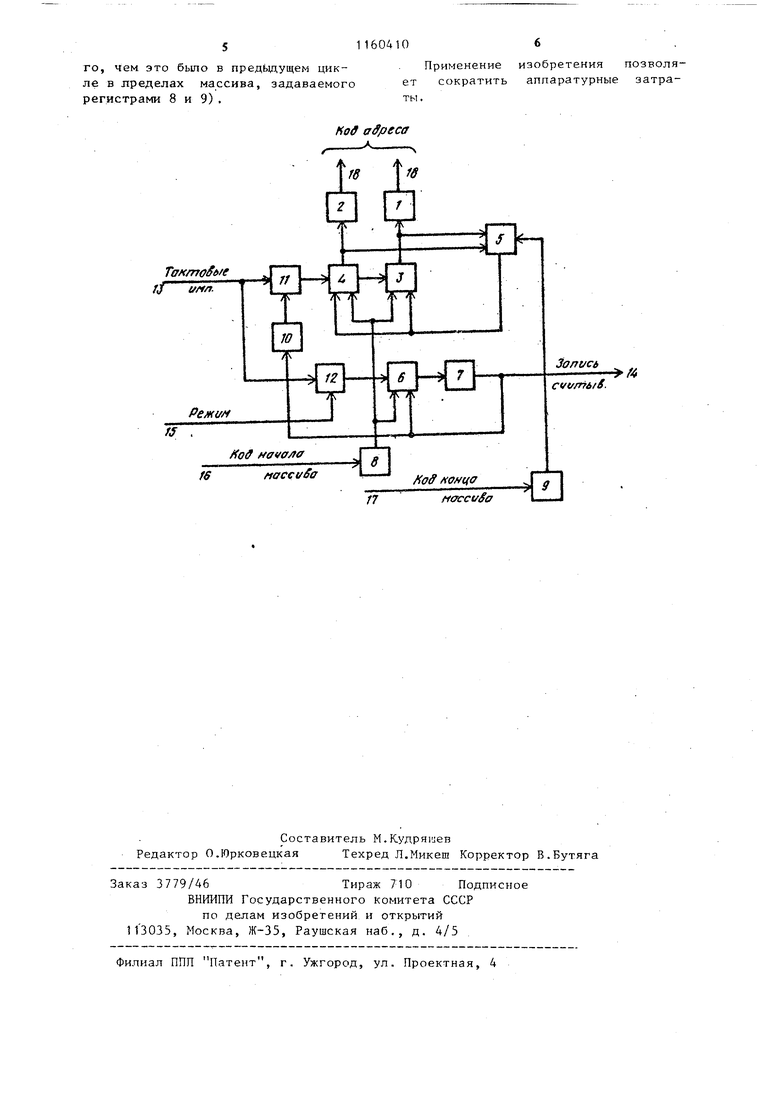

Поставленная цель достигается тем что в устройство адресации памяти, содержащее регистры старших и младших разрядов адреса, счетчики старших и младших разрядовадреса, схему сравнения, счетчик, дешифратор, регистр начала и регистр конца массива, выход регистра начала массива соединен с установочным входом счетчика старших разрядов адреса, выход регистра конца массива соединен с первым входом схемы сравнения, вход регистра старших разрядов адреса и старшие рааряды второго входа схемы сравнения подключены к выходу счечика стар1Ш1х разрядов адреса, вход регистра.младших разрядов адреса соединен с выходом счетчика младших разрядов адреса, выходы регистров младших и старших разрядов адреса являются группой выходов устройства, введены элемент задержки, элемент ИЛИ и элемент И, первый вход которого соединен с трактовым входом устройства и первым входом элемента ИЛИ, выход которого соединен со счетным входом счетчика младших разрядов адреса, выход переноса которого соединен со счетным входом счетчика старших разрядов адреса, выходы счетчика младших разрядов адреса подключены к младшим разрядам второго входа схемы сравнения, установочные входы счетчика младших разрядов адреса и счетчика соединены с выходом регисра начала массива, входы управления записью счетчиков старших и младших разрядов адреса соединены с выходом схемы сравнения, выход счетчика соединен с входом дешифратора, выход которого соединен с сигнальным выходом устройства, входом управления записью счетчика и через элемент задержки с вторым входом элемента ШШ, счетный,вход счетчика соединен с выходом элемента И, второй вход которого соединен с входом режима устройства, первый и второй кодовые устройства соединены соответствен но с. входом регистра начала массива и входом регистра конца массива. На чертеже представлена функциональная схема устройства адресации памяти. Устройство содержит регистр 1 старших и регистр 2 младших разрядов адреса, счетчик 3 старших и счетчик младших разрядов адреса,схему 5 сравнения, счетчик 6, дешифратор 7,регистр 8 начала и регистр 9 конца мас сива, элемент 10 задержки, элемент ИЛИ 11, элемент И 12, тактовый вход 13, сигнальный выход 14, вход. 15 режима, группу кодовых входов 16, груп пу кодовых входов 17 и группу.выходов 18. Устройство работает в двух режимах. Первый режим. Вьдача адресов данных в порядке их возрастания (убивания) , начиная с адреса, разряды кото .рого находятся в регистре начала мас сива, и заканчивая адресом, старшие и млаДшие разряды которого находятся в регистре конца массива. В этом режиме после начальной засылки содержимое регистра 8 передается в счетчики 3 и 4, а затем в регистры 1 и 2, адреса, а код регистра 9 конца массива подается на вход схемы 5 сравнения. Так формируется первый адрес. При этом на вход 15 устройства подается Нулевой потенциал, в результате чего на вход счетчика 6 запрещается поступление импульсов, подаваемых на вход 13. Затем через элемент ИЛИ 11 прибавляют единицу в счетчик 4 и производится выдача содержимого счетчиков 3 и 4 в регист ры 1 и 2 соответственно. В конце каждой новой выдачи адреса проверяется с помощью схемы 5 совпадение кодов счетчиков 3 и 4 с кодом perncT ра 9 конца массива. В случае их совпадения прекращается .вьщача адресов. второй режим адресов, при которой обеспечивается режим бегущей строки. При работе в этом режиме на вход 15 подается уровень логической 1, при котором разрешается поступление импульсов, подаваемых на шину 13, одно временно на входы счетчика 4 младших разрядов адреса и счетчика 6. После начальной засылки содержимое регистра 8 передается в счс-- . т и 4 а затем в регистры 1 и 2. Код регистра 9 конца массива подается на нход Схеу мы 5. Так формируется первый адрес Затем через элементы 11 и 12 па пходы счетчиков 4 и 6 прибавляется единица и производится выдача содержимого счетчиков 3 и 4 в регистры 1 и 2 соответственно. Так формируются последующие адреса памяти до конеч- ного адреса массива. При равенстве кодов счетчиков 3 и 4 и кода регистра 9 конца массива формируется импульс, который поступает на входы управления записью начального адреса, определяемого кодом регистра 8 начала массива, который и записыва-. .ется в счетчики 3 и 4 и через них в регистры 1 и 2 соответственно.Одновременно с импульсом на вьрсоде схемы 5 вырабатывается короткий импульс на выходе дешифратора 7, который вьздается на выход 14 и через элемент 10 задержки и элемент ИЛИ 11 поступает на вход счетчика 4 младших { азрядов адреса,а код его. в регистр 2 на выход устройства. Таким образом, во втором цикле обращения к массиву памяти в первый адрес памяти записывается новая информация (на место ранее записанной). Запись обеспечивается вьщачей в память короткого импульса соответствующего уров.ня на выходе меняя адреса памяти информа1щя считывается из этого же адреса). Одновременно с появлением короткого импульса на выходе дешифратора 7 в.счёТчик 6 записывается код начала массива. Наличие связи между выходом дешифратора 7 через элементы 10 и 11 и выходом счетчика младших разрядов адреса приводит к тому, что до прихода тактового импульса во втором цикле обращения к памяти сигнал, поступивший с выхода дешифратора 7, добавляет единицу в счетх,ик 4. Это приводит к тому, что в этом цикле обращения к памяти сначала срабатывает схема 5, а с задержкой на такт (период следования тактовых импульсов на входе 13) дешифратор 7. В следующем цикле опроса адресов памяти эта задержка составляет два такта и т.д. Таким образом, в каждом цикле обращения к памяти производится запись на место самых старых данных новой информации и вывод массива данных, хранящихся в памяти, начиная с очередного адреса, на единицу больше

го, чем это было в предыдущем цикле в лределах массива, задаваемого регистрами 8 и 9),

// Ufin.

f6

11604106

Применениеизобретения позволяет сократитьаппаратурные затраты.

Л

fiCfcct/Sa

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1513506A2 |

| Устройство адресации для канала прямого доступа к памяти | 1981 |

|

SU1005052A1 |

| Цифровое логарифмическое устройство | 1983 |

|

SU1101819A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1987 |

|

SU1444814A1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1374279A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство управления с контролем переходов | 1983 |

|

SU1103238A1 |

УСТРОЙСТВО АДРЕСАЦИИ ПАМЯТИ, содержащее регистры старших и младших разрядов адреса счетчики старших и младших разрядов адреса, схему сравнения, счетчик, дешифратор, регистр начала и регистр конца массива, выход регистра начала массива соед-инен с установочным входом счетчика разрядов адреса, выход регистра конца массива соединен с первым входом схемы сравнения, вход регистра старших разрядов адреса и старшие разряды второго входа схемы сравнения подключены к вь1ходу счетчика старших разрядов адреса, вход регистра мпадших разрядов адреса соединен с выходом счетчика младших разрядов адреса, выходы регистров младших и старших разрядов адреса являются группой вькодов устройства, отл и. чающееся. тем, чго , с целью сокращения аппаратурных затрат, оно содержит элемент задержки, элемент ИЛИ и элемент И, первый вход которого соединен с тактовым входом устройства и первым входом элемента ИЛИ, выход которого соединен со счетным входом счетчика младших разрядов адреса ,выход переноса которого- соединен со счетным входом счетчика старших разрядов адреса, выходы счетчика младших разрядов адреса подключены к младшим разрядам второго входа схе- . мы сравнения, установочные входы счетчика и счетчика младших разрядов адреса соединены с выходами регистра начала массива, входы управления за(Л писью счетчиков старших и младших, разрядов адреса соединены с выходом схемы сравнения, выход счетчика соединен с входом дишифратора, выход которого соединен с сигнальным выходом устройства, входом управления записью счетчика и через элемент задержки с-вторым входом элемента ИЛИ, счетный вход счетчика соединен с выходом элемента И, второй вход котоа рого соединен с входом режима устройства, первый и второй входы уст ройства соединены соответственно с входом регистра начала массива и входом регистра конца массива.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Канал прямого доступа к памяти электронной вычислительной машины (эвм) | 1977 |

|

SU691840A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство адресации для канала прямого доступа к памяти | 1981 |

|

SU1005052A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1984-01-11—Подача