{5) ЦИфРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU953721A2 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU928632A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1051701A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

. : 1

Изобретение относится к «цифровой измерительной и вычислительной технике и может быть использовано для преобразования цифровых величин.

Известен цифроаналоговый преобразователь, содержащий регистр входного цифрового кода, выход которого соединен со вторым входом ключевых элементов, выход источника опорного напряжения соединен с пе|эвым входом ключевых элементов, выход ключевых л элементов соединен со входом резистивного делителя напряжения, выход резистивного делителя напряжения соединен со входом операционного усилителя, выход операционного усилителя является выходом цифроаналогового преобразователя Cl3 .

Недостатком данного цифроаналогового преобразователя является низкая точность преобразования, ограниченная- точностью подгонки резисторов в резистивной матрице.

Известен также цифроаналоговый преобразователь,, содержащий регистр, цифровой коммутор, блок ключевых элементов, блок эталонных величин, блок суммирования эталонных величин, блок выделения paзнoctи, блок управления и первый блок свертки кодов, выход которого соединен с первым

входом цифрового коммутатора ВЫХОД:

которого подключен к первым входам

10 блока ключевых элементов, вторые входы которого соединены с выходом блока эталонных величин, выход блока - ключевых элементов подкл рчен к входу

j блока суммирования.эталонных величин выход которого через блок выделения разности соединен с первым вхбдом блока управления, первый и второй выходы блока управления соединены )

20 соответственно с управляющими входами регистра ицифрового коммутат эра C2l .

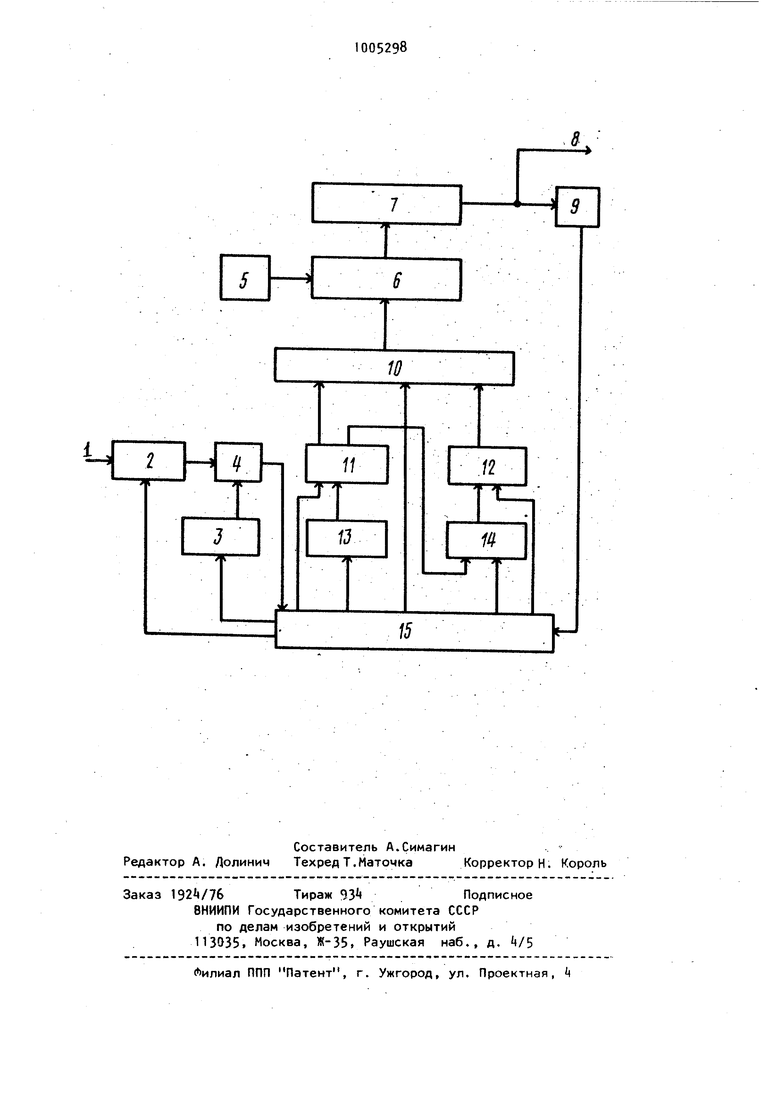

Недостатком данного устройства является ограниченная точность преобразования вследствие температурной и временной нестабильности, возникающей в резистивном делителе, напряжения , который используется в блоке эталонных величин. Цель изобретения - повышение точности преобразования. Поставленная цель достигается тем, что в цифроаналоговый преобразователь, содержащий регистр, цифровой коммутатор, блок ключевых элемен тов, блок эталонных величин, блок су мирования эталонных величин, блок выделения разности, блок управления и первый блок свертки кодов, выход которого соединен с первым входом цифрового коммутатора, выход которого подключен к первым входам блока ключевых элементов, вторые входы которого соединены с выходом блока эталонных величин, выход блока ключевых элементов подключен к входу блока суммирования эталонных величин, выход которого .через блок выделения разности соединен с первым входом блока управления, первый и второй выходы блока управления соединены соответственно с управляющими входами регистра и цифрового коммутатора, введены два реверсивных счет чика, второй блок свертки кодов, третий счетчик, блок сравнения кодов, первый вход которого соединен с выходом регистра, второй вход с выходо третьего счетчика, а выход - с вторы входом блока управления, причем выход первого реверсивного счетчика подключен к первому входу первого бл ка свертки кодов, второй выход которого соединен с первым входом второго реверсивного счетчика, выход кото рого подключен к первому входу второго блока свертки кодов, выход которого соединен с вторым входом цифрового коммутатора, при этом третий четвертый, пятый, шестой и седьмой выходы блока управления соединены соответственно со входом третьего счетчика, входом первого реверсивно го счетчика, вторым входом первого блока свертки кода и вторым входом второго блока свертки кода. На чертеже представлена функциональная схема устройства. Схема содержит вход 1 преобразователя, регистр 2, счётчик 3, блок сравнения кодов k, блок эталонных величин 5 блок ключевых элементов 6, блок суммирования эталонных величин. 7 выход цифроаналогового преобразователя 8, блок выделения разности 9 цифровой коммутатор 10, первый лок свертки кода 11, второй блок свертки кода 12, первый реверсивный счетчик 13, второй реверсивный счетчик Tt, блок управления 15Вход 1 цифроаналогового преобразователя является информационным, через который на первый вход регистра 2 поступает цифровой код. Выход регистра 2 соединен с первым входом блока сравнения кодов k, второй вход которого подключен к выходу счетчика 3. Выход блока соединен со вторым входом блока управления 15- Выход первого реверсивного счетчика 13 подключен ко второму входу первого блока свертки кода 11, первый выход которого соединен с первым входом цифрового коммутатора 10. Второй выход блока 11 подключен к первому входу второго реверсивного счетчика 1 выход которого соединен с первым входом второго блока свертки кода 12. Выход блока 12 подключен к третьему входу цифрового коммутатора 10. Вы- i ход цифрового коммутатора 10 соединен с управляющими входами блока ключевых элементов 6, информационные входы которого подключены к выходу блока эталонных величин 5. Выход блока ключевых элементов 6 соединен со вхоДОМ блока суммирования эталонных величин 7. Выход блока 7 является выходом 8 цифроаналогового преобразователя, на котором формируется результирующий аналоговый сигнал. Вход блока выделения разности 9 соединен с выходом блока суммирования эталонных величин 7. В процессе преобразо вания блок выделения разности 9 производит сравнение предыдущего и последующего .аналоговых сигналов, формирующихся на выходе 8 цифроаналогового преобразователя. Выход блока 9 .. является управляющим и соединен с . первым входом блока управления 15Первый, второй, третий, четвертый, пятый, шестой и седьмой,выходы блока управления 15 соединены соответственно со вторым входом регистра 2, управляющим входом цифрового коммутатора 10, входом счетчика 3, входом первого реверсивного счетчика 13, вторым входом второго реверсивного счетчика Н, вторым входом первого блока свертки кода 11 и йторым входом второго блока свертки кода 12. Блок 15 обеспечивает функциониров ние устройстве.. Цифроаналоговый преобразователь работает в одном режиме, т.е. в режиме преобразования кодов с иррациональным основанием в аналоговые сигналы. В процессе преобразования производится оперативный контроль линейности вь1ходной характеристики, опред ляются величины отклонений весов раз рядов от требуемых величин, производится их регистрация и коррекция. К кодам с, иррациональным основанием относятся р-коды Фибоначчи. В кодах золотой р-пропорции любое действительное число у может быть представлено в виде «о « -двоичная цифра; где q -вес 1-го разряда. По команде блока управления 15 входной код записывается в регистр 2 В следующий такт времени в младшие разряды первого реверсивного счетчика 13 и второго реверсивного счетчика 1 4 записывается по единице. По команде блока 15.кодовая кокйинация находящаяся в первом реверсивном сче чике 13. через устройство свертки ко дов 1 1 , цифровой коммутатор 10 подается на управляющие входы к/точевых элементов 6, которые осуществляют по ключение аналоговых величия от блока эталонных величин 5 через информационные входы ключевых элементов 6, ко входу блока суммирования эталонны величин 7. В результате этого на выходе 8 цифроаналогового преобразователя сформируется аналоговый эквивалент кодовой комбинации, находящейся в первом реверсивном сметчике 13.. После этого по команде блока 15 будет осуществлена свертка кодовой комбина ции, находящейся в первом реверсивно счетчике 13. в первом блоке свертки кодов 11. Свернутая кодовая комбинация через цифровой коммутатор 10 подается на управляющие входы ключевых элементов 6 и обеспечивает подач через информационные входы блока 6 аналоговых величин с блока 5 на блок 7. В результате на выходе 8 цифроанаглогового преобразователя сформируется аналоговый эквивалент свернутой кодовой комбинации. Если веса ,разрядов устройства суммирования эталонных величин 7 соответствует требуемым, то блок выделения разности 9 не зафиксирует разницы между аналоговыми эквивалентами развернутой и свернутой кодовых комбинаций. По команде блока управления 15 производится свертка кодовой комбинации, находящейся во втором реверсивном счетчике I, во втором блоке свертки 12, параллельно во времени, к содержимо му счетчика 3 прибавляется единица. Если все веса разрядов блока соответствуют требуемым, то аналогичные действия выполняются до тех пор, пока код, записанный в счетчике 3, не становится равен входному коду, находящемуся в регистре 2. Момент равенства кодов зафиксируется блоком сравнения кодов k, управляющий сигнал с выхода .которого поступает йа вто- рой вход блока управления 15. По команде блока 15 с выхода 8 цифроаналогового преобразователя можно будет снимать результирующий аналоговый эквивалент входного кода. При несоответствии весов разрядов требуемым значением процесс преобразова ния будет происходить следующим образом. Пусть вес 1-го разряда не соответствует требуемому значению. На очередном шаге преобразования в первом, реверсивном счетчике 13 и . втором реверсивном счетчике Н записываются кодовые комбинации, содержащие единицы в (1-1)-м и (1-2) разрядах. Ко- , довая комбинация, находщаяся .в первом реверсивном счетчике 1р, через блок 11., цифровой коммутатор 10 поступает на управляющие входы блока ключевых элементов 6, который осуществляет подачу аналоговых чин от блока 5 через информационные входы блока & на блок суммирования эталонных величин 7 В результате на выходе 8 цифроаналогового преобразователя формируется аналоговый эквивалент кодовой комбинации, находящейся в первом реверсивном счетчике 13 и втором реверсивном счетчике It. По команде блока 15 в первом локе свертки кодов 11 производится свертка кодовой комбинации, находяейся в первом реверсивном счетчике 13. Свернутая кодовая комбинация через .блок 10 поступает на управляюие входы ключевых элементов б котоkрые через информационные входы осуществляют подачу аналоговых величин от блока эталонных величин 5 на блок суммирования эталонных величин 7. На выходе 8 цифроаналогового преобразователя сформируется аналоговый эквивалент свернутой кодовой комбина ции, находящейся в первом реверсивном счетчике 13. Так как вес 1-го разряда не соответствует требуемому значению, то блок выделения разности 9 зафиксирует перепад уровней аналог вых эквивалентов развернутой и свернутой кодовых комбинаций и его знак, и выдает управляющий сигнал, который поступит на первый вход блока управления 15. Если знак расстройки положительный, т.е. вес 1-го разряда больше суммы весов (1-1) и (1-2)-го разряда, то по команде блока управления 15 к кодовой комбинации, содержащейся во втором реверсивном счетчике It, добавляется единица. Полученная кодовая комбинация через блок 12, цифровой коммутатор 10 подается на управляющие входы ключевых элементов 6, которые через информационные входы осуществляют подачу аналоговых величин от блока эталонных величин 5 на блок суммирования эталонных величин 7. На выходе 8 цифроаналоговог преобразователя формируется аналоговый эквивалент кодовой комбинации, находящейся во втором реверсивном счетчике 1. Одновременно производит ся прибавление единицы к содержимому счетчика 3. По команде блока 15 путем подачи через блок 11, цифровой коммутатор 10 на управляющие входы ключевых элементов 6, осуществляющих подключение аналоговых величин через их информационные входы от блока 5 к блоку 7, кодовой комбинации, содержащейся в первом реверсивном счет чике 13, на выходе 8 цифроаналогового преобразователя сформируется анал говый эквивалент кодовой комбинации, находящейся в блоке 13. Аналогичные дейетвия будут выполняться до тех пор, пока блок выделения разности 9 не прекращает фиксировать.разность между уровнями аналоговых эквивалентов нескорректированной кодовой комбинации, находящейся в первом реверсивном счетчике 13 и скорректированной кодовой комбинации, находящейся во втором реверсивном счетчике Т, или пока блок сравнения кодов не выдает сигнал о равенстве кодов, находящихся в регистре 2 и счетчике 3. В первом случае кодовая комбинация, находящаяся в блоке 13, перепишется по команде блока 15 в блок И, и процесс преобразования продолжается дальше. Во втором случае по команде блока 15 с выхода 8 цифроаналогового преобразователя снимается аналоговый эквивалент скорректированной кодовой комбинации, находящейся во втором реверсивном счетчике 1, являющейся результатом преобразования код-аналог. Если знак расстройки отрицательный, т.е. вес 1-го разряда меньше суммы весов (1-1)-го и (1-2)-го разрядов, то по команде блока управления 15 к содержимому первого реверсивного счетчика 13 добавляется единицаi По команде блока управления 15 кодовая комбинация, находящаяся во втором реверсивном сметчике 1Л, через блок 12,цифровой коммутатор 10 подается на управляющие входы ключевых элементов 6, которые через информационные входы осуществляют подключение аналоговых величин от блока 5 к блоку 7. 8результате на выходе 8 цифроаналогового преобразователя формируетс:я аналоговый эквивалент кодовой комбинации, находящейся во втором реверсивном счетчике . По команде блока 15 кодовая комбинация, находящаяся в первом реверсивном счетчике 13, через блок 11, цифровой коммутатор 10 подается на управляющие входы ключевых элементов 6, которые осуществляют подключение аналоговых величин от блока 5 к блоку суммирования эталонных вели4ин 7. В результате на выходе формируется аналоговый эквивалент кодовой комбинации, находящейся в первом реверсивном счетчике 13. Аналогичные действия выполняются дотех пор, пока блок выделения разности 9не прекращает фиксировать разность между уравнениями аналоговых эквивалентов Нескорректированной кодовой комбинации, находящейся во втором реверсивном счетчике Н и скорректирйванной кодовой комбинации, находящейся в первом реверсивном счетчике 13.Когда это произойдет по команде блока управления 15 к содержимому счетчика 3 прибавляется единица,.и процесс преобразования продолжается. Когда а ходе преобразования достига-. ется равенство кодов в регистре 2 и счетчике 3, с выхода блока сравнени кодов k поступает управляющий сигна на второй управляющий вход блока управления; 15. При этом на выходе 8 цифроаналогового преобразователя сформируемся результирующий сигнал, являющийся аналоговым эквивалентом скорректированной -кодовой комбинации, находящейся в первом реверсивном счетчике 13.В предлагаемом устройстве за сче цифровой коррекции точность преобра зования код-аналог выше технологи ческой точности элементов блока эта лонных величин. Важным преимуществом предлагаемо го устройства является то, что коррекция производится в процессе преобразования, что позволяет при эксплуатации устройства значительно увеличить .его срок службы, улучшить точностные параметры. : При изготовлении -цифроаналоговых преобразов.ателей в; виде ийтегральны микросхем увеличится на этапе произ водства выпуск годной продукции.. Предлагаемое Vcтpoйcтвo выгодно, отличается от известных использующих коды с иррациональным основанием тем, что не требует для сопряжения:, с существующими средствами вычислительной техники преобразователей кодов, так как регистр 2 и счетчик 3 могут быть выполнены для системы счисления с любым основанием. Формула изобретения Цифроаналоговый преобразователь, содержащий регистр, цифровой коммутатор, блок ключевых элементов, блок эталонных величин, блок суммирования эталонных величин, блок выделения разности, блок управления и первый блок свертки кодов, выход которого соединен с первым входом цифрового коммутатора, выход которого подключен к первым входам блока ключевых элементов, вторые входы которого соединены с выходом блрка эталонных величин, .выход блока ключевых элементов подключен к входу блока суммирования эталонных величин, выход которого, через блрк выделения разности Соединен с первым входом блока управления j первый и второй выходы блока управления соединены соответственно с управлящими входами реги-/ стра и цифрового коммутатора, отл и ч-а ю щ и и с я тем, что, с . целью повышения точности, в него введейы два реверсивных счетчика, второй блок свертки кодов, третий счетчик, блок сравнения кодов, первый .вход которого соединен с выходом региртра, второй вход с выходом третьего счетчика, а выход - с вторым входом блока управления, причем выход первогореверсивного счетчика подключен к первому входу первого блока свертки кодов, второй выход которого соединен с. первым входом второго реверсивного счетчика, выход которого подключен к первому в.ходу второго блока свертки кодов, выход которого соединен с вторым входом цифрового коммутатора, при этом третий, четвертый, пятый, шестой и седьмой вы- . ходы блока управления соединены соответственно с входом третьего счетчика, входом первого реверсивного счетчика, вторым входом первого блока свертки кода и вторым входом второго блока свертки кода. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № , кл. Н 03 К 13/02, 09.08.73. 2L. Авторское свидетельство СССР по заявке Vf 2853223, кл, Н 03 К 13/02, .79 (прототип).

Ц

Авторы

Даты

1983-03-15—Публикация

1981-07-14—Подача