(St) УСТРОЙСТВО ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| Устройство для декодирования сверточного кода | 1973 |

|

SU510803A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Кодек для системы связи с многократной фазовой модуляцией | 1987 |

|

SU1629992A1 |

| Устройство для декодирования сверточного кода | 1986 |

|

SU1467753A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Устройство для декодирования сверточного кода | 1977 |

|

SU675616A1 |

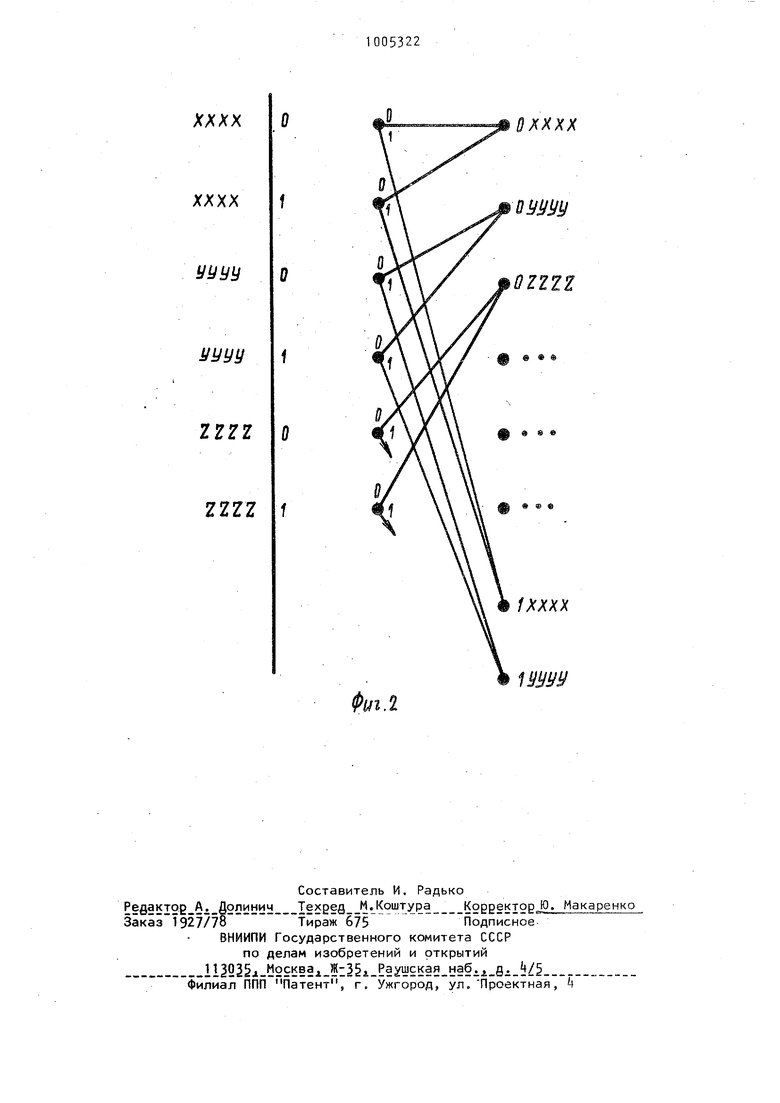

Изобретение относится к передаче , данных и может быть использовано для; повышения достоверности передачи информации по радиоканалу. Известно устройство декодирования сверточного кода по алгоритму Витерби, которое содержит блок вычисления метрик ветвей, ri параллельных каналов обработки, каждый из которых состоит из двух сумматоров, первые входы ко-торых через блок инвертирования- и ком мутатор соединены с выходом блока вычисления метрик ветвей, а вторые - с выходами соответствующих блоков памяти метрик ветвей, а выходы через блок сравнения подключены к коммутатору метрик ветвей, выход которого по подключен ко входу адресного двухтакт ного коммутатора, управляемого блоком промежуточной памяти, и выходы адресного двухтактного коммутатора подключены ко входам блока памяти решения и входам соответствующих блоков памяти метрик ветвей, дополнительные выХОДЫ которых через элементы ИЛИ соединены со входами блока нормированного порога; выход блока памяти решения через дополнительный сумматор подключен к компаратору 1 . Недостатком его является практическая невозмо хность реализации схемы при больших значения кодовых ограничений используемых кодов (уже -при 1с 5). Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является устройство декодирования сверточного кода, содержащее блок вычисления метрик ветвей и п параллельных каналов обработки, каждый из которых содержит регистры памяти, сумматоры, блок сравнения, коммутатор метрик ветвей, также блок памяти решений и компаратор, выход блока вычисления метрик ветвей непосредственно подключен ко входам младших разрядов сумматоров п каналов обработки, к входам ббъединенных старших разрядов которых под-, ключей выход блока нормированного порога, вход которого через элемент ИЛИ подключен к дополнительным выходам регистров памяти, при этом первые выходы коммутаторов метрик ветвей п каналов обработки подключены ко входам записи соответствующих регистров памяти, а вторые выходы коммутаторов метрик ветвей через блок памяти решении подключены к входу компаратора. Устройство предлагает параллельную обработку узлов решетчатой диаграммы что позволяет обеспечить большую (еди ницы Мдод) информационную скорость в канале 2 Недостатком данного устройства являются большие аппаратурные затраты при к 5 из-за наличия п параллельных каналов обработки и регистровой Организации блоков памяти. В большом классе систем передачи данных необходимо обеспечить высокие вероятностные характеристики передаваемых сообщений (т.е. необходимо ис пользование сверточных кодов с большим значением кодового ограничения к ) при требуемой информационной скорости в каналах единицы, десятки К 5оА что обеспечивает предлагаемое устройства. Цель изобретения - упрощение устройства. Для достижения указанной цели в устройство для декодирования сверточ ного кода, содержащее блок вычисления метрик ветвей, компаратор, блок нормированного порога, первый элемент ИЛИ и два параллельных канала о работки, состоящий каждый из двух сумматоров, выходы которых подключены ко входам блока сравнения, а входы младших разрядов - к выходам блока вычисления метрик ветвей, коммута тора метрик ветвей, к управляющему входу которого подключен выход блока сравнения, введены блок памяти ме рик, блок памяти путей, два коммутатора путей, второй элемент ИЛИ, счет чик адресов считывания, счетчик адре сов записи и два кодера, а в каждый канал обработки - блок вычитания, пр этом выходы блоков вычитания через первый элемент ИЛИ соединены со входом блока нормированного порога, под соединенного выходом ко вторым входам блоков вычитания, первые входы которых подключены к выходам соответствующих коммутаторов метрик ветвей, выход первого элемента ИЛИ подключен к входу блока памяти метрик, один выход которого соединен со вторыми входами сумматоров первого канала обработки ,другой - со вторыми входами сумматоров второго канала обработки.выходы счетчика адресов считывания черезко.деры соединены со входами блока вычисения метрик ветвей, второй выход счетчика адресов считывания и выход четчика адресов записи подключены к соответствующим адресным входам блока памяти метрик и блока памяти путей. выходы блока памяти путей через коммутаторы путей подключены к входам компаратора, выходы блоков сравнения через второй элемент ИЛИ соединен с управляющими входами коммутаторов путей. В указанном коммутаторе блоки памяти метрик и путей имеют адресную организацию, выполнены на регистрах параллельного типа. На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - иллюстрация кодовой решетки к доказательству положения о соответствии двух узлов одного ярус двум узлам на следующем ярусе. Устройство (фиг. 1) содержит блок вычисления метрик ветвей 1, два канала обработки, каждый из которых содер : ит сумматоры 2-1, 2-2 и 2-3, 2- соответвенно, входы которых соединены с выходами блока вычисления метрик ветвей 1, блок сравнения в первом канале и - во втором, входы которого подключены к выходам сумматоров 2-1, 2-2 и 2-3, 2-, коммутатор 4-1 и it-2 метрик ветвей, входы которого подключены к выходу соответствующего блока сравнения 3-2, блок вычитания 5-1, , входы которого подключены к выходам коммутатора метрик ветвей, а выходы через первый Элемент ИЛИ 6 подключены ко входам блока нормированного порога 7, выходы которого подключены ко вторым входам блока вычитания 5 и входам блока памяти метрик 8, выходы которого подключены ко вторым входам сумматоров 2-1 - 2-А каналов обработки, а также блок памяти путей 9, выходы которого через коммутаторы путей 10-1 - 10-2, управляющие входы которых подсоединены через второй элемент ИЛИ 11 к выходам блоков сравнения - обоих каналов обработки, подключены к компаратору 12, выход которого является выходом устройства,а также кодеры 13-1 13-2, подключенные к входам блока . вычисления метрик ветвей 1, счетчики адресов считывания 1 и адресов записи 15 подключенные к адресным вхо дам блоков памяти метрик 8 и памяти путей 9. Устройство работает следующим образом. На входы блока вычисления метрик ветвей 1, являющимися входами устрой ства, поступают с квйнтователя-триадами девять или шесть символов, соответственно для скоростей кода 1/3 и 1/2. На вторые входы блока поступа ют двоичные триады с кодеров 13-1 13-2, представляющие собой значения ветвей решетчатых диаграмм, задаваемые счетчиком адресов считывания 1 . На выходах блока вычисления метрик получаются значения приращений метрик, определяемые степенью корреляции принятой кодовой ветви с каж дой из ветвей, соответствующей на ре шетчатой диаграмме поступлению нулевого информационного символа. На дру гих выхода блока вычисления метрик значения приращений метрик, соответствующие поступлению единичного информационного символа. Выходы блока вычисления метрик ветвей подключены к входам сумматора 2-1 - 2-k, вторые входы которых подключены к выходам блока памяти метрик 8. Количество ка налов обработки равно двум. Это число выбрано потому, что каждым двум рядом расположенным узлам в ярусе со ответствует строго определенная пара узлов на следующем ярусе,, что справедливо для двоичных св. кодов со ско ростями l/t где 1,2,3,... (см. фиг. 2). Номер каждого узла в двоичном виде равен состоянию кодера, т.е. информации, находящейся в регистре кодера. Номера узлов возрастают сверху вниз, поэтому в последних разрядах номеров будет чередование О и 1. Рас смотрим первый узел. При скорости 1/с в кодер поступает один бит информации, причем находящаяся в кодере информация сдвигается вправо и последний разряд пропадает. Поэтому кодер может перейти в одно из двух состояний: ОХХХХ или 1ХХХХ (при поступлении О и 1 соответственно). Рас102 смотрим второй узел. Аналогично поступление одного бита информации может привести к одному из двух состояний: ОХХХХ или 1ХХХХ. Следовательно паре узлов соответствует пара узлов. на следующем ярусе. На следующем ярусе рассуждения повторяются. Обработка узлов в паре и вычисление превращений метрик ветвей, соединяющих эти пары, производится параллельно. Результаты сложения с выходов сумматоров 2-1 - 2- подаются на входы блока сравнения 3-1 и 3-2 и дальше на коммутаторы метрик ветвей i-l и , где осуществляется конкуренция двух метрик. Выжившие метрики нормируются в блоке вычитания 5-1 и 5-2 путем уменьшения ее значения с целью избежания переполнения ячеек блока памяти метрик 8. Выходы блока вычитания 5-1 и 5-2 подключены через первый элемент ИЛИ 6 ко входу блока памяти метрик 8. Блок памяти метрик 8 разделен на две части, одна из которых служит для хранения и считывания информации, вторая - для записи и хранения. При каждом шаге декодирования обе части обмениваются своими функциями. В свою очередь, каждая часть памяти разделена на две половины для осуществления параллельного доступа к двум ячейкам памяти, хранящим значения метрик. Аналогично организована и память для хранения путей - блок памяти путей 9- Отличие состоит только в разрядности запоминаемых величин. Все блоки памяти имеют адресную организацию, кроме того, запоминаемая N разрядная величина хранится в N микросхемах по одному разряду в каждой. Разрядность путей, хранимых в памяти устройства, определяется величиной А.к, называемой глубиной проникновения в кодовую решетку, где А принимает целые значения в интервале 1-6, а количество разрядов в хранимых метриках не превышает В, которое для к 10 не превышает 10. Поэтому, при предлагаемой организации памяти количество микросхем пропорционально величине кодового ограичения /-/А.к + В при условии, что . объем памяти микросхем не превышает количества запоминаемых путей, в то время как использование принципа организации памяти, при котором запоинаемая М разрядная величина хранится в одной микросхеме (регистре), количестоо микросхем пропорционально количеству хранимых величин Таким образом, количество микросхем при данной организации памяти уменьшается в .к, + В раз. На адресные входы блоков памяти метрик 8 и памяти путей 9 поступают адреса считывания и записи соответственно с выходом счетчика адресов считывания Н и адресов записи 15. Конкуренция путей осуществляется на коммутаторах путей 10-1 и 10-2, входы которых подключены соответственно к выходам блока памяти путей а управляющие входы подключены ко второму элементу ИЛИ 11, входы кото рого подключены к выходам блоков ср нения и первого и второго к налов обработки. Старшие разряды проконкурировавших путей с коммутаторов путей 10-1 и 10поступают на вход компаратора12, играющего роль решающего блока. Выход компаратора 12 является выходом устройства. Предлагаемое устройство по сравнению с ранее известным позволяет умень шить количество корпусов микросхем приблизительно в раз. Это дости гается тем, что устройство имеет лишь два канала обработки при любом значении кодового ограничения используемых кодов, а блоки памяти метрик и путей, имеющих адресную организацию, которая позволяет значительно снизить аппаратурный объем памяти устройства, Указанные технические решения дают тем больший выигрыш в упрощении устройства по сравнению с прототипом, чем больше значение кодового ограничения используемых кодов. Практически устройство рассчитано на использование св. кодов с кодовым ограничением в диапазоне от 6 до 15. формула изобретения 1. Устройство декодирования сверточного кода, содержащее блок вычисления метрик ветвей, компараторj блок нормированного порога, первый элемент ИЛИ и два параллельных канала об работки, состоящий каждый из двух сумматоров, выходы которых подключены к входам блока сравнения, а входы младших разрядов - к выходам блока вычисления метрик ветвей, коммутатора метрик ветвей, к управляющему входу которого подключен выход блока сравнения, отличающееся тем, что, с целью упрощения, в него введены блок памяти метрик, блок памяти путей, два коммутатора путей, второй элеэлемеит ИЛИ, счетчик адресов считывания, счетчик адресов записи и два кодера, а в каждый канал обработки блок вычитания, при этом выходы блоков вычитания через первый элемент ИЛИ соединены с входом блока нормированного порога, подсоединенного выходом к вторым входам блоков вычитания. первые входы которых подключены к выходам соответствующих коммутаторов метрик ветвей, выход первого элемента ИЛИ подключен к входу блока памяти метрик, один выход которого соединен с вторыми входами сумматоров первого канала обработки, другой - с вторыми входами сумматоров второго канала обработки, выходы счетчика адресов считывания через кодеры соединены с входами блока вычисления метрик ветвей, второй выход счетчика адресов считывания и выход счетчика адресов записи подключены к соответствующим адресным входам блока памяти метрик и блока памяти путей,выходы блока памяти путей через коммутаторы путей подключены к входам компаратора, выходы блоков сравнения через второй элемент ИЛИ соединены с управляющи- ми входами коммутаторов путей, 2. Устройство по п, 1, о т л и чающееся тем, что блоки памяти метрик и путей выполнены на регистр.ах параллельного типа. Источники информации, принятые во внимание при эксперти зе 1.Авторское свидетельство СССР № 510803, кл. н L 17/30; Н Oi L 1/10, 05.07.73. 2.Авторское свидетельство СССР W 675616, кл. Н О U 17/30, Н 0 L 1/10, 26.10.77 (прототип).

хлхх

xxxx

yyyy

yyyy

nil

zzzz

5ЛХХХ

ozzzz

в «

e «

/ЛХХХ

imy

Авторы

Даты

1983-03-15—Публикация

1981-07-06—Подача