1

Изобретение относится к системам связи и может использоваться в каналах связи, где требуется повысить эффективность передачи информации.

Известно устройство для декодирования сверточного кода, содержащее блок вычисления метрик ветвей и блок вычитания, выход которого подключен к блоку памяти решений через п параллельных каналов обработки, каждый из которых состоит из двух входных сумматоров, к. одному из входов которых подключены выходы соответствующих блоков памяти метрик ветвей, а выходы сумматоров подключены к соответствующим входам блока сравнения и коммутатора метрик ветвей, управляемого блоком сравнения.

Однако известное устройство имеет низкую достоверность декодирования.

Цель изобретения - повышение достоверности декодирования.

Это достигается тем, что в предлагаемом устройстве между выходом блока вычисления метрик ветвей и входом блока вычитания включены последовательно соединенные блок инвертирования метрик ветвей и коммутатор, управляемый сигналом с дополнительного выхода блока вычисления метрик ветвей, а в каждом из п каналов обработки на выходе коммутатора метрик ветвей включен адресный двухтактный коммутатор, управляемый блоком промежуточной памяти, причем выходы адресного двухтактного коммутатора подключены ко входам соответствующих блоков памяти метрик ветвей, дополнительные выходы которых через соответствующие элементы «ИЛИ подключены ко входам блока нормирования порога, подсоединенного к дополнительному входу блока вычитания, кроме того, выход блока памяти решений подключен к компаратору через дополнительный сумматор.

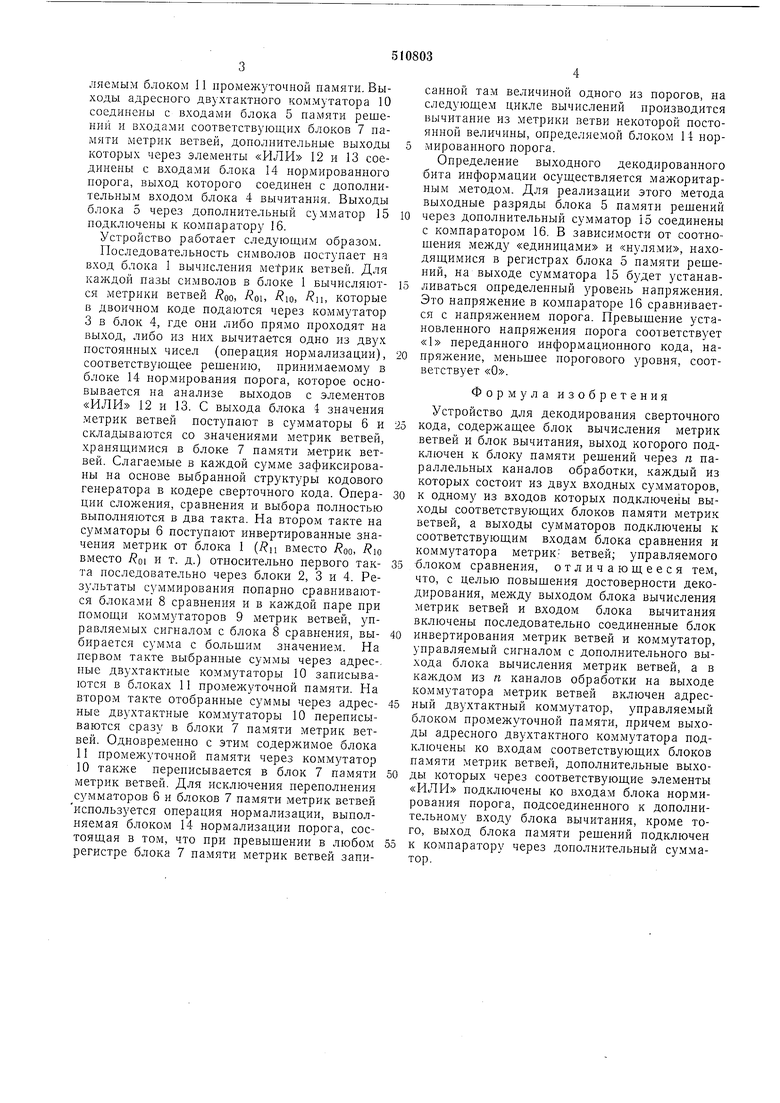

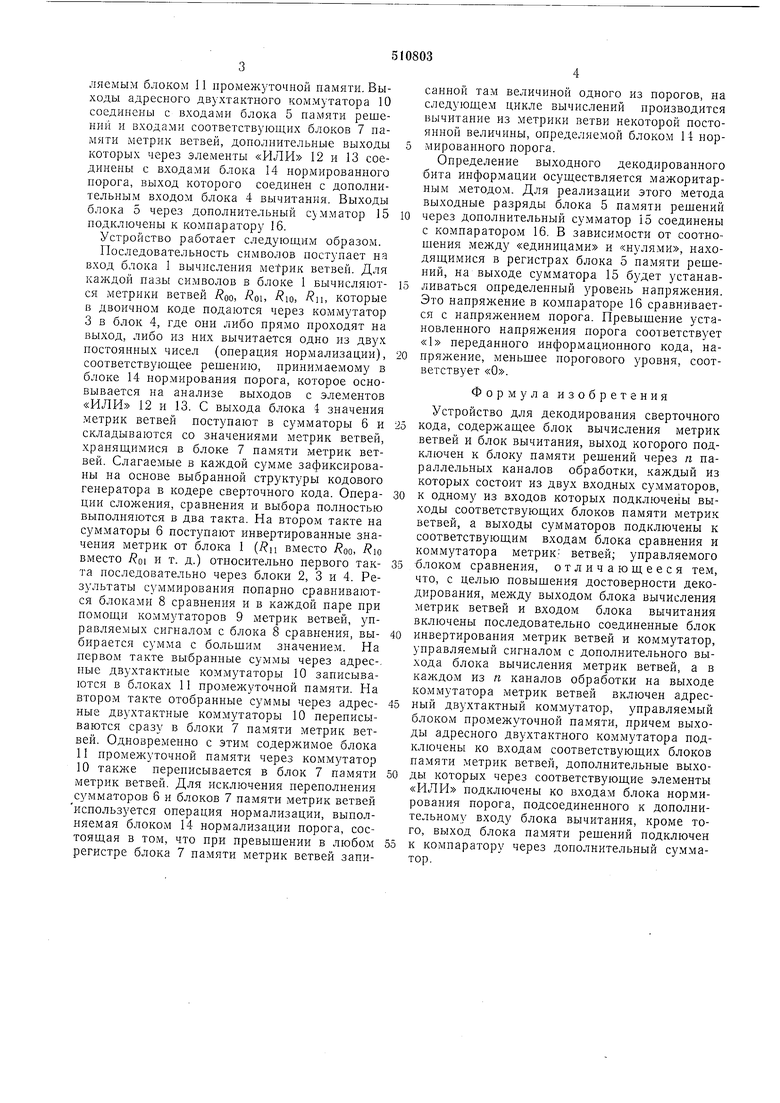

На чертеже показана схема предлагаемого устройства, содержащего последовательно соединенные блок 1 вычисления метрик ветвей, блок 2 инвертирования метрик ветвей, коммутатор 3, второй вход которого соединен с дополнительным выходом блока 1, и блок 4 вычитания. Выход блока 4 вычитания через п каналов обработки соединен с соответствующими входами блока 5 памяти решений. Каждый из п каналов обработки состоит из двух сумматоров 6, первые входы всех сумматоров объединены и соединены с выходол блока 4 вычитания, а вторые - соединены с выходами соответствующих блоков 7 памяти метрик ветвей, выходы сумматоров 6 соединены с блоком 8 сравнения и коммутатором 9 метрик ветвей, Т1равляющий вход которого соединен с выходом блока 8 сравнения, а выходы - с адресным двухтактным коммутатором 10, управляемым блоком 11 промежуточной памяти. Выходы адресного двухтактного коммутатора 10 соединены с входами блока 5 памяти решений и входами соответствующих блоков 7 памяти метрик ветвей, дополнительные выходы которых через элементы «ИЛИ 12 и 13 соединены с входами блока 14 нормированного порога, выход которого соединен с дополнительным входом блока 4 вычитания. Выходы блока 5 через дополнительный сумматор 15 подключены к компаратору 16.

Устройство работает следуюпдим образом.

Иоследовательность символов поступает на вход блока 1 вычисления метрик ветвей. Для каждой пазы символов в блоке 1 вычисляются метрики ветвей оо, , , и, которые в двоичном коде подаются через коммутатор 3 в блок 4, где они либо прямо проходят на выход, либо из них вычитается одно из двух постоянных чисел (операция нормализации), соответствующее решению, принимаемому в блоке 14 нормирования порога, которое основывается на анализе выходов с элементов «ИЛИ 12 и 13. С выхода блока 4 значения метрик ветвей поступают в сумматоры 6 и складываются со значениями метрик ветвей, хранящимися в блоке 7 памяти метрик ветвей. Слагаемые в каждой сумме зафиксированы на основе выбранной структуры кодового генератора в кодере сверточного кода. Операции сложения, сравнения и выбора полностью выполняются в два такта. На втором такте на сумматоры 6 поступают инвертированные значения метрик от блока 1 (Кц вместо RQO, ю вместо 01 и т. д.) относительно первого такта последовательно через блоки 2, 3 и 4. Результаты суммирования попарно сравниваются блоками 8 сравнения и в каждой паре при помощи коммутаторов 9 метрик ветвей, управляемых сигналом с блока 8 сравнения, выбирается сумма с большим значением. На первом такте выбранные суммы через адрес-, ные двухтактные коммутаторы 10 записываются в блоках 11 промежуточной памяти. На втором такте отобранные суммы через адресные двухтактные коммутаторы 10 переписываются сразу в блоки 7 памяти метрик ветвей. Одновременно с этим содержимое блока 11 промежуточной памяти через коммутатор 10 также переписывается в блок 7 памяти метрик ветвей. Для исключения нереполнения сумматоров 6 и блоков 7 памяти метрик ветвей используется операция нормализации, выполняемая блоком 14 нормализации порога, состоящая в том, что при превышении в любом регистре блока 7 памяти метрик ветвей записанной там величиной одного из порогов, на следующем цикле вычислений нроизводится вычитание из метрики ветви некоторой постоянной величины, определяемой блоком 14 нормированного порога.

Определение выходного декодированного бита информации осуществляется мажоритарным методом. Для реализации этого метода выходные разряды блока 5 памяти решений через дополнительный сумматор 15 соединены с компаратором 16. В зависимости от соотношения между «единицами и «нулями, находящимися в регистрах блока 5 памяти решений, на выходе сумматора 15 будет устанавливаться определенный уровень напряжения. Это напряжение в компараторе 16 сравнивается с напряжением порога. Превышение установленного напряжения порога соответствует «1 переданного информационного кода, напряжение, меньшее порогового уровня, соответствует «О.

Формула изобретения

Устройство для декодирования сверточного кода, содержащее блок вычисления метрик ветвей и блок вычитания, выход когорого подключен к блоку памяти решений через п параллельных каналов обработки, каждый из которых состоит из двух входных сумматоров, к одному из входов которых подключены выходы соответствующих блоков памяти метрик ветвей, а выходы сумматоров подключены к соответствующим входам блока сравнения и коммутатора метрик- ветвей; управляемого блоком сравнения, отличающееся тем, что, с целью повыщения достоверности декодирования, между выходом блока вычисления метрик ветвей и входом блока вычитания включены последовательно соединенные блок инвертирования метрик ветвей и коммутатор, управляемый сигналом с дополнительного выхода блока вычисления метрик ветвей, а в каждом из п каналов обработки на выходе коммутатора метрик ветвей включен адресный двухтактный коммутатор, управляемый блоком промежуточной памяти, причем выходы адресного двухтактного коммутатора подключены ко входам соответствующих блоков памяти метрик ветвей, дополнительные выходы которых через соответствующие элементы «ИЛИ подключены ко входам блока нормирования порога, подсоединенного к дополнительному входу блока вычитания, кроме того, выход блока памяти решений подключен к компаратору через дополнительный сумматор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство декодирования сверточного кода | 1981 |

|

SU1005322A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2015621C1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1725400A1 |

| Устройство для декодирования сверточного кода | 1977 |

|

SU675616A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

Авторы

Даты

1976-04-15—Публикация

1973-07-05—Подача