блока управления, а второй вход подключен к первому входу второго триггера и нулевому выходу первого триггера, единичный выход которого является первым выходом управления блока и подключен к входу первого формирователя, выход которого является выходом установки нуля блока

управления, третьим выходом которого является выход второго формировате.ля, вход которого подключен к единичному выходу второго триггера и является вторым выходом блока управления, второй вход второго триггера подключен к второму входу первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2002 |

|

RU2220426C1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Устройство для вычисления средне-КВАдРАТичЕСКОгО зНАчЕНия | 1979 |

|

SU849229A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Преобразователь период-частота | 1975 |

|

SU546102A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ КОЛЕБАНИЙ | 1991 |

|

RU2018911C1 |

1. УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ, содержащее последовательно соединенные блок управления и первый элемент И, последова тельно соединенные первый и второй счетчики, дешифратор и блок элементов И, вторые входы которого подключены к выходам делителя, вход которого подключен к импульсному выходу блока управления, а выходы блока элементов И подключены к входам первого элемента ИЛИ, выход которого подключен к второму входу первого элемента И и первому входу второго элемента И, второй вход которого подключен к первому входу третьего элемента И и второму выходу блока управления, третий выход которого подключен к первому входу второго элемента ИЛИ, при этом выход первого счетчика подключен к своему входу предварительной записи, входы уста-.. новки в нуль первого и второго счетчиков подключены к выходу установки нуля блока управления, отличающееся тем, что, с целью повы. шения точности преобразования частоты, в него дополнительно введены дешифратор, а также счетчик и счетчик с управляемым коэффициентом пересчета, входь| установки в нуль которых подключены к выходу установки нуля блока управления, причем управляющий, вход дополнительного дешифратора подключен к четвертому выходу блока управления, выход дополнительного дешифратора подключен к первому входу первого счетчика, а его информационные входы подключены к информационным выходам счетчика С: управляемым коэффициентом пересчета, вход которого подключен к выходу первого элемента И, а его управляющий выход подключен к второму входу первого сметчика, информационные выходы которого подключены к информационным входам дополнительного счетчика, первый управляющий вход которого подключен к выходу второго элемента И, а второй 1 управляющий вход подк/иочен к выходу второго элемента ИЛИ, второй вход О которого подключен к выходу дополнительного счетчика и второму входу сх третьего элемента И. ;о 2. Устройство по п, 1, отличающееся тем, что блок управ.ления содержит компаратор, два элемента И, два триггера, два формирователя, генератор импульсов,, выход которого является импульсньм выходом блока управления, а выход компаратора подключен к первому входу первого элемента И, выход которого подключен к первому входу первого триггера, а второй вход подключен к нулевому выходу второго триггера и neo.BQ-. му входу второго элемента И, выход которого является четвертым выходом

Изобретение относится к измерительной технике и может быть использо вано в цифровых устройствах, занятых обработкой (вычислением интеграль ных характеристик) аналоговых сигналов, а также в качестве измерительного прибора, позволяющего измерять период входных сигналов и вырабатывать последовательность импульсов с частотой следования,.обратно пропорциональной периоду входного сигнала.

Известно устройство, содержащее генератор эталонной частоты, формирующее устройство, блок управления, управляемые вентили, делители.частоты регистр и схему переноса, которые позволяют выполнить функции преобразователя период-частота Л .

Однако в указанном устройстве наличие, одного (неуправляемогь) источника опорной частоты значительно сужает частотный диапазон входных сигналов. Кроме того, указанным устройствам присущи большие погрешности, уменьшение значений которых требует значительного сравнимого с объемом основного устройства, дополнительного оборудования.

Наиболее близким к предлагаемому является устройство, содержащее блок (блок управления), три элемента И. первый и второй счетчики, дешифратор, блок элементов И, делитель, два элемента ИЛИ и второй блок элементов И 2 .

Известное устройство позволяет обеспечить постоянство относительной погрешности преобразования в достаточно широком частотной диапазоне.

Недостатки, известного устройства наличие инструментальной ошибки, возникающей вследствие конечного времени распространения сигнала из-за иск жения. состояния делителя при соответствующих его установках (запись дополнительного кода в младшие разря ды и др.) , ошибка преобразования ограничена сверху в каждом-i -ом диапазоне весом младшего разряда первого суетчика, ввиду конструктивны : особенностей затруднено изменение коэффициентов передачи преобразователя в широких пределах.

Указанные- недостатки существенно снижают то ность преобразований и область применения известных устройств.

Цель изобретения - повышение точности (преобразования частоты.

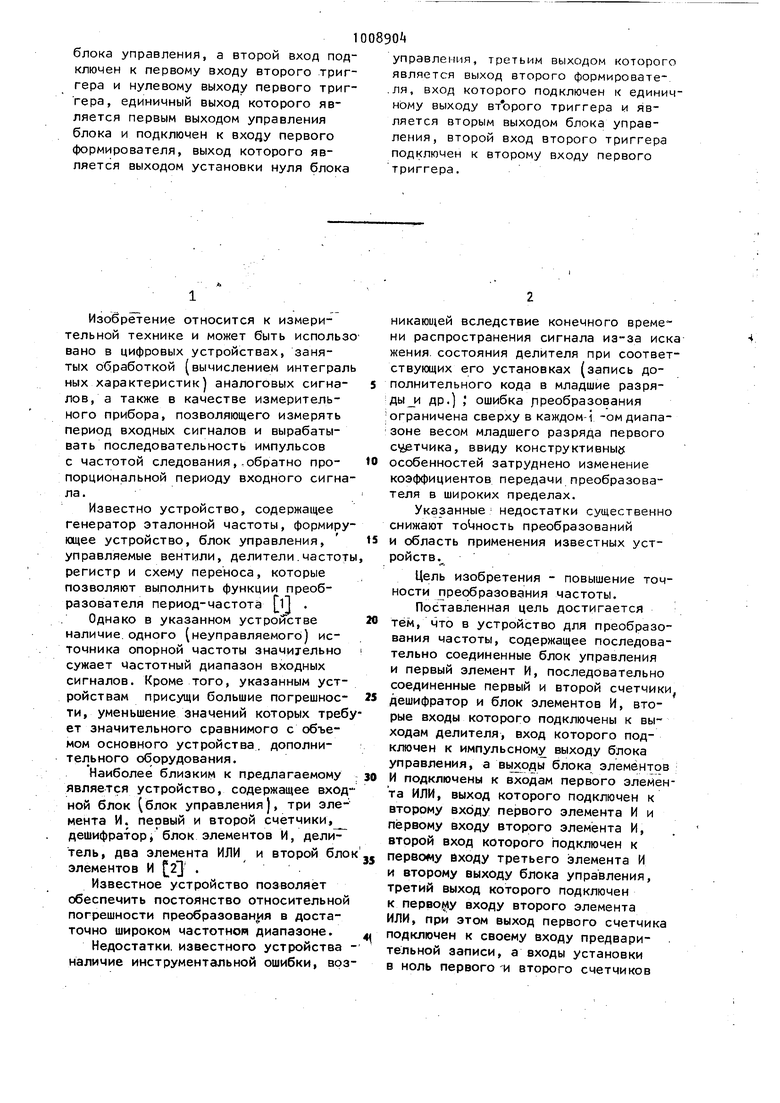

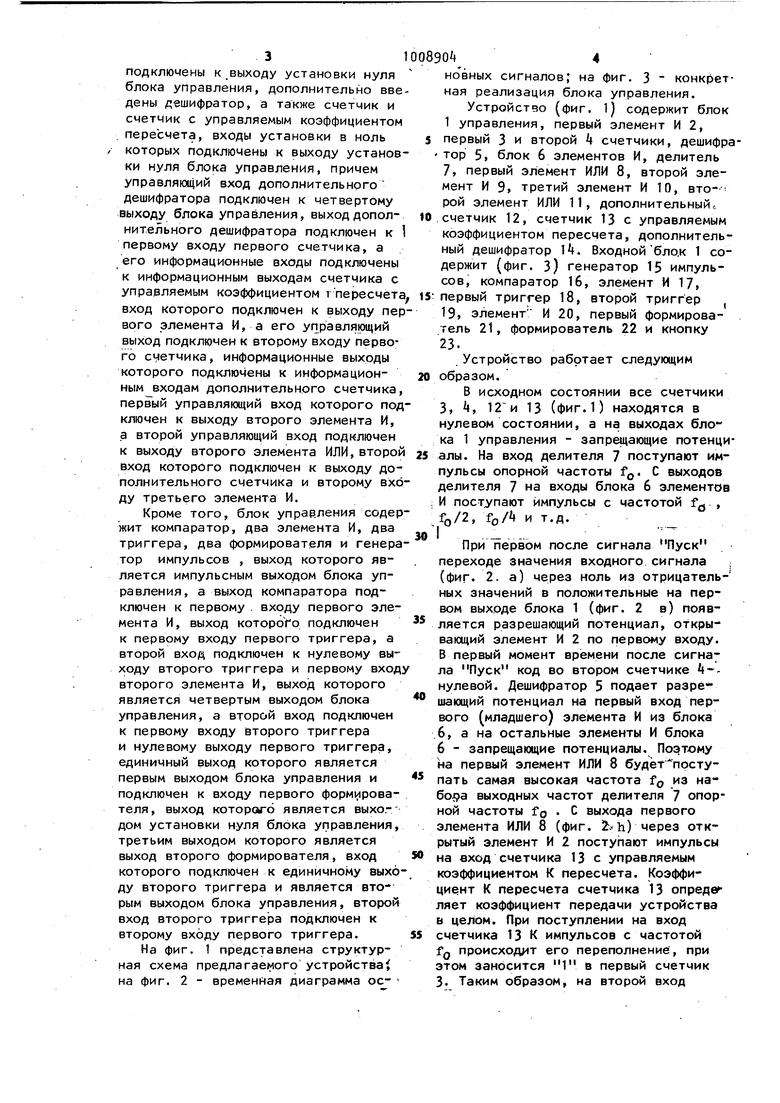

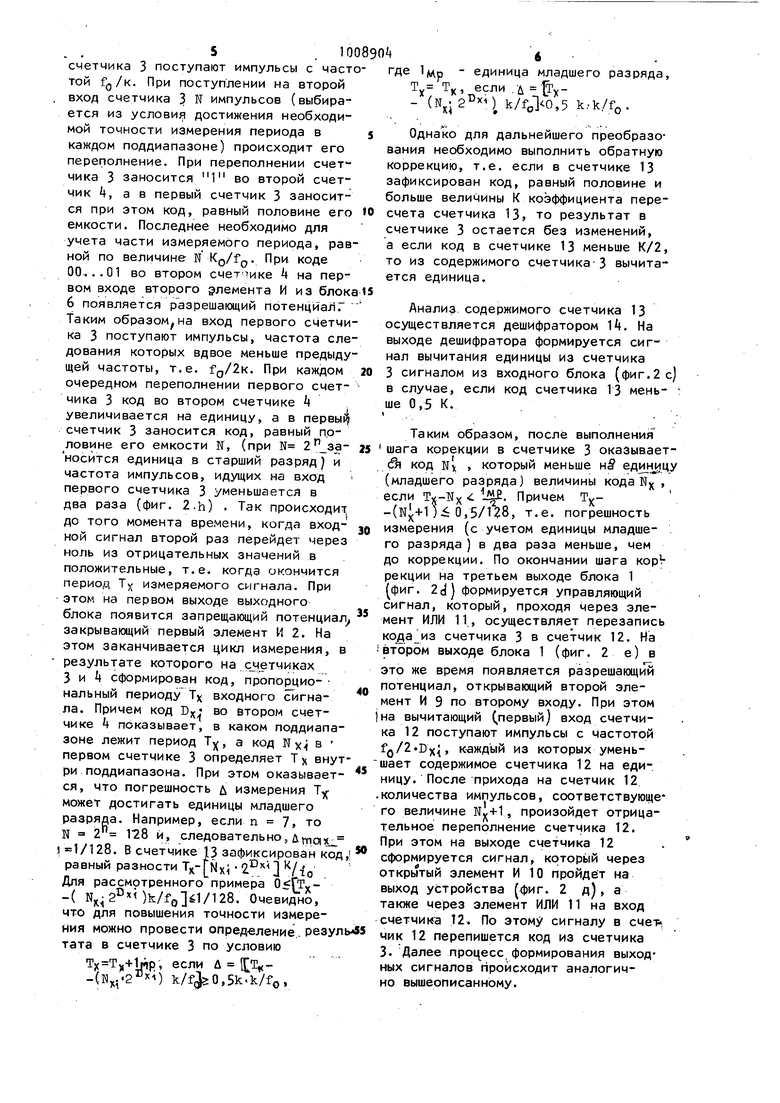

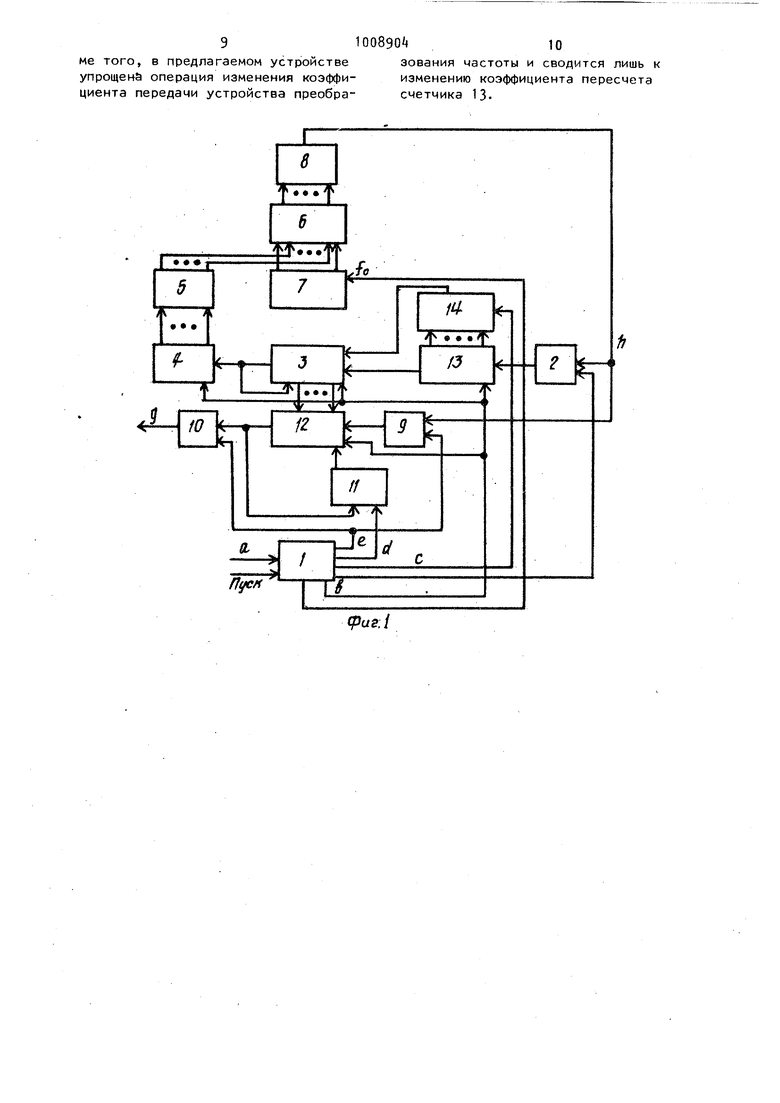

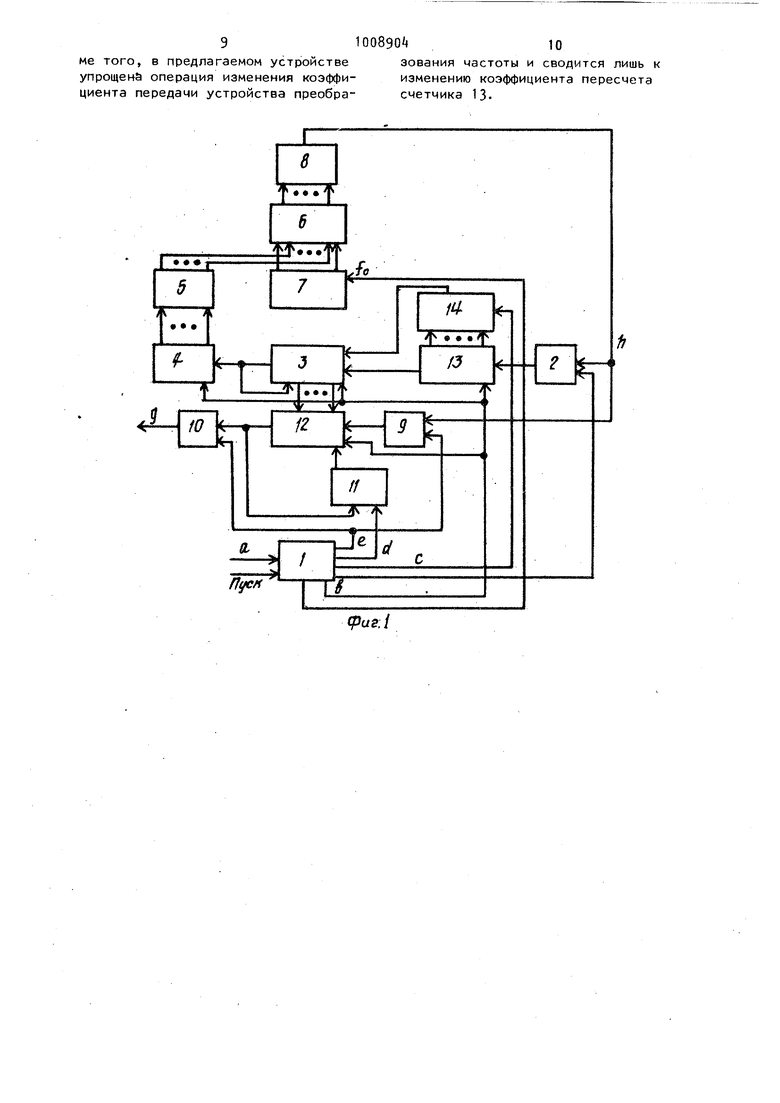

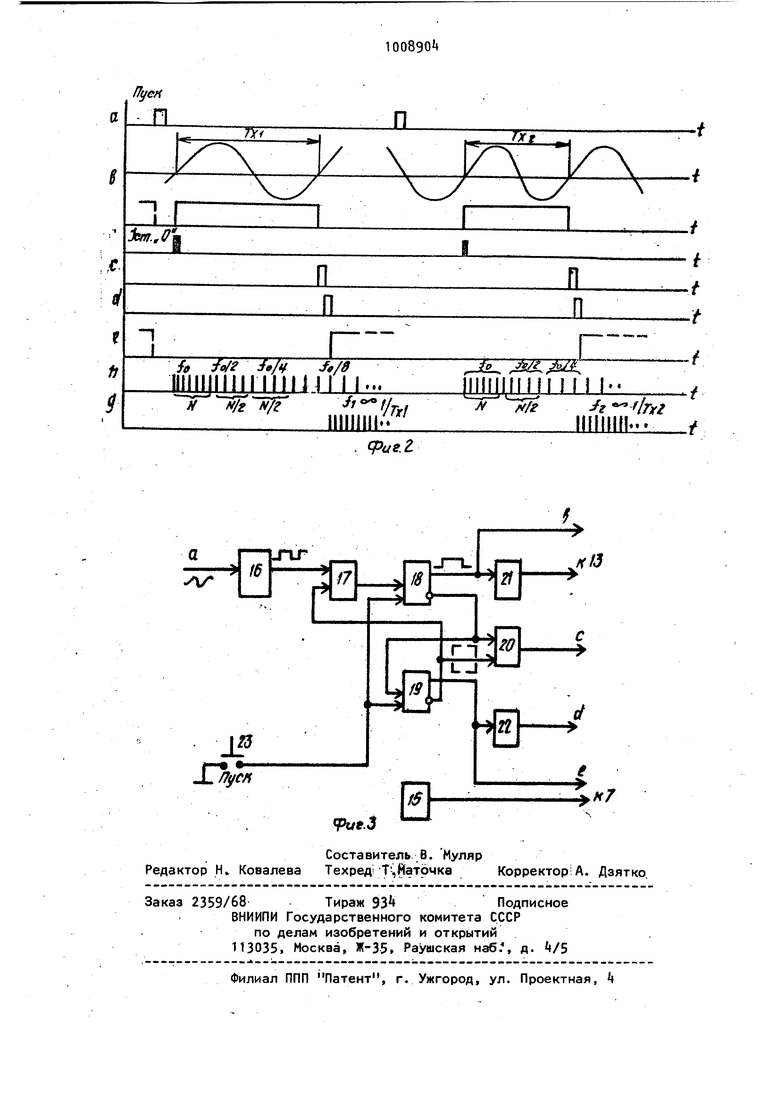

Поставленная цель достигается тем, что в устройство для преобразования частоты, содержащее последовательно соединенные блок управления и первый элемент И, последовательно соединенные первый и второй счетчики дешифратор и блок элементов И, вторые входы которого подключены к выходам делителя, вход которого подключен к импульсному выходу блока управления, а блока элемёнтсзв И подключены к входам первого элемента ИЛИ, выход которого подключен к второму входу первого элемента И и первому входу второго элемента И, второй вход которого подключен к первому входу третьего -элемента И и второму выходу блока управления, третий выход которого подключен к nepBOi y входу второго элемента ИЛИ, при этом выход первого счетчика подключен к своему входу предварительной записи, а входы установки в ноль первого И второго счетчиков подключены к.выходу установки нуля блока управления, дополнительно вве дены дешифратор, а также счетчик и счетчик с управляемым коэффициентом . пересчета, входы установки в ноль которых подключены к выходу установ ки нуля блока управления, причем управляющий вход дополнительного дешифратора подключен к четвертому выходу блока управления, выход дополнительного дешифратора подключен к первому входу первого счетчика, а его информационные входы подключены к информационным выходам счетчика с управляемым коэффициентом г пересчета вход которого подключен к выходу пер аого элемента И, а его управлякмций выход подключен к второму входу первого счетчика, информационные выходы которого подключены к информационным входам дополнительного счетчика, первый управляющий вход которого под ключен к выходу второго элемента И, а второй управляющий вход подключен к выходу второго элемента ИЛИ, второй вход которого подключен к выходу дополнительного счетчика и второму вхо ду третьего элемента И. Кроме того, блок управления содер жит компаратор, два элемента И, два триггера, два формирователя и генера тор импульсов , выход которого является импульсным выходом блока управления, а выход компаратора подключен к первому вхсэду первого элемента И, выход которого подключен к первому входу первого триггера, а второй вхой подключен к нулевому выходу второго триггера и первому вход второго элемента И, выход которого является четвертым выходом блока управления, а второй вход подключен к первому входу второго триггера и нулевому выходу первого триггера, единичный выход которого является первым выходом блока управления и подключен к входу первого формирователя, выход KOTOpcjro является выхо,дом установки нуля блока управления, третьим выходом которого является выход второго формирователя, вход которого подключен к единичному выхо ду второго триггера и является вторым выходом блока управления, второй вход второго триггера подключен к второму входу первого триггера. На фиг. 1 представлена структурная схема предлагаемого устройстваi на фиг. 2 - временная диаграмма основных сигналов; на фиг. 3 конкретная реализация блока управления. Устройство (фиг. 1) содержит блок 1 управления, первый элемент И 2, первый 3 и второй k счетчики, дешифратор 5, блок 6 элементов И, делитель 7, первый элемент ИЛИ 8, второй элемент И 9, третий элемент И 10, второй элемент ИЛИ 11, дополнительный,, счетчик 12, счетчик 13 с управляемым коэффициентом пересчета, дополнительный дешифратор . Входнойблок 1 содержит (фиг. З) генератор 15 импульсов, компаратор 16, элемент И 17, первый триггер 18, второй триггер 19, элемент И 20, первый формировагель 21, формирователь 22 и кнопку 23. Устройство работает следующим образом. В исходном состоянии все счетчики 3, , 12 и 13 (фиг.1) находятся в нулевом состоянии, а на выходах блока 1 управления - запрещающие потенциалы. На вход делителя 7 поступают импульсы опорной частоты Гд. С выходов делителя 7 на входы блока 6 элементов И поступают импульсы с частотой f , fo/2, fo/Ц и т.д. При первом после сигнала Пуск переходе значения входного сигнала (фиг. 2. а) через ноль из отрицательных значений в положительные на первом выходе блока 1 (фиг. 2 в) появляется разрешающий потенциал, открывающий элемент И 2 по первому входу. В первый момент времени после сигнала Пуск код во втором счетчике Ц-нулевой. Дешифратор 5 подает разрешающий потенциал на первый вход первого (младшего) элемента И из блока 6, а на остальные элементы И блока 6 - запрещающие потенциалы. Поэтому на первый элемент ИЛИ 8 будет поступать самая высокая частота f из на6oj a выходных частот делителя 7 опорной частоты fo . С выхода первого элемента ИЛИ 8 (фиг. 2.-h) через открытый элемент И 2 поступают импульсы на вход счетчика 13 с управляемым коэффициентом К пересчета. Коэффициент К пересчета счетчика 13 опредв ляет коэффициент передачи устройства в целом. При поступлении на вход счетчика 13 К импульсов с частотой TQ пpoиcxoд т его переполнение, при этом заносится 1 в первый счетчик 3. Таким образом, на второй вход 5. Ю счетчика 3 поступают импульсы с част той . При поступлении на второй , вход счетчика 3 N импульсов (выбирается из условия достижения необходимой точности измерения периода в каждом поддиапазоне) происходит его переполнение. При переполнении счетчика 3 заносится 1 во второй счетчик k, а в первый счетчик 3 заносится при этом код, равный половине его емкости. Последнее необходимо для учета части измеряемого периода, рав ной по величине N Ко/Г. При коде 00.. .01 во втором 4 на первом входе второго элемента И из блок 6 появляется разрешающий потенцйалГ Таким образом,на вход первого счетчи ка 3 поступают импульсы, частота еле дования которых вдвое меньше предыду щей частоты, т.е. Гд/2к. При каждом очередном переполнении первого счетчика 3 код во втором счетчике 4 , увеличивается на единицу, а в первы счетчик 3 заносится код, равный прловине его емкости N, {при N- 2 заносйтся единица в старший разряд) и частота импульсов, идущих на вход первого счетчика 3 уменьшается в два раза (фиг. 2.h) . Так происходит до того момента времени, когда входной сигнал второй раз перейдет через ноль из отрицательных значений в положительные, т.е. когда окончится период TX измеряемого сигнала. При этом на первом выходе выходного блока появится запрещающий потенциал закрывающий первый элемент И 2. На этом заканчивается цикл измерения, в результате которого на счетчиках 3 и i сформирован код, пропорцио- нальный периоду TX входного clirHaла. Причем код во втором счет.. чике i показывает, в каком поддиапазоне лежит период Т, а код NX-J в первом счетчике 3 определяет TX внут ри поддиапазона. При этом оказывается, что погрешность д измерения Т может достигать единицы младшего разряда. Например, если п 7, то N 2 128 и, следовательно, U ,;( J 1/128. В счетчике 13 зафиксирован код равный разности T -fNxi lin Для рассмотренного примера O Uv-( )k/fo 6l/128. Очевидно, что для повышения точности измерейия можно провести определение . резул тата в счетчике 3 по условию Т)(+1мр, если U () ,5k.k/fo, где - единица младшего разряда, Т.. Т, если . - () ,5 k..k,/fo. Однако для дальнейшего преобразования необходимо выполнить обратную коррекцию, т.е. если в счетчике 13 зафиксирован код, равный половине и больше величины К ко;эффициента пересчета счетчика 13, то результат в счетчике 3 остается без изменений, а если код в счетчике 13 меньше К/2, то из содержимого счетчика-3 вычитается единица. Анализ, содержимого счетчика 13 осуществляется дешифратором 1А. На выходе дешифратора формируется сигнал вычитания единицы из сметчика 3 сигналом из входного блока (фиг.2 с) в случае, если код счетчика 13 мень- : ше 0,5 К. Таким образом, после выполнения шага корекции в счетчике 3 оказывает код NX , который меньше н единицу (младшего разряда) величины кода N , если : 1J|H. Причем (NJ,+1) i 0,5/128, т.е. погрешность измерения (с учетом единицы младше- . го разряда ) в два раза меньше, чем до коррекции. По окончании шага KopV рекции на третьем выходе блока 1 фиг. 2d) формируется управляющий сигнал, который, проходя через . , ..,.. мент ИЛИ IV, осуществляет перезапись счетчика 3 в счетчик 12. На втором выходе блока 1 (фиг. 2 е) в это же время появляется разрешающими потенциал, открывающий второй элемент И 9 по второму входу. При этом на вычитающий (первый) вход счетчи а 12 поступают импульсы с частотой f /2.БхЬ каждый из которых уменьщает содержимое счетчика 12 на единицу. После прихода на счетчик 12 количества импульсов, соответствующего величине N.,+1, произойдет отрицательное переполнение счетчика 12. При этом на выходе счетчика 12 сформируется сигнал, крторь1Й через открьтый элемент И 10 пройдёт на выход устройства (фиг. 2 д), а также через элемент ИЛИ 11 на вход счетчика 12. По этому сигналу в счеть чик 12 перепишется код из счетчика 3.Далее формирования выходных сигналов происходит аналогично вышеописанному. Коэффициент передачи устройства определяется как io/Nx- вых/Чх О X Следовательно, число выходных импульсов не зависит от величины периода входного сигнала и определяется лишь коэффициентом пересчета счетчика 13. Как следует из описания функционирования устройства преобразования частоты фиг. 1) порядок работы его блоков определяется сигналами, формируемыми в блоке 1 управления в соответствии с временной диаграммой фи г. 2). Устройство работает следующим образом. На бход компаратора.16 (фиг. З) поступает периодический сигнал фиг. 2 а). В качестве компаратора может быть использован например, триггер Шмитта. На выходе компаратора 16 формируется также периодический сигнал с тем же периодом, но форма его соответствует сигналам, используемым в цифровых логических элементах. Этот сигнал поступает.на первый вход элемента И 17. При нажатии кнопки 23 (формируется сигнал Пуск ;триггеры 18 и 19 устанавливаются в ноль. При этом сигнал с нулевого выхода триггера .19 открывает элемент И 17 для прохождения сигнала с выхода Компаратора 16 на первый вход триггера 18. Первый вход триггера 18 является счетным входом, т.е. каждый переход сигнала на этом входе из нуля в единицу переводив триггер-18 в противоположное состояние. Первый после CHrHd Ли Пуск переход из нуля в единицу указанного сигнала переводит триггер 18 в единичное положение. При этом сигнал ня единичном выходе триг гера 18 соответствует 1 Гфиг. 2;в) В то же время из перехода ноль - eAV . ница (передний фронт) формирователь 21 формирует сигнал установки в ноль счетчиков 3, t, 12 и 13. Таким образом-, по переднему фронту входного сигнала сигналом, формируемым бло ком 1, асе счетчики 3, , 12 и 13 устанавливаются в исходное (нулевое) СОСТОЙ ние. В момент окончания первого периода входного сигнала (очередным передним фронтом) триггер 18 переводит ся в нулевое состояние. Сигнал на . его единичном выходе (фиг. 2 в) меняется с единицы на ноль. Сигнал на нулевом выходе триггера 18 изменяется с нуля на единицу. Этот передний фронт сигнала поступает на первый (счетный) вход триггера 19 и переводит его в единичное положение. Сигнал на единичном выходе триггера 19 изменяется с нуля на единицу (фиг.2е) Формирователь 22 формирует из этого переднего фронта импульс (фиг. 2.3) На выходе элемента И 20 появляется сигнал в том случае, когда триггеры 18 и 19 находятся в состоянии нуля.Первый раз этот сигнал мируется сразу же после нажатия кнопки, но до форг мирования сигнала установки счетчиков в ноль, т.е. этот сигнал на работу схемы не влияет. Второй раз на выходе элемента И 20 формируется короткий импульс, длительность которого равна времени задержки сигнала в . . триггере 19 ((фиг. 2. с). Для предлагаемого устройства такая длительность импульса обеЙ1ечивает надежную работу устройства. Если же для какой-либо реализации длительность импульса будет недостаточной, то в цепь между нулевым выходом 7 иггера 19 и первым входом элемента И 20 «ожно ввести &лёмент задержки. На фиг. .3 этот элемент задержки показан пунктиром. В качестве формирователей 21 и 22, генератора 15 импульсов и счетчика 13 с / управляемым коэффициентом пересчета может быть использовано любое из известных устройств. В качестве делителя 7 быть использован, например, двоичный счетчик, так как у двоичных счётчиков . частота сигнала на выходе каждого последующего триггера в два раза меньше , чем на выходе предыдущего. . Таким образом, введение новых функциональных блоков и связей позволяет повысить точность преобразования, а именно: уменьшить максимальное значение абсолютной ошибки в два раза, устранить инструментальную Ошибку, возникающую вследствие конечного времени распространения сигнала в делителе при соответствующих становках «его .8 исходное состояние например, запись дополнительного ода в младшие разряды и др.) .оКро9100890 10

ме того, в предлагаемом устройстве зования частоты и сводится лишь к упрощенй операция изменения коэффи- изменению коэффициента пересчета циента передачи устройства преобра- счетчика 13.

(pas: i

Авторы

Даты

1983-03-30—Публикация

1981-11-23—Подача