11 Изобретение относится к электрони ке и вычислительной технике и может быть использовано при построении арифметических устройств. Известен полусумматор, содержащий 7 МДП-транзисторов р-типа lj . Недостатком указанного элемента является повышенное потребление мощности в связи с тем, что устройство выполнено на транзисторах одного типа 1 Известен полусумматор на МДП-тран зисторах, содержащий первый, второй третий и четвертый МДП-транзисторы р-типа и пятый, шестой, седьмой и .восьмой МДП-транзисторы 1п-типа, при этом стоки первого, третьего и четвертого транзисторов подключены соответственно к стокам пятого, шестого и седьмого, сток второго транзис тора подключен к выходной шине и . стоку шестого транзистора, затворы первого и пятого транзисторов подключены к первой входной шине, четвертого и седьмого - к второй, треть его и шестого - к стокам четвертого и седьмого, второго и восьмого - к стЬкам первого и пятого транзисторов истоки первого, второго, третьего и четвертого транзисторов подключены к шине питания, исток пятого транзис тора - к второй входной шине, исток шестого - к стоку восьмого, исток седьмого транзистора подключен к первой входной шине, исток восьмого транзистора - к общей шине ,2 . Недостатком известного элемента является низкое быстродействие в связиС. тем, что заряд емкости, об разованный стоками первого и пятого четвертого и седьмого пар транзисторов через открытые транзисторы пя тый и седьмой при комбинации входны сигналов А 1, В 1 осуществляетс только дп уровня Е-ипрр где Е ПОР t где уровень напряжения, соответствущии Ипо пороговое напряжение транзистора tt-типа, ( -коэффициент влияния подложки транзистора f -типа причем указанный уровень меньше уровня 1. Таким образом, на затво рах шестого и восьмого транзисторов устанавливаются уровни напряженияменьшие, чем уровень напряжения 1 что приводит к неполному отпиранию последних, тем самым, k увеличению времени формирования на выходной ши не уровни напряжения, соответствующ го 0 Цель изобретения - повышение быстодействия устройства. Поставленная цель достигается ем,что в полусумматор на МДП-транзисорах, содержащий первый., второй, ретий и четвертый МДП-транзисторы -типа и пятый, шестой, седьмой и осьмой МДП-транзисторы , при том стоки первого третьего и четверого транзисторов подключены соответтвенно к стокам пятого, шестого и едьмого транзисторов, сток второго ранзистора подключен к первой вы- . одной шине, затворы первого и пятого транзисторов подключены к первой входной, шине, четвертого и седьмого к второй, третьего и шестого - к стокам четвертого и седьмого транзисторов, исток второго транзистора подключен к истоку третьего транзистора, и сток четвертого - к шине питания, . веден девятый МДП-транзистоо. П-типа, причем истоки первого, шестого и затворы второго, девятого транзисторов подключены к второй шине, истоки восьмого, девятого, второго и третьего транзисторов подключены к первой входной шине, исток седьмого к общей шине, затвор восьмого и исток пятого - к затвору третьего транзистора, стоки первого и второго транзисторов подключены к стоку восьмого, а стоки девятого, шестого и третьего транзисторов - к второй выходной шине. На чертеже представлена электрическая принципиальная схема предлагаемого устройства. Устройство содержит МПД-транзисторы 1-4 р-типа и МДП-транзисторы 5 9 п-типа. Стоки первого, третьего и четвертого транзисторов подключены соответственно к стокам пятого, шестого и седьмого. Затворы первого и пятого транзисторов и истоки второго и третьего, восьмого и девятого транзисторов подключены к первой входной шине.10, на которую поступает входной сигнал А. Затворы транзисторов 2, 9, 4 и 7 и истоки транзисторов 1, 6, 7 подключены к второй входной шине 11, на которую поступает входной сигнал В. Исток транзистора подключен к шине 12 питания, а исток транзистора 7 к общей шине 13. Стоки транзисторов 1, 2, 5 и 8 подключены к первой выходной шине 14, на которой формируется сиг нал S . Стоки транзисторов 3, 6 и

9 подключены к второй выходной шине 15, на которой формируется сигнал Р.

Устройство работает следующим образом.

При комбинации входных сигналов А 0, В О закрыты транзисторы

1и 5 и через открытые транзисторы

2и 8 на шине И формируется сигнал S О, через открытый транзистор 6

формируется сигнал на шине 15- Р 0 При комбинации входных сигналов А 0, В 1 закрыты второй, пятый и восьмой транзисторы и на шине 14 формируется сигнал S - 1 через открытый транзистор 1, на шине 15 формируется сигнал Р 0., через открытые третий и девятый транзисторы, , транзистор 6 при этом закрыт. При

комбинации входных сигналов А 1, В О закрыты первый, седььюй, девятый И .третий транзисторы. Сигнал S 1 на шине И формируется через открытые второй и восьмой транзисторы, а на шине 15 формируется сигнал Р О через открытый транзистор 6. При комбинации входных сигналов А 1, В - 1 закрыты первый, второй,четвертый, шестой . и восьмой транзисторы. На шине Н формируется сигнал через открытый транзистор 5. На выходной шине 15 формируется сигнал Р 1 через открытые транзисторы J и 9.

i

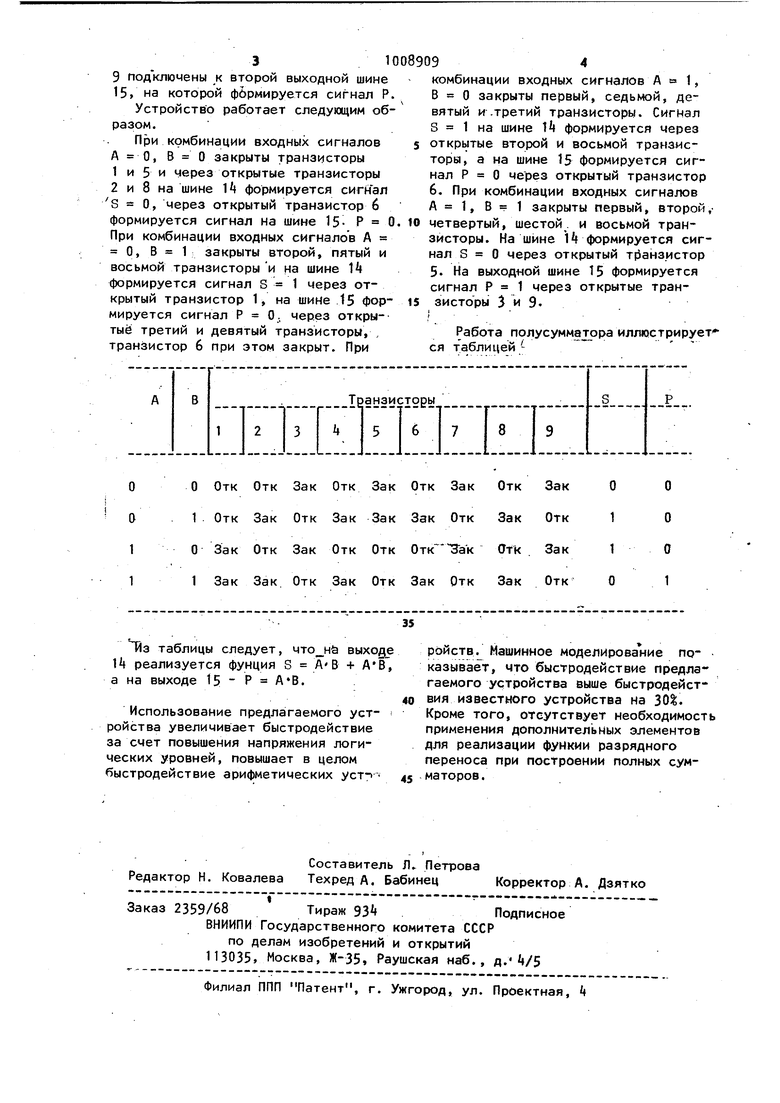

Работа полусумматора иллюстрирует

ся таблицей

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый мажоритарный элемент | 1982 |

|

SU1069167A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| Тактируемый Е-триггер | 1987 |

|

SU1492454A1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

таблицы следует, выходе Ц реализуется фунция S АВ + , а на выходе 15 Р . Использование предлагаемого устройства увеличивает быстродействие за счет повышения напряжения логических уровней, повышает в целом быстродействие арифметических уст-i ройств. Машинное моделирование показывает, что быстродействие предлагаемого устройства выше быстродейстВИЯ известного устройства на 30. Кроме того, отсутствует необходимость применения дополнительных элементов для реализации функии разрядного переноса при построении полных сумматоров.

Авторы

Даты

1983-03-30—Публикация

1981-11-18—Подача