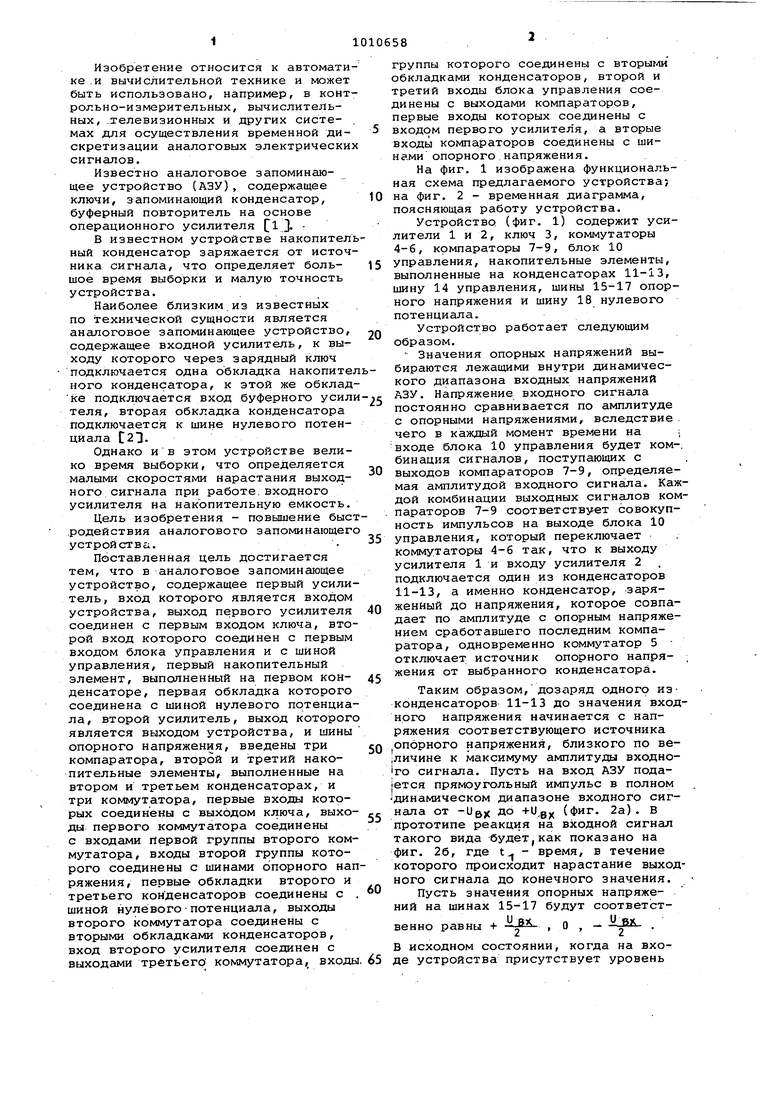

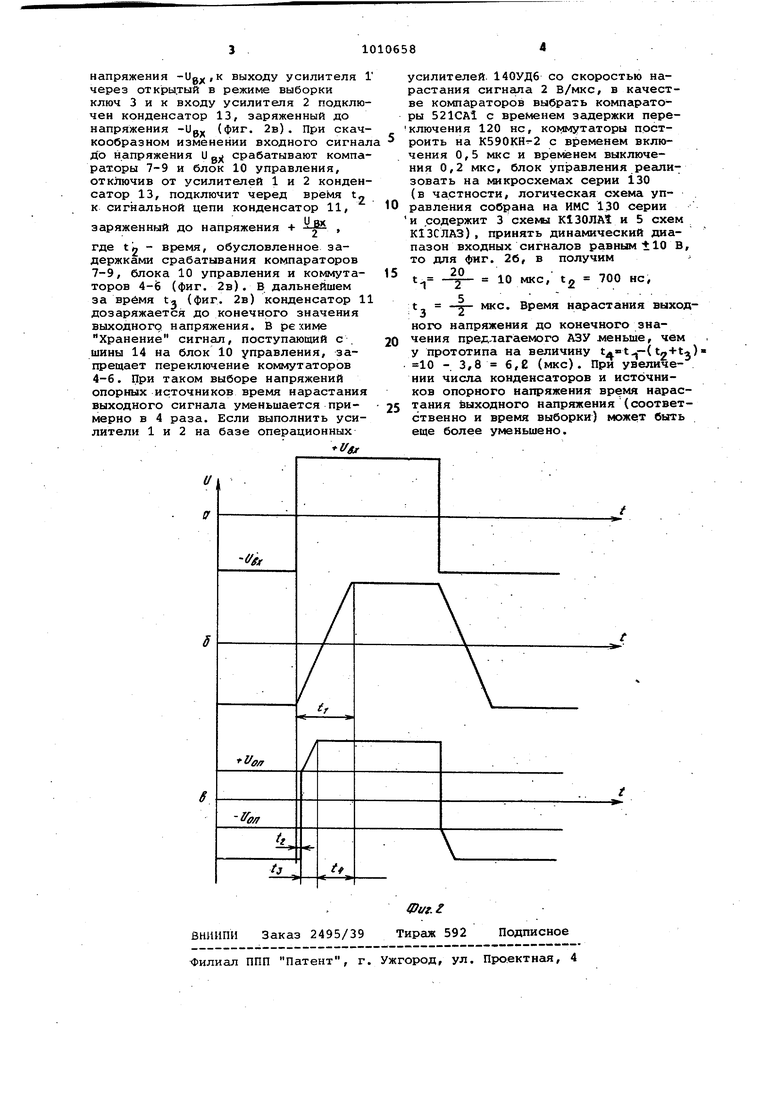

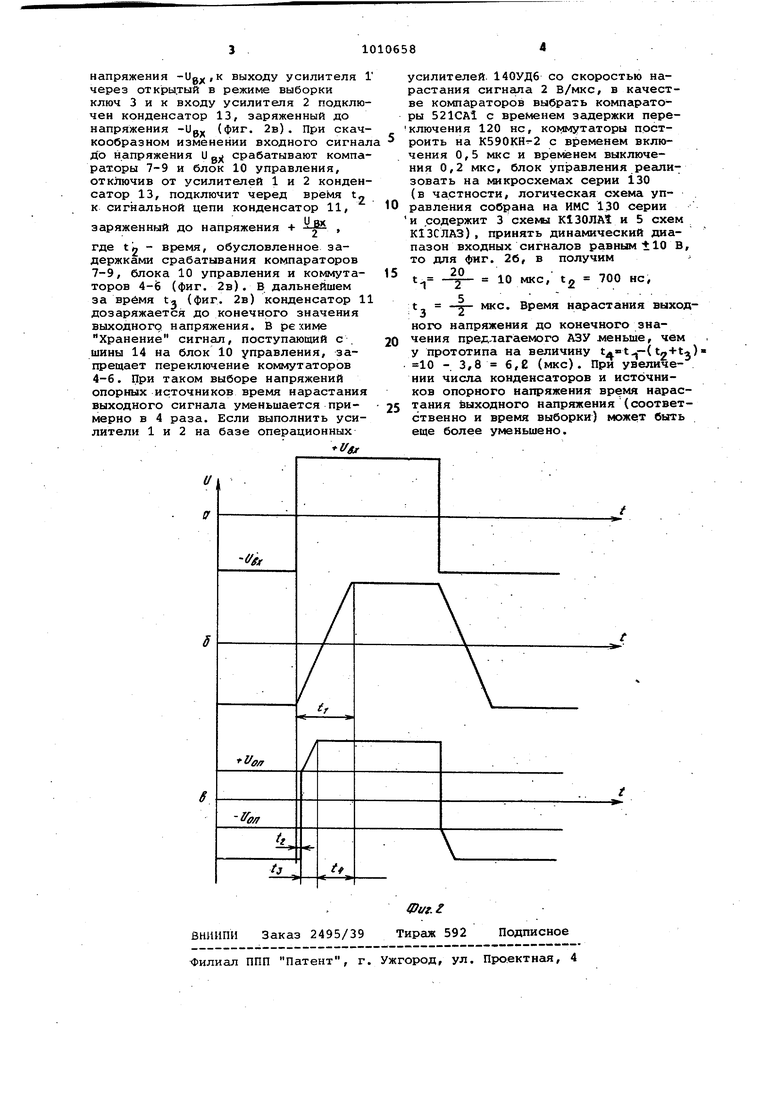

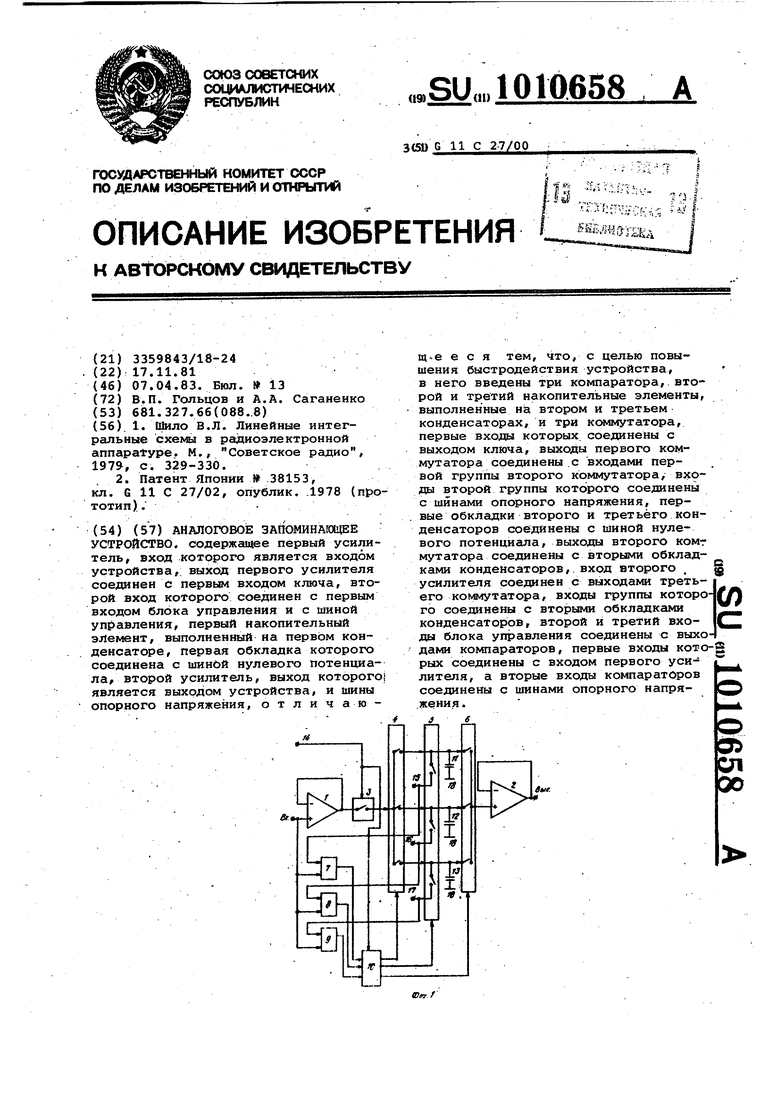

Изобретение относится к автомати ке .и вычислительной технике и может быть использовано, например, в конт рольно-измерительных, вычислительных, .телевизионных и других системах для осуществления временной дискретизации аналоговых электрически сигналов. Известно аналоговое запоминающее устройство (АЗУ), содержащее ключи, запоминающий конденсатор, буферный повторитель на основе операционного усилителя В известном устройстве накопител ный конденсатор заряжается от источ ника сигнала, что определяет большое время выборки и малую точность устройства. Наиболее близким из известных по технической сущности является аналоговое запоминающее устройство, содержащее входной усилитель, к выходу которого через зарядный ключ подключается одна обкладка накопите ного конденсатора, к этой же обклад ке подключается вход буферного усил теля, вторая обкладка конденсатора подключается к шине нулевого потенциала СзЗ. Однако ив этом устройстве велико время выборки, что определяется малыми скоростями нарастания выходного сигнала при работе.входного усилителя на накопительную емкость. Цель изобретения - повышение быс .родействия аналогового запоминающег устройства.. Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый усили тель, вход которого является входом устройства, выход первого усилителя соединен с первым входом ключа, вто рой вход которого соединен с первым входом блока управления и с шИной управления, первый накопительный элемент, выполненный на первом конденсаторе, первая обкладка которого соединена с шиной нулевого потенциа ла, второй усилитель, выход которог является выходом устройства, и шины опорного напряжения, введены три компаратора, второй и третий накопительные элементы, выполненные на втором и третьем конденсаторах, и три коммутатора, первые входы которых соединены с выходом ключа, выходы первого коммутатора соединены с входами Первой группы второго коммутатора, входы второй группы которого соединены с шинами опорного нап ряжения, первые обкладки второго и третьего конденсаторов соединены с шиной нулевого потенциала, выходы второго коммутатора соединены с вторыми обкладками конденсаторов, вход второго усилителя соединен с выходами третьего KONtMyTaTopa, входы группы которого соединены с вторыг-ш обкладками конденсаторов, второй и третий входы блока управления соединены с выходами компараторов, первые входы которых соединены с входом первого усилителя, а вторые входы компараторов соединены с шинами опорного напряжения. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма, поясняющая работу устройства. Устройство, (фиг. 1) содержит усилители 1 и 2, ключ 3, коммутаторы 4-6, компараторы 7-9, блок 10 управления, накопительные элементы, выполненные на конденсаторах 11-13, шину 14 управления, шины 15-17 опорного напряжения и шину 18 нулевого потенциала. Устройство работает следующим образом. Значения опорных напряжений выбираются лежащими внутри динамического диапазона входных напряжений АЗУ. Напряжение входного сигнала постоянно сравнивается по амплитуде с опорными напряжениями, вследствие чего в каждый момент времени на ; входе блока 10 управления будет ком-, бинация сигналов, поступающих с выходов компараторов 7-9, определяемая амплитудой входного сигнала. Каждой комбинации выходных сигналов компараторов 7-9 соответствует совокупность импульсов на выходе блока 10 управления, который переключает коммутаторы 4-6 так, что к выходу усилителя 1 и входу усилителя 2 подключается один из конденсаторов 11-13, а именно конденсатор, заряженный до напряжения, которое совпадает по амплитуде с опорным напряжением сработавшего последним компаратора, одновременно коммутатор 5 отключает источник опорного напряжения от выбранного конденсатора. Таким образом, дозаряд одного изконденсаторов 11-13 до значения входного напряжения начинается с напряжения соответствующего источника опорного напряжения, близкого по величине к максимуму амплитуды входного сигнала. Пусть на вход АЗУ подается прямоугольный импульс в полном Динамическом диапазоне входного сигнала от -Uej{ до +U,gj( (фиг. 2а) . В прототипе реакция на входной сигнал такого вида будет,как показано на фиг. 26, где t - время, в течение которого происходит нарастание выходного сигнала до конечного значения. Пусть значения опорных напряжений на шинах 15-17 будут соответственно равны + , О , - . исходном состоянии, когда на вхое устройства присутствует уровень

напряжения -Ug.K выходу усилителя Г через открытый в режиме выборки ключ 3 и к входу усилителя 2 подключен конденсатор 13, заряженный до напряжения -Ug (фиг. 2в). При скачкообразном изменении входного сигнал до напряжения U g срабатывают компараторы 7-9 и блок 10 управления, отключив от усилителей 1 и 2 конденсатор 13, подключит черед вреМя t к сигнальной цепи конденсатор 11,

заряженный до напряжения + -- ,

где trt время, обусловленное задержками срабатывания компараторов 7-9, блока 10 управления и коммутаторов 4-6 (фиг. 2в). В дальнейшем за время tj (фиг. 2в) конденсатор 1 дозаряжается до конечного значения выходного напряжения. В рехиме Хранение сигнал, поступающий с . шины 14 на блок 10 управления, запрещает переключение коммутаторов 4-6. При таком выборе напряжений опорных источников время нарастания выходного сигнала уменьшается примерно в 4 раза. Если выполнить усилители 1 и 2 иа базе операционных

У

I/

О

усилителей. 140УД6 со скоростью нарастания сигнала 2 В/мкс, в качестве компараторов выбрать компараторы 521СА1 с временем задержки переключения 120 не, коммутаторы построить на К590КН-2 с временем включения О,5 МКС и временем выключения 0,2 МКС, блок управления реализовать на микросхемах серии 130 (в частности, логическая схема управления собрана на ИМС 130 серии и содержит 3 схемы К130ЛА1: и 5 схем К13СЛАЗ), принять динамический диапазон входных сигналов равным ±10 В, то для фиг. 26, в получим

t 10 МКС, tg 700 НС,

t -4- МКС. Время нарастания выходного напряжения до конечного значения предлагаемого АЗУ меньше, чем у прототипа на величину (t2+tj)i 10 - 3,8 6,2 (мкс). При увеличении числа конденсаторов и источников опорного напряжения время нарастания выходного напряжения (соответственно и время выборки) может быть еще более уменьшено.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1984 |

|

SU1156142A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2006 |

|

RU2328011C2 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU963106A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2007 |

|

RU2354985C2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2006 |

|

RU2326474C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2007 |

|

RU2354986C2 |

АНАЛОГОВОЕ ЗАПОМИНАГОСЦЕЕ УСТРОЙСТВО, содержаилее первый усилитель, вход которого является входом устройства,: выход первого усилителя соединен с первьв4 входом ключа, второй вход которого соединен с первым входом блока управления и с шиной управления, первый накопительный элемент, выполненный на первом конденсаторе , первая обкладка которого соединена с шинбй нулевого потенциала, второй усилитель, выход которого; является выходом устройства, и шины опорного напряжения, отличающ-е е с я тем, что, с целью повышения быстродействия устройства, в него введены три компаратора, второй и третий накопительные элементы, выполненные Hk втором и третьемконденсаторах, и три кс 1мутатора, первые входы которых соединены с выходом ключа, выходы первого коммутатора соединены с входами первой группы второго коммутатора, входы второй группы которого соединены с шинами опорного напряжения, пер. вые обкладки второго и третьего конденсаторов соединены с шиной нулевого потенциала, выходы второго комг мутатора соединены с вторыми обкладками конденсаторов,. вход второго усилителя соединен с выходами треть(Л его коммутатора, входы группы которого соединены с вторыми обкладками конденсаторов, второй и третий входы блока управления соединены с выхоЧ дами компараторов, первые входы кото-2 рых соединены с входом первого уси- лителя, а вторые входы компараторов соединены с шинами опорного напряжения . J g эь СП эо fttr.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шило В.Л | |||

| Линейные интегральные схемы в радиоэлектронной annapafype | |||

| М., Советское радио, 1979, с | |||

| Букса для железнодорожного подвижного состава | 1922 |

|

SU329A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ извлечения антипирина | 1933 |

|

SU38153A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1983-04-07—Публикация

1981-11-27—Подача