(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1978 |

|

SU868752A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Множительно-сдвиговое устройство | 1982 |

|

SU1013951A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

1

Изобретение относится к области вычислительной техники, в частности к быстрЬ действующим ЦВМ.

Известно устройство для умножения, соаержащее регистры множимого, множителя, румматор и регистр резулнгата i

Недостатком известного устройства является малое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство для умножения, содержащее генератор кратных множимых, вькоцы которого подключены к первым группам входов коммутаторов, вторые группы входов которых подключены к соответствующим разрядным выходам регистра множителя. Выходы коммутаторов, кроме первого, подключены ко вторым соответствующим разрядным входам параллельных сумматоров. Во всех параллельных сумматорах выход переноса самого старшего разряда каждого сумматора подключен через элемент задержки к первому входу самого младшего разряда того же параллельного сумматора. К третьим входам всех параллельных сумматоров через элементы задержки подключены соответствующие вйхоцы сумм предыдущих параллельных сумматоров 21

Недостатком устройства является малое быстродействие.

Цель изобретения - повышение быстродействия.

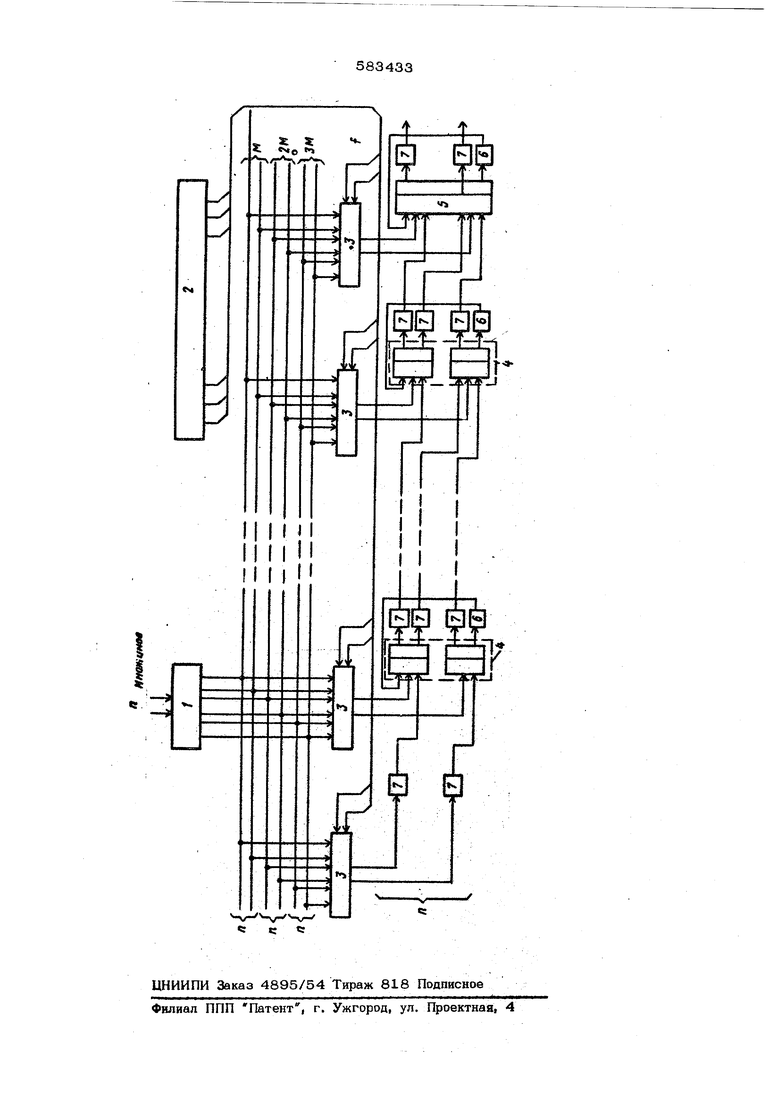

Эта цель достигается тем, что в предложенном устройстве параллелы ые сумматоры, кроме последнего, выполг ены без распространения переноса, а в устройство введены дополнительные элементы задержки по числу выходов переносов, не считая стар щих разрядов. Последний, параллельный сумматор выполнен с одновременным параллельным переносом. При этом выходы перено- . сов параллельных сумматоров без распространения переноса, кроме выхода перено; са старшего разряда каждого сумматора, через дополнительно введенные элементы задержки подключены к первым разрядным входам более старших разрядов последующих параллельных сумматоров. Выходы первого коммутатора подключены ко входам соответствующих элементов задерж-« ки, выходы которых подсоединены к соот ветствующим третьим разрядным входам первого параллельного сумматора без рас. простраиения переноса. Выходы паралпепь ого сумматора с одновременным паралпвпъкым переносом подключены fepes эле. менты задержки к соответствующим выходам устройства. На чертеже изображена схема устройства Устройство содержит генератор кратных множимых 1, регистр множителя 2, коммута-t : тор 3, параллельный сумматор без распространения переноса4, параллельный сумма тор с одновременным параллельным переносом 5, элементы задержки 6 и дополни- телыГые элементы задержки 7, Устройство работает следующим образом. Множитель хранится в регистре 2 в виде двоичного С|, -разрядного кода и обрабатывается f - разрядными группами (г -7 групп). Множимое псютупает двоичным последовательно-параллельным -разрядным кодом группами с « разрядов в кажд1 й параллелшо подаваемой группе (т ---групп на вход генератора 1.. С выхода генератора 1 в аналогичном последовательно-параллельном виде на одноименные входы каждого коммутатора 3 снимается ряд чисел типа К -Mj где М множимое, а К -числа натурального ряда от О до (2-1).Например, для трехразрядных групп множителя (f 3,2 - 1 7) генератор 1 формирует числа О, М, 2М, ЗМ, 4М, 5М/6М, 7М. На другие входы каждого коммутатора поступают по f разрядов множителя из рег стра 2, На выход каждого коммутатора проходит то число из ряда KI М ,К|которого совпадает с кодом группы множителя, поданной на вход данного коммутатора. Например, для случая f 3 при коде группы множителя 1О1 (что равно 5 в десятичной системе счисления) на выходе дан ного коммутатора будет число, равное 5М Таким образом, на выходах всех коммутаторов 3 одновременно в последовател1 рпараллельноМ:Виде формируется ряд частичных произведений множимого на соответствующие группы разрядов множителя, при сложении которых с учетом относительных сдвигов получается искомое полное произведение. Каждый сумматор 4 суммирует частичное произведение Kj М , поступающее с выхода соответствующего коммутатора крат ных множимых и коды с выходов предыдуш го сумматора, прошедшие через логическую задержку. Первый сумматор из-эа наличия. только одного операнда превращается фактически в секцию элементов зад:ержки б, Полное произведение формируется на выходах последнего сумматора 5, вьгаолвенного в виде п -разрядного сумматрра с параллельными переносами для получения последней суммы за один такт. Разряды сумматоров, кроме первого и последнего, состоят из одноразрядных ,cywматоров, не связанных между собой по целям переносов. Последние через элементы задержки Ь поступают на входы соответствующих более старших разрядов последую- ших сумматоро где учитываются в следую|цем такте. В результате такого учета переносов и формирования произведения при одинаковой элементной базе и разрядности операндов и групп (а соответственно и разрядности коммутаторов кратных множимых и секций сумматоров) быйт юдействие предлагаемого устройства повышается, в jM раз по сравнению с известным устройством - за счет увеличения предельно допустимой тактовой частоты (частоты синхронизации работы усрройства)., pMyjja изобретения Устройство для умножения содержаще генератор кратных множимых, выходы которого подключены к первым группам, вхо дов коммутаторов, вторые группы входов которых подключены., к соответствующим разрядным выходам регистра множителя выходы коммутаторов, кроме первого, подключены ко вторым соответствующим разрядным входам параллельных сумматоров, .во всех параллельных сумматорах выход переноса-,, самого старщего разряда каждого сумматора подключен через элемент задержки к первому входу самого младшего разряда того же параллельного сумматора, к третьим входам jBcex параллельных сумматоров через алементы задержки подключены соответствующие выходы сумм предыдущих параллельных сумматоров, отличаю щое -е с я тем, что, с целью повышения быстродействия, параллельные сумматоры, кроме последнего выполнены без распространения переноса, введены дополнительные элементы за-- . держки по числу выходов переносов, не счи тая старших разрядов, последний параллел ный сумматор выполнен с одновременным па| лельным переносом; при этом выходь1 пере носов параллельных сумматоров без распространения переноса, кроме выхода переноба старшего разряда каждого сумматора, подключены. через дополнительно введенные елементы задержки к первым разрядным входам более старших разрядов последук щих параллельных сумматоров; при атом выходы первого, коммутатора подключены ко входа соответствующих элементов задержки, выходы которых подсоединены к соответствующим третьим разрядным входам первого параллельного сумматора без распространения переноса, выходы параллельгi ЕОГО сумматора с одновременным параллель 1кым переносом подключены через элементы задержки к соответствующим выходам устройства. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 451079 S06 Р 7/39, 18.04.73. v2. Ричарде Р. К. I Арифметические операции на цифровых вычислительных машинах, М., изд-во иностранной литературы 1957, стр. 170-175.

Авторы

Даты

1977-12-05—Публикация

1976-05-24—Подача