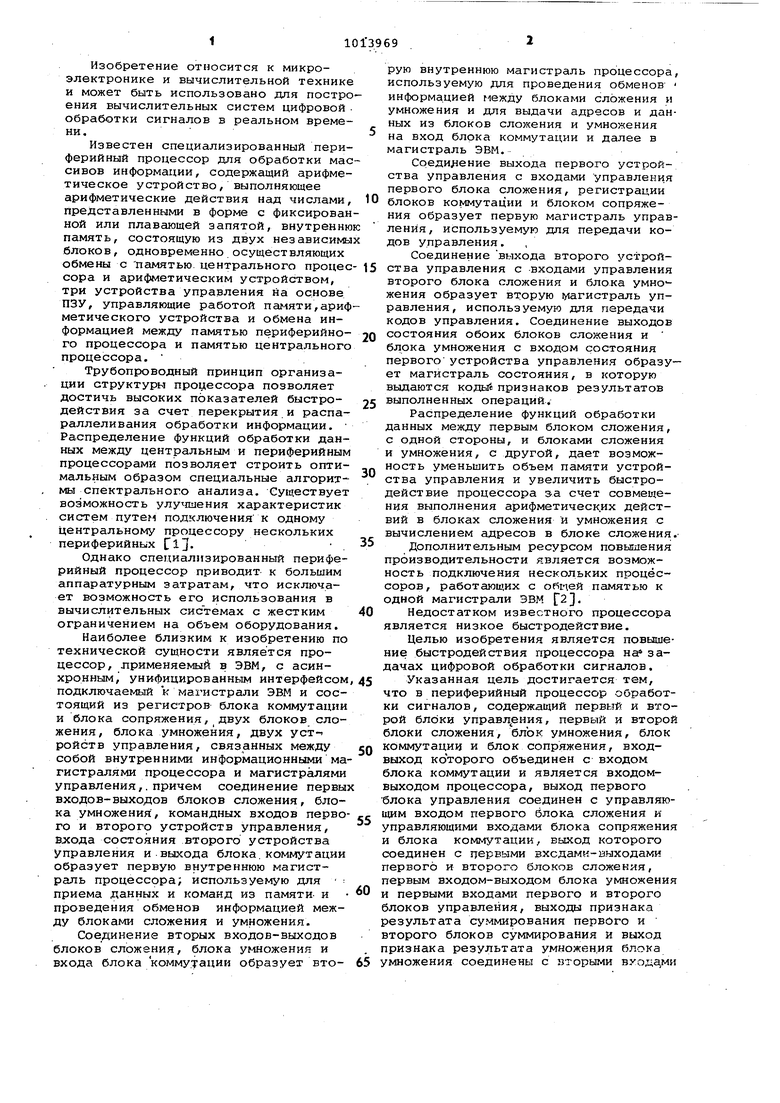

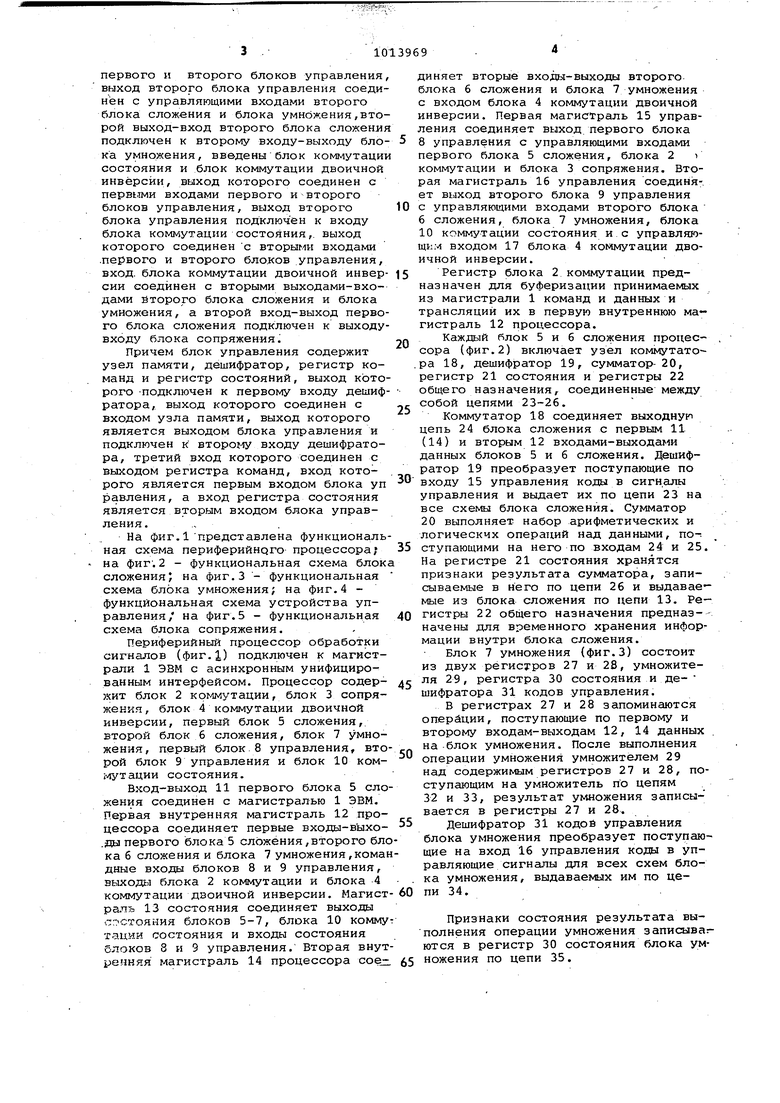

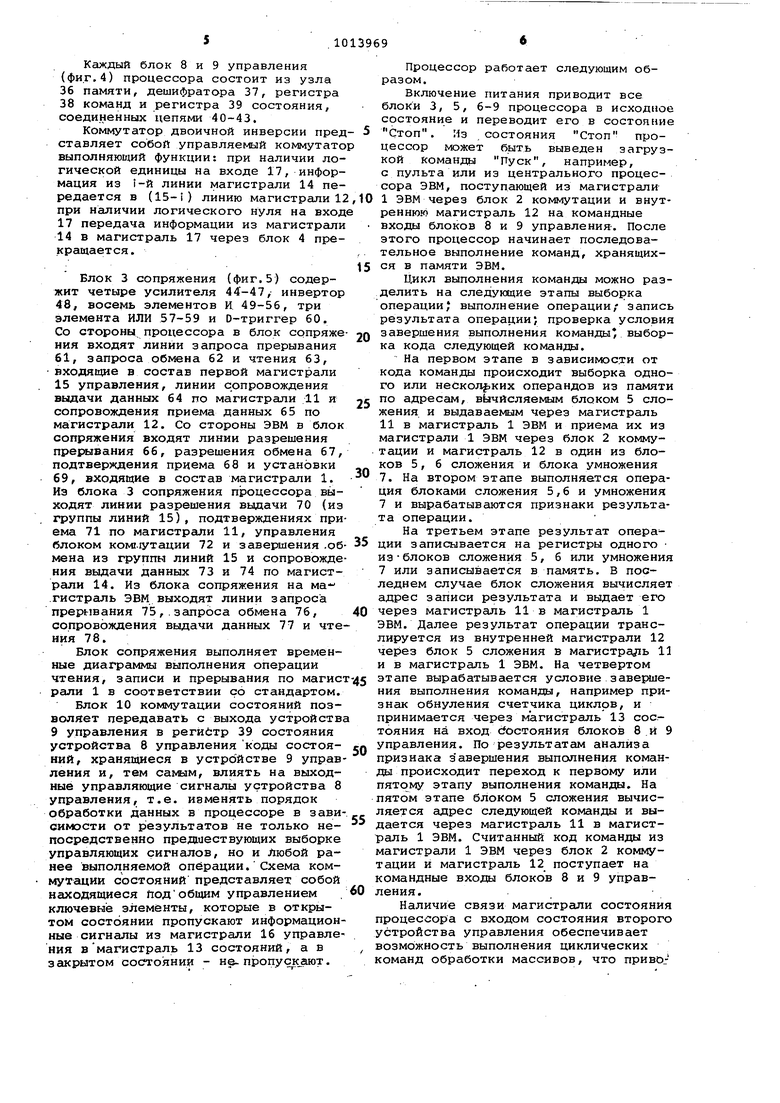

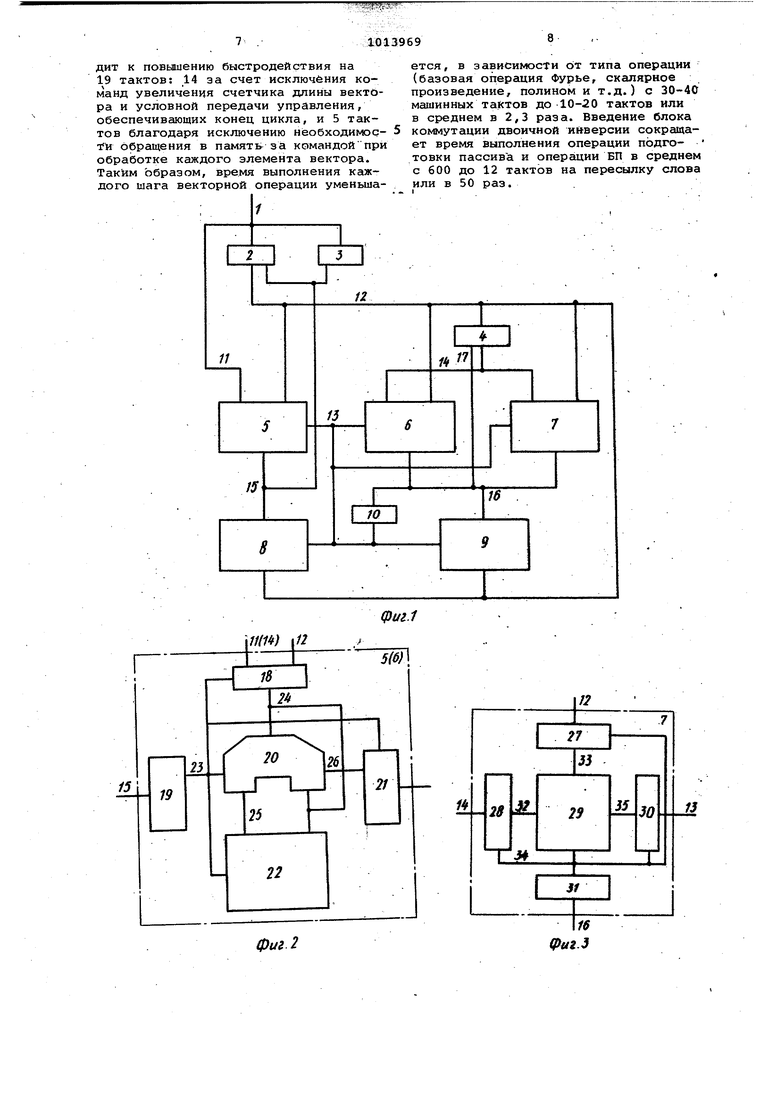

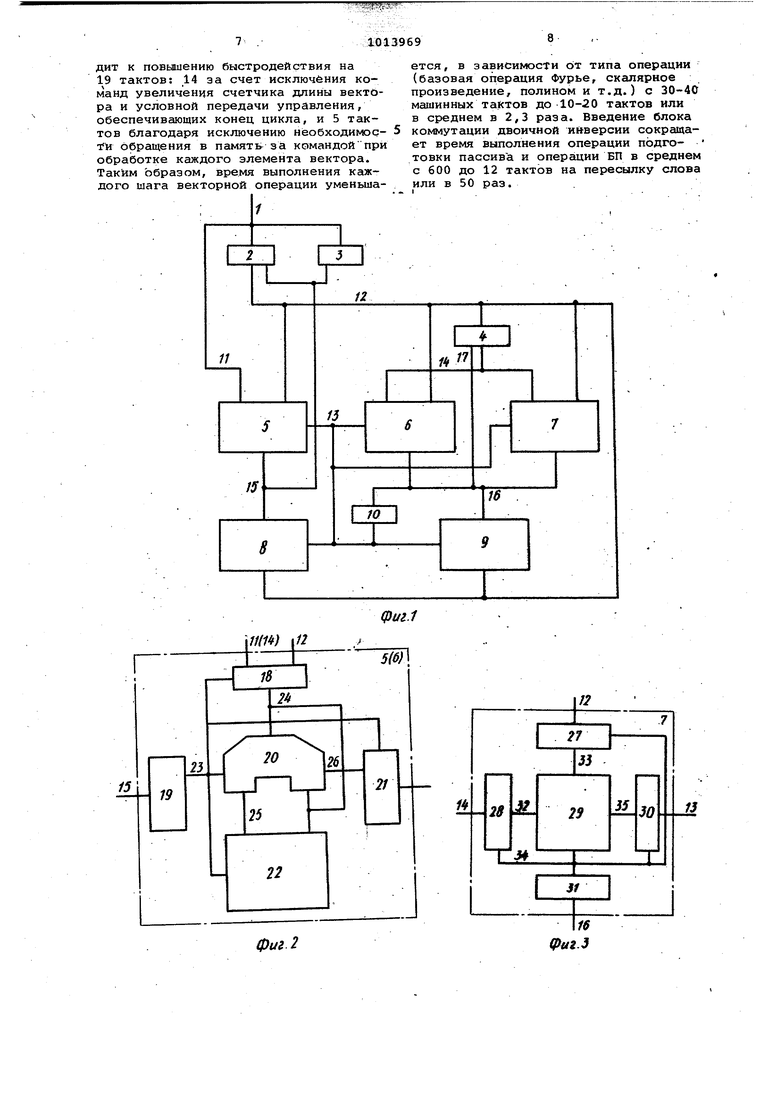

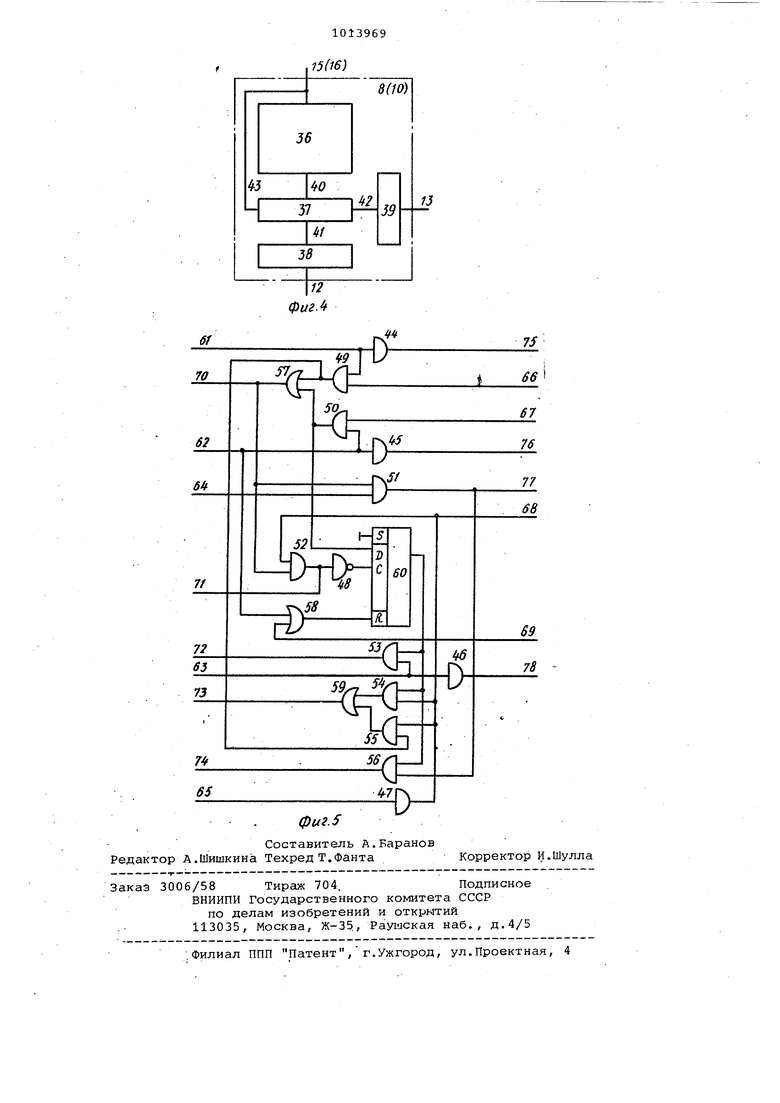

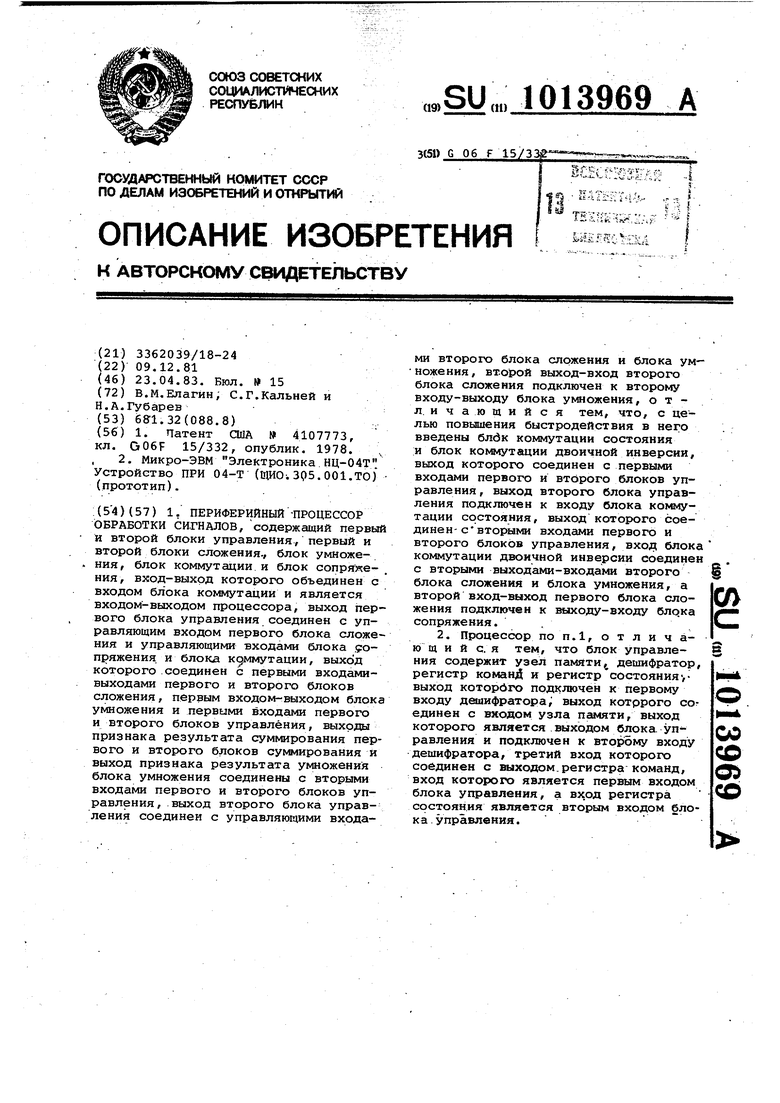

Изобретение относится к микроэлектронике и вычислительной технике и может быть использовано для постро ения вычислительных систем цифровой обработки сигналов в реальном времени. Известен специализированный периферийный процессор для обработки мас сивов информации, содержащий арифметическое устройство, выполняющее арифметические действия над числами представленными в форме с фиксирован ной или плавающей запятой, внутренню память, состоящую из двух независимы блоков, одновременно осуществляющих обмены с Пс1мятью. центрального процес сора и арифметическим устройством, три устройства управления на основе ПЗУ, управляющие работой ,ариф метического устройства и обмена информацией между памятью периферийного процессора и памятью центрального процессора. Трубопроводный принцип организации структуры процессора позволяет достичь высоких показателей быстродействия за счет перекрытия и распараллеливания обработки информации. Распределение функций обработки данных между центральным и периферийным процессорами позволяет строить оптимальным образом специальные алгоритмы спектрального анализа. Существует возможность улу паения характеристик систем путем подключения к одному центральному процессору нескольких периферийных ClJ- . Однако специализированный периферийный процессор приводит к большим аппаратурным затратам, что исключает возможность его использования в вычислительных системах с жестким ограничением на объем оборудования. Наиболее близким к изобретению по технической сущности является процессор, лриманяемый в ЭВМ, с асинхронным, унифицированным интерфейсом подключаемый к магистрали ЭВМ и состоящий из регистров блока коммутации и блока сопряжения, двух блоков сложения, блока умножения, двух устройств управления, связанных между собой внутренними информационными ма гистралями процессора и магистралями управления,, причем соединение первы входов-выходов блоков сложения, блока умножения, командных входов перво го и второго устройств управления, влода состояния второго устройства управления и выхода блока.коммутации образует первую внутреннюю магистраль процессора; используемую для приема данных и команд из памяти- и проведения обменов информацией между блоками сложения и умножения. Соединение вторых входов-выходов блоков сложения, блока y iнoжeния и входа блока коммутации образует вторую внутреннюю магистраль процессора, используемую для проведения обменов информадией между блоками сложения и умножения и для выдачи адресов и данных из блоков сложения и умножения на вход блока коммутации и далее в магистраль ЭВМ. Coeди eниe выхода первого устройства управления с входами управления первого блока сложения, регистрации блоков коммутации и блоком сопряжения образует первую магистраль управления, используемую для передачи кодов управления. Соединение выхода второго устройства управления с входами управления второго блока сложения и блока умно-жения образует вторую магистраль управления, используемую для передачи кодов управления. Соединение выходов состояния обоих блоков сложения и блока умножения с входом состояния первого устройства управления образует магистраль состояния, в которую выдаются коды признаков результатов выполненных операций Распределение функций обработки данных между первым блоком сложения, с одной стороны, и блоками сложения и умножения, с другой, дает возможность уменьшить объем памяти устройства управления и увеличить быстродействие процессора аа счет совмещения выполнения арифметических действий в блоках сложения и умножения с вычислением адресов в блоке сложения. Дополнительным ресурсом повышения производительности является возможность подключения нескольких процессоров, работающих с общей памятью к одной магистрали ЭВМ Г2. Недостатком известного процессора является низкое быстродействие. Целью изобретения является повышение быстродействия процессора на задачах цифровой обработки сигналов. Указанная цель достигается тем, что в периферийный процессор обработки сигналов, содержащий первьтй и второй блоки управл ения, первый и второй блоки сложения, блок умножения, блок коммутации и блок сопряжения, входвыход которого объединен с входом блока коммутации и является входомвыходом процессора, выход первого блока управления соединен с управляющим входом первого блока сложения и управляющими входами блока сопряжения и блока коммутации, выход которого соединен с первыми вхсдаглк-выходами первого и второго блоков сложения, первым входом-выходом блока умножения и первыми входами первого и второго блоков управления, выходы признака результата суммирования первого и второго блоков суммирования и выход признака результата умножения блока умножения соединены с вторыми вуока,ми первого и второго блоков управления выход второго блока управления соединён с управляющими входами второго блока сложения и блока умножения,второй выход-вход второго блока сложения подключен к второму входу-выходу бло ка умножения, введены блок коммутации состояния и блок коммутации двоичной инверсии, выход которого соединен с первыми входами первого и второго блоков управления, выход второго блока управления подключен к входу блока коммутации состояния,, выход которого соединен с вторыми входами .первого и второго бло.ков управления, вход, блока коммутации двоичной инвер сии соединен с вторыми выходами-входами Второго блока сложения и блока умножения, а второй вход-выход перво го блока сложения подключен к выходу входу блока сопряжения. Причем блок управления содержит узел памяти, дешифратор, регистр команд и регистр состояний, выход кото рого -подключен к первому входу дешиф ратора, выход которого соединен с входом узла памяти, выход которого является выходом блока управления и подключен к BTopofiy входу дешифратора, третий вход которого соединен с выходом регистра команд, вход которого является первым входом блока уп равления, а вход регистра состояния является вторым входом блока управления. , На фиг.1представлена функциональ ная схема периферийного процессора; на фиг;2 - функциональная схема блок сложенияJ на фиг.З - функциональная схема блока умножения; на фиг.4 функциональная схема устройства управления/ на фиг.5 - функциональная схема блока сопряжения. Периферийный процессор обработки сигналов (фиг.1) подключен к магистрали 1 ЭВМ с асинхронным унифицированным интерфейсом. Процессор содержит блок 2 крм1мутации, блок 3 сопряжения , блок 4 коммутации двоичной инверсии, первый блок 5 сложения, второй блок 6 сложения, блок 7 умножения, первый блок.8 управления, вто рой блок 9 управления и блок 10 ком; 1утации состояния. Вход-выход 11 первого блока 5 сло жения соединен с магистралью 1 ЭВМ. Первая внутренняя магистраль 12 процессора соединяет первые входы-выхо.ды первого блока 5 сложения,второго бло ка 6 сложения и блока 7 умножения,кома дные входы блоков 8 и 9 управления, выходы блока 2 коммутации и блока 4 коммутации двоичной инверсии. Магист раль 13 состояния соединяет выходы с:: стояния блоков 5-7, блока 10 комму тации состояния и входы состояния блоков 8 и 9 управления. Вторая внут ренняя магистраль 14 процессора coejn диняет вторые входы-выходы второго блока 6 сложения и блока 7 умножения с входом блока 4 коммутации двоичной инверсии. Первая магистраль 15 управления соединяет выход первого блока 8 управления с управляющими входами первого блока 5 сложения, блока 2 коммутации и блока 3 сопряжения. Вторая магистраль 16 управления соединя-. ет выход второго блока 9 управления с управляющими входами второго блока 6 сложения, блока 7 умножения, блока 10 коммутации состояния и с управляющим входом 17 блока 4 коммутации двоичной инверсии. Регистр блока 2 коммутации предназначен для буферизации принимаемых из магистрали 1 команд и данных и трансляций их в первую внутреннюю магистраль 12 процессора. Каждый блок 5 и 6 сложения процессора (фиг.2) включает узел коммутатора 18, дешифратор 19, сумматор- 20, регистр 21 состояния и регистры 22 общего назначения, соединенные между собой цепями 23-26. Коммутатор 18 соединяет выходную цепь 24 блока сложения с первым 11 (14) и вторым 12 входами-выходами данных блоков 5 и 6 сложения. Дешифратор 19 преобразует поступающие по входу 15 управления коды в сигн.алы управления и выдает их по цепи 23 на все схемы блока сложения. Сумматор 20 выполняет набор арифметических и логических операций над данными, по-; ступающими на него по входам 24 и 25. На регистре 21 состояния хранятся признаки результата сумматора, записываемые в него по цепи 26 и выдаваемые из блока сложения по цепи 13. Регистры 22 общего назначения предназ- начены для временного хранения информации внутри блока сложения. Блок 7 умножения (фиг.З) состоит из двух регистров 27 и 28, умножителя 29, регистра 30 состояния и дешифратора 31 кодов управления. В регистрах 27 и 28 запоминаются операции, поступающие по первому и второму входам-выходам 12, 14 данных . на блок умножения. После выполнения операции умножения умножителем 29 над содержимым регистров 27 и 28, поступающим на умножитель по цепям 32 и 33, результат умножения записывается в регистры 27 и 28. Дешифратор 31 кодой управления блока умножения преобразует поступающие на вход 16 управления коды в управляющие сигнашы для всех схем блока умножения, выдаваемых им по цепи 34. Признаки состояния результата выполнения операции умножения записыва:ются в регистр 30 состояния блока умножения по цепи 35. Каждый блок 8 и 9 управления (фиг,4) процессора состоит из узла 36 памяти, дешифратора 37, регистра 38 команд и регистра 39 состояния, соединенных цепями 40-43. Коммутатор двоичной инверсии пред ставляет собой управляемый коммутато выполняющий функции: при наличии логической единицы на входе 17, информация из i-й линии магистрали 14 передается в (15-i) линию магистрали 12 при наличии логического нуля на вход 17 передача информации из магистрали 14в магистраль 17 через блок 4 прекращается. Блок 3 сопряжения (фиг.5) содержит четыре усилителя 44-47, инвертор 48, восемь элементов И 49-56, три элемента ИЛИ 57-59 и D-триггер 60, Со стороны процессора в блок сопряже ния входят линии запроса прерывания 61, запроса обмена 62 и чтения 63, входящие в состав первой магистрали 15управления, линии сопровождения выдачи данных 64 по магистрали 11 и сопровождения приема данных 65 по магистрали 12. Со стороны ЭВМ в блок сопряжения входят линии разрешения прерывания 66, разрешения обмена 67, подтверждения приема 68 и установки 69, входящие в состав магистрали 1. Из блока 3 сопряжения процессора выходят линии разрешения выдачи 70 (из группы линий 15), подтверждениях при ема 71 по магистрали 11, управления блоком ком1.1утации 72 и завершения .об мена из группы линий 15 и сопровожде ния выдачи данных 73 и 74 по магистрали 14. Из блока сопряжения на ма.гистраль ЭВМ выходят линии запроса прерывания 75,.запроса обмена 76, сопровождения выдачи данных 77 и чте ния 78. Блок сопряжения выполняет временные диаграммы выполнения операции чтения, записи и прерывания по магист рали 1 в соответствии со стандартом. Блок 10 коммутации состояний позволяет передавать с выхода устройства 9 управления в регистр 39 состояния устройства 8 управления коды состояНИИ, хранящиеся в устройстве 9 управ ления и, тем самым, влиять на выходные управляющие сигналы устройства 8 управления, т.е. изменять порядок обработки данных в процессоре в зависимости от результатов не только непосредственно предьиествующих выборке управляющих сигналов, но и Любой ранее выполняемой операции. Схема коммутации состояний представляет собой находящиеся йодобщим управлением . ключевые элементы, которые в открытом состоянии пропускают информационные сигналы из магистрали 16 управления вмагистраль 13 состояний, а в закрытом сос тоянии - не-пропускают. Процессор работает следующим образом. Включение питания приводит все блоки 3, 5, 6-9 процессора в исходное состояние и переводит его в состояние Стоп. Из состояния Стоп процессор может быть выведен загрузкой команды Пуск, например, с пульта или из центрального процессора ЭВМ, поступающей из магистрали IЭВМ через блок 2 коммутации и внутреннюю магистраль 12 на командные входы блоков 8 и 9 управления. После этого процессор начинает последовательное выполнение команд, хранящихся в памяти ЭВМ. Цикл выполнения команды можно разделить на следующие этапы выборка операции выполнение операции/ запись результата операции; проверка условия завершения выполнения команды выборка кода следующей команды. На первом этапе в зависимости от кода команды происходит выборка одного или нескол| ких операндов из памяти по адресам, вычисляемым блоком 5 сложения и выдаваемым через магистраль IIв магистраль 1 ЭВМ и приема их из магистрали 1 ЭВМ через блок 2 коммутации и магистраль 12 в один из блоков 5, 6 сложения и блока умножения 7. На втором этапе выполняется операция блоками сложения 5,6 и умножения 7 и вырабатываются признаки результата операции. На третьем этапе результат операции записывается на регистры одного изблоков сложения 5, 6 или умножения 7 или записывается в память. В последнем случае блок сложения вычисляет адрес записи результата и выдает его через магистраль 11 в магистраль 1 ЭВМ. Далее результат операции транслируется из внутренней магистрали 12 через блок 5 сложения в магистра 1ь 11 и в магистраль 1 ЭВМ. На четвертом этапе вырабатывается условие завершения выполнения команды, например признак обнуления счетчика циклов, и принимается через магистраль 13 состояния на вход Состояния блоков 8,й 9 управления. По результатам анализа признака завершения выполнения команды происходит переход к первому или пятому этапу выполнения команды. На пятом этапе блоком 5 сложения вычисляется адрес следующей команды и выдается через магистраль 11 в магистраль 1 ЭВМ. Считанный код команды из магистрали 1 ЭВМ через блок 2 коммутации и магистраль 12 поступает на командные входы блоков 8 и 9 управления. Наличие связи магистрали состояния процессора с входом состояния второго устройства управления обеспечивает возможность выполнения циклических команд обработки массивов, что приво дит к повышению быстродействия на 19 тактов: 14 за счет исключения команд увеличения счетчика длины вектора и условной передачи управления, обеспечивающих конец цикла, и 5 тактов благодаря исключению необходимоеfK обращения в память- за командой при обработке каждого элемента вектора. Таким образом, время выполнения каждого шага векторной операции уменьша iim) 12 ется, в зависимости от типа операции (базовая операция Фурье, скалярное произведение, полином и т.д.) с 30-40 машинных тактов до 10-20 тактов или в среднем в 2,3 раза. Введение блока коммутации двоичной инверсии сокращает время выполнения операции подготовки пассива и операции БП в среднем с 600 до 12 тактов на пересылку слова или в 50 раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микроэлектронная вычислительная машина | 1979 |

|

SU1061606A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1988 |

|

SU1541623A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

1. ПЕРИФЕРИЙНЫЙ -ПРОЦЕССОР ОБРАБОТКИ СИГНАЛОВ, содержащий первый и второй блоки управления, первый и второй блоки сложения., блок умножения, блок коммутации.и блок сопряже- . ния, вход-выход которого объединен с входом блока коммутации и является входом-выходом процессора, выход первого блока управления соединен с управляющим входом первого блока сложения и управляющими входами блока .90пряжения. и блока коммутации, выход которого соединен с первыми входамивыходами первого и второго блоков сложения, первым входом-выходом блока умножения и первыми входами первого и второго блоков управления, выходы признака результата сумьирования первого и второго блоков суммирования и выход признака результата умножени я блока умножения соединены с вторыми входами первого и второго блоков управления, выход второго блока управ-ления соединен с управляюгдими входами второго блока сложения и блока ум- ножения, второй выход-вход второго блока сложения подключен к второму входу-выходу блока умножения, отличающийся тем, что, с целью повышения быстродействия в него введены коммутации состояния и блок коммутации двоичной инверсии, выход которого соединен с первыми входами первого и второго блоков управления , выход второго блока управления подключен к входу блока коммутации состояния, выход которого соединен- с BTOjttiMH входами первого и второго блоков управления, блока коммутации двоичной инверсии соединен с вторыми выходами-входами второго блока сложения и блока умножения, а сл второй вход-выход первого блока сложения подклю чен к выходу-входу блрка сопряжения. . 2. Процессор ПОП.1, о т л и ч аю щ и и с. я тем, что блок управления содержит узел памяти дешифратор, регистр команд и регистр состояния выход которбго подключен к первому входу дешифратора; выход котррого сог единен с входом узла памяти, выход 00 которого является выходом блока управления и подключен к второму входу Ш дешифратора, третий вход которогчэ Ф со соединен с выходом.регистра команд, вход которого является первым входом блока управления, а вход регистра состояния является вторым входом блока управления.

фиг 2

/

13

I «

Мб фаг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент ОНА 4107773, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ; | |||

Авторы

Даты

1983-04-23—Публикация

1981-12-09—Подача