() МИКРОПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1985 |

|

SU1330634A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство адресации памяти | 1986 |

|

SU1410039A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

I

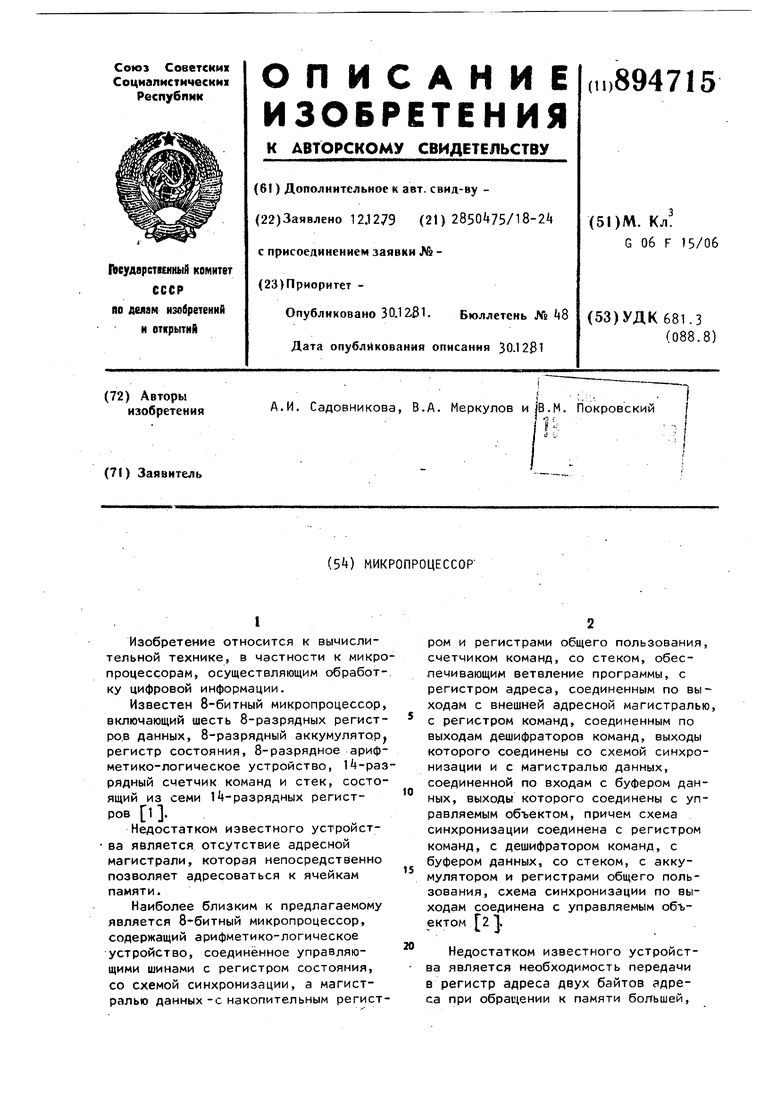

Изобретение относится к вычислительной технике, в частности к микропроцессорам, осуществляющим обработ-. ку цифровой информации.

Известен 8-битный микропроцессор, включающий шесть 8-разрядных регистров данных, 8-разрядный аккумулятор регистр состояния, 8-разрядное арифметико-логическое устройство, 14-разрядный счетчик команд и стек, состоящий из семи 1«-разрядных регистров 1 .

Недостатком известного устройства является отсутствие адресной магистрали, которая непосредственно позволяет адресоваться к ячейкам памяти.

Наиболее близким к предлагаемому является 8-битный микропроцессор, содержащий арифметико-логическое устройство, соединённое управляющими шинами с регистром состояния, со схемой синхронизации, а магистралью данных -с накопительным регистром и регистрами общего пользования, сметчиком команд, со стеком, обеслечивающим ветвление программы, с регистром адреса, соединенным по выходам с внешней адресной магистралью, с регистром команд, соединенным по выходам дешифраторов команд, выходы которого соединены со схемой синхронизации и с магистралью данных, соединенной по входам с буфером дан10ных, выходы которого соединены с управляемым объектом, причем схема синхронизации соединена с регистром команд, с дешифратором команд, с буфером данных, со стеком, с акку15мулятором и регистрами общего пользования, схема синхронизации по выходам соединена с управляемым объектом 21.

20

Недостатком известного устройства является необходимость передачи в регистр адреса двух байтов адреса при обращении к памяти большей.

3

чем 256 ячеек, что существенно снижает скорость выполнения команд.

Цель изобретения - повышение быстродействия за счет возможности адресации к памяти объемом до 64к байт с помощью одного байта адреса.

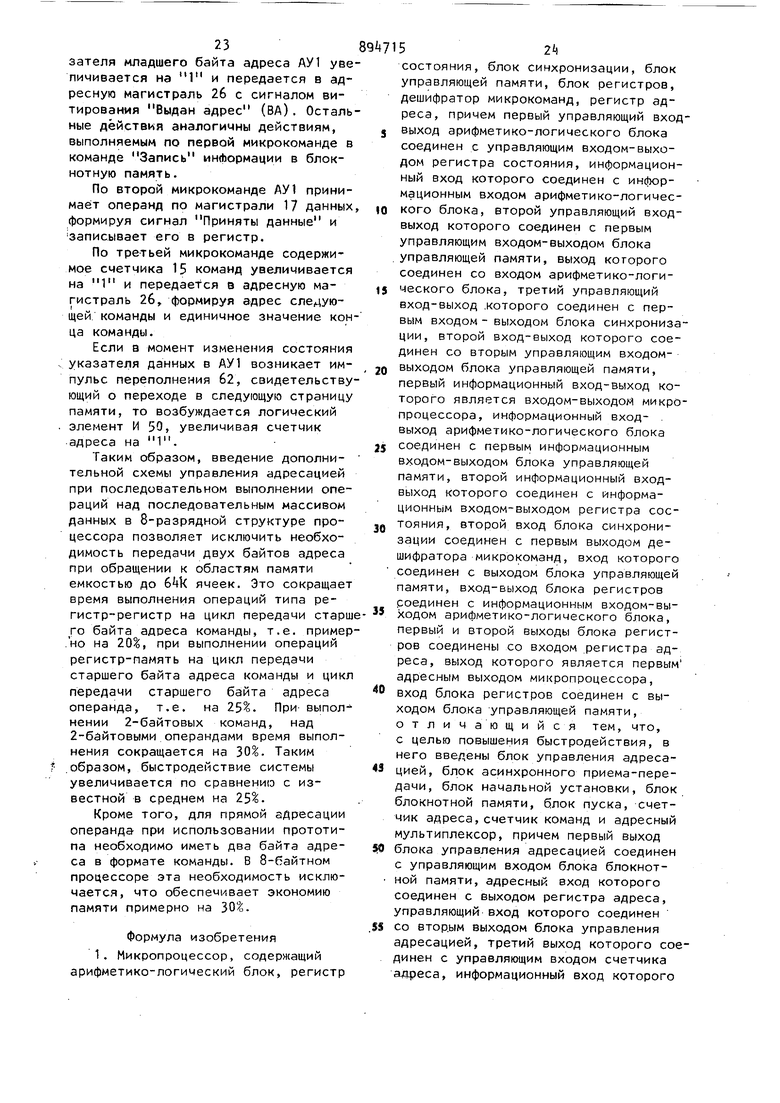

Поставленная цель достигается тем,что в микропроцессор, содержащий арифметико-логический блок, регистр состояния, блок синхронизации блок 5правляющей памяти, блок регистров , дешифратор,микрокоманд,регист адреса, причем первый управляющий вход-выход арифметико-логического блока соединен с управляющим входом.выходом регистра состояния, информационный вход которого соединен с информационным входом арифметикологического блока, второй управляющий вход-выход которого соединен с первым управляющим входом-выходом блока управляющей памяти, выход которого соединен со входом арифметиклогического блока, третий управляю. щий вход-выход которого -соединен с первым входом-выходом блока синхронизации, второй вход-выход которого соединен со вторым управляющим входом-выходом блока jуправляющей памяти, первый информационный вход-выход которого является входом-выходом микропроцессора, информационный вход-выход apифмeтикo-лo ичecкoгo блока соединен с первым информационным входомвыходом блока управляющей памяти, второй информационный вход-выход которого соединен с информационным входом-выходом регистра состояния, второй вход блока синхронизации соединен с первым выходом дешифрато ра микрокоманд, вход которого соединен с выходом блока управляющей памяти, вход-выход блока регистров соединен с информационным входом- выходом арифметико-логического блока, первый и второй выходы блока регистров соединены со входом регистра адреса, выход которого является первым адресным выходом микропроцессора, вход блока регистров соединен с выходом блока управляющейпамяти, введены блок управления адресацией, блок асинхронного приема-передачи, блок начальной устаноки, блок блокнотной памяти, блок . пуска, счетчик адреса, счетчик команд и адресный мультиплексор, причем первый выход блока управления

54

адресацией соединен с управляющим входом блока блокнотной памяти, адресный вход которого соединен с выходом регистра адреса, управляющий вход которого соединен со вторым выходом блока управления адресацией, третий выход которого соединен с управляющим входом счетчика адреса, информационный вход которого соединен со вторым выходом блока регистров, четвертый выход блока управления адресацией является управляющим выходом микропроцессора, а пятый выход блока управления адресацией соединен с первым входом-выходом блока синхронизации, третий вход-выход которого соединен с входом-выходом блока асинхронного приема-передачи, выход которого соединен с пятым выходом блока управления адресацией, первый вход которого соединен с выходом блока синхронизации,

первый вход которого соединен с,первым выходом блока пуска, второй выход которого соединен со входом блока начальной установки, выход которого соединен с установочными входами блока управляющей памяти, арифметико-логического блока, блока синхронизации и блока управления адресацией, второй вход которого соединен с выходом дешифратора микрокоманд, вход-выход блока блокнотной памяти соединен со входом-выходом блока регистров, выход счетчика адреса соединен с первым входом адресного мультиплексора, выход которого является вторым адресным выходом микропроцессора, информационный вход счетчика адреса соединен со вторым выходом блока регистров, управляющий вход счетчика команд соединен с третьим выходом блока управления адресацией, выход счетчика команд соединен со входом адресного мультиплексора .

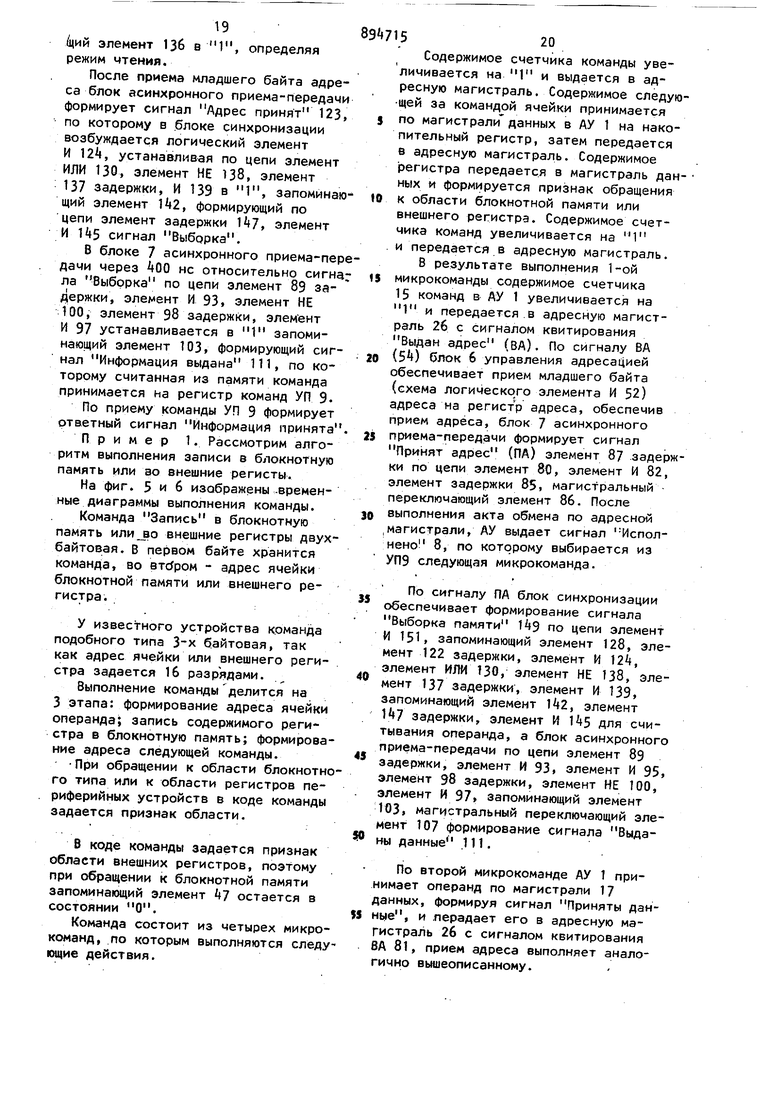

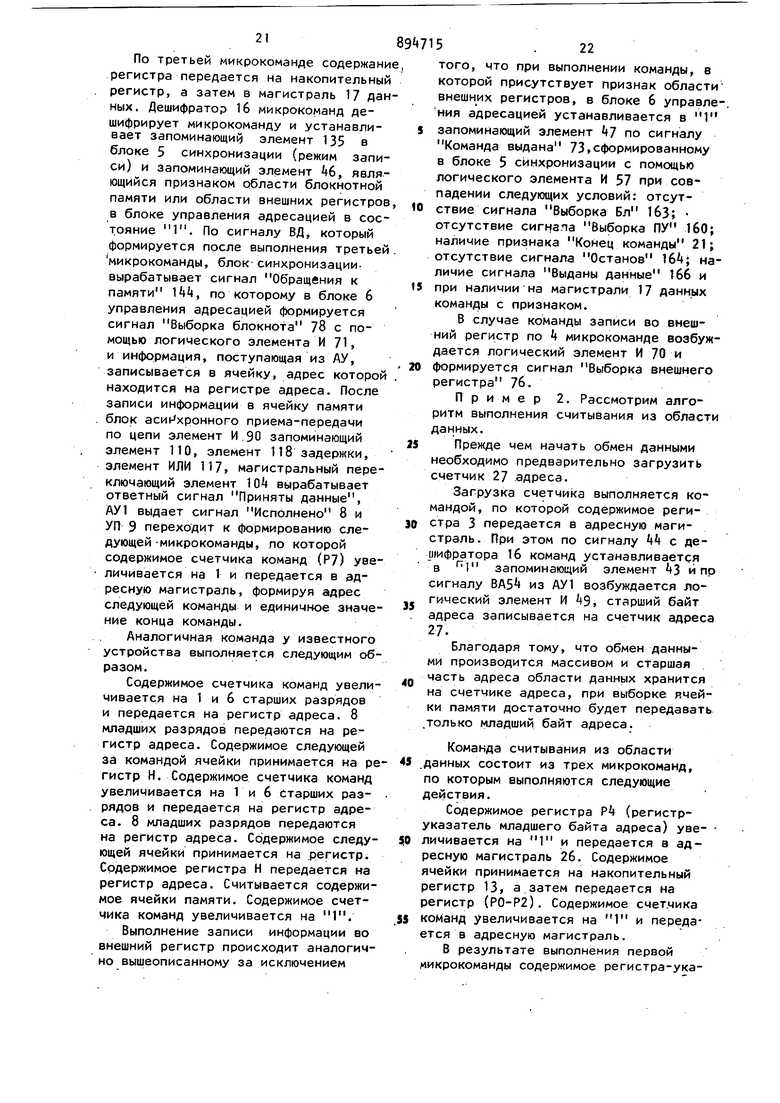

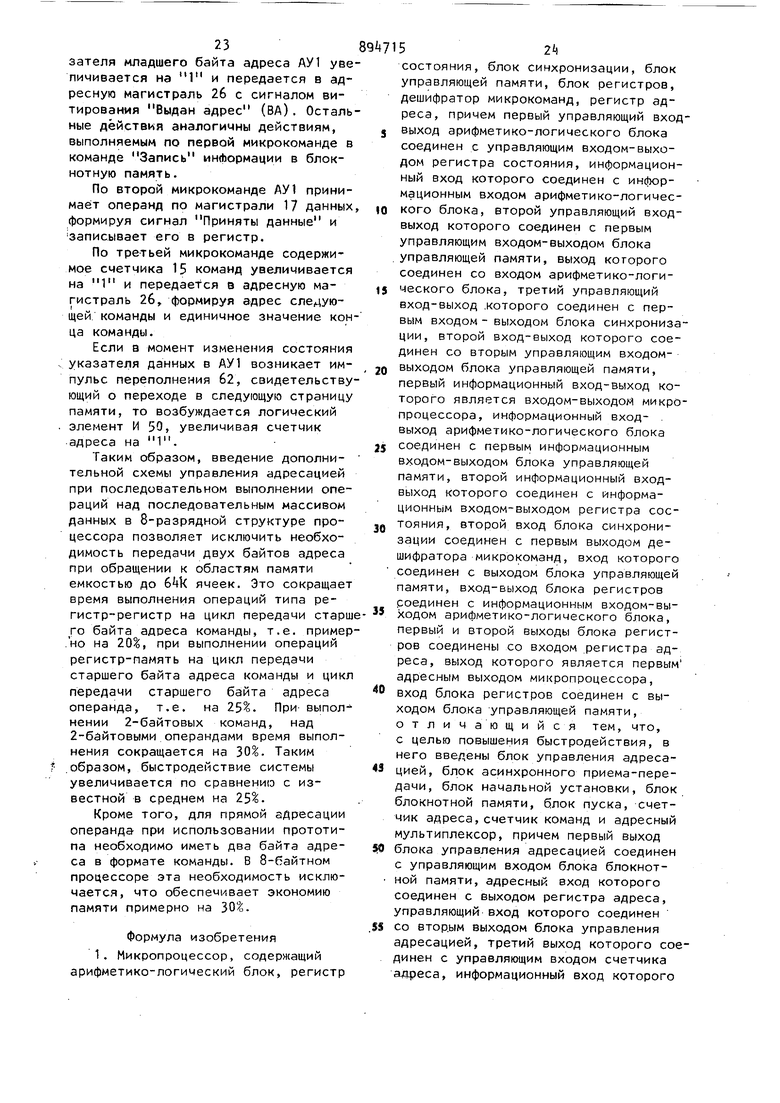

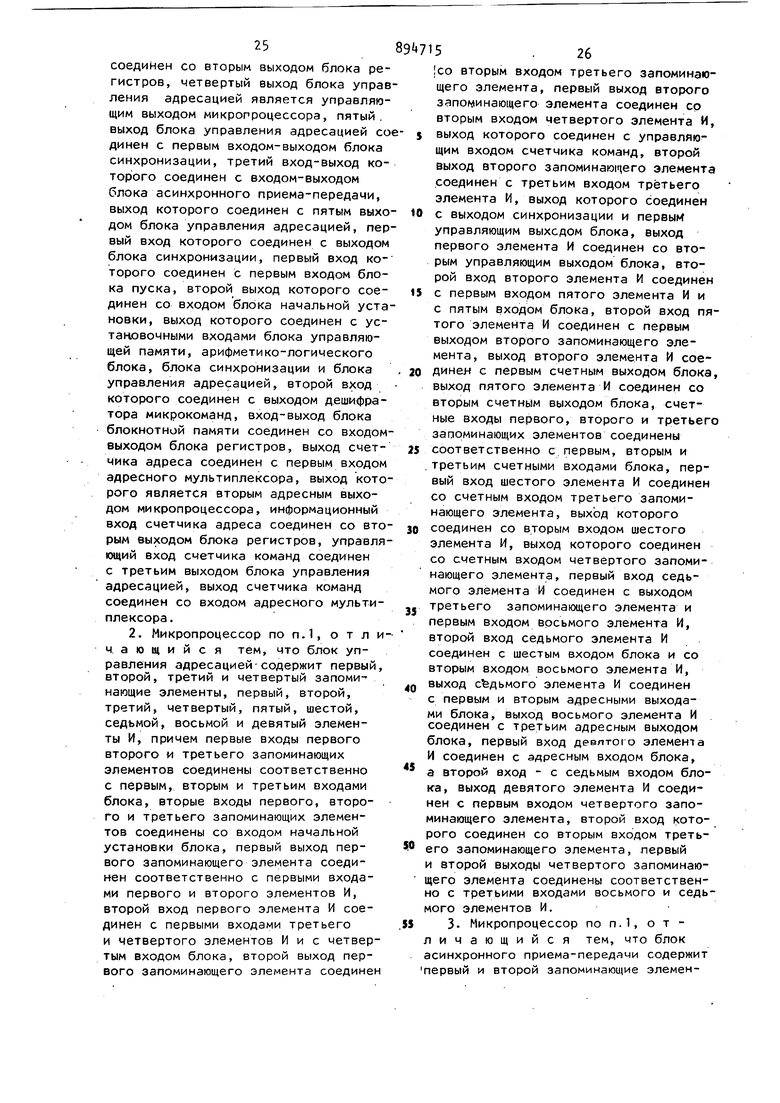

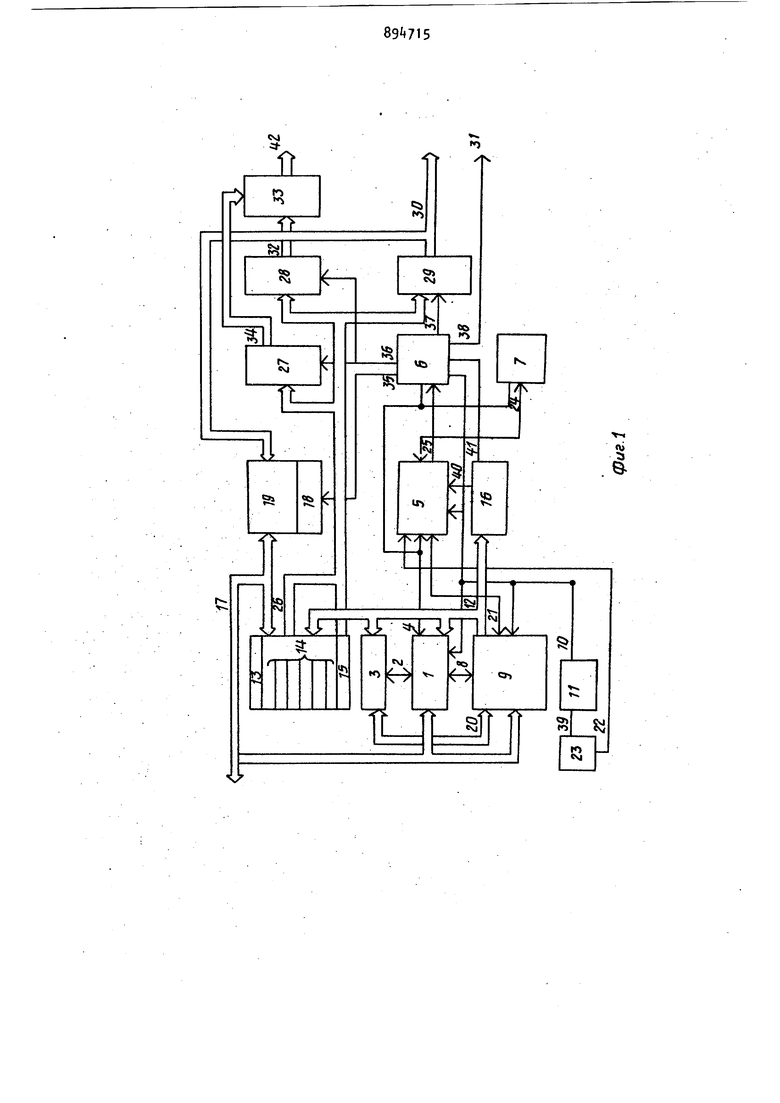

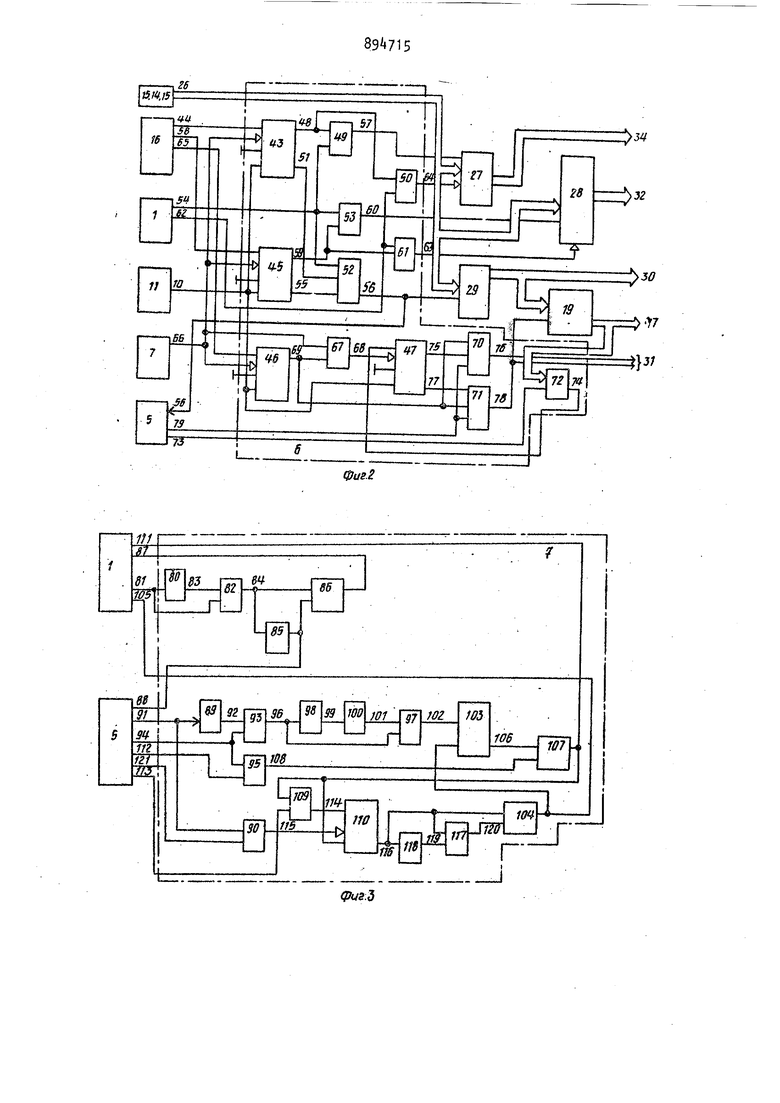

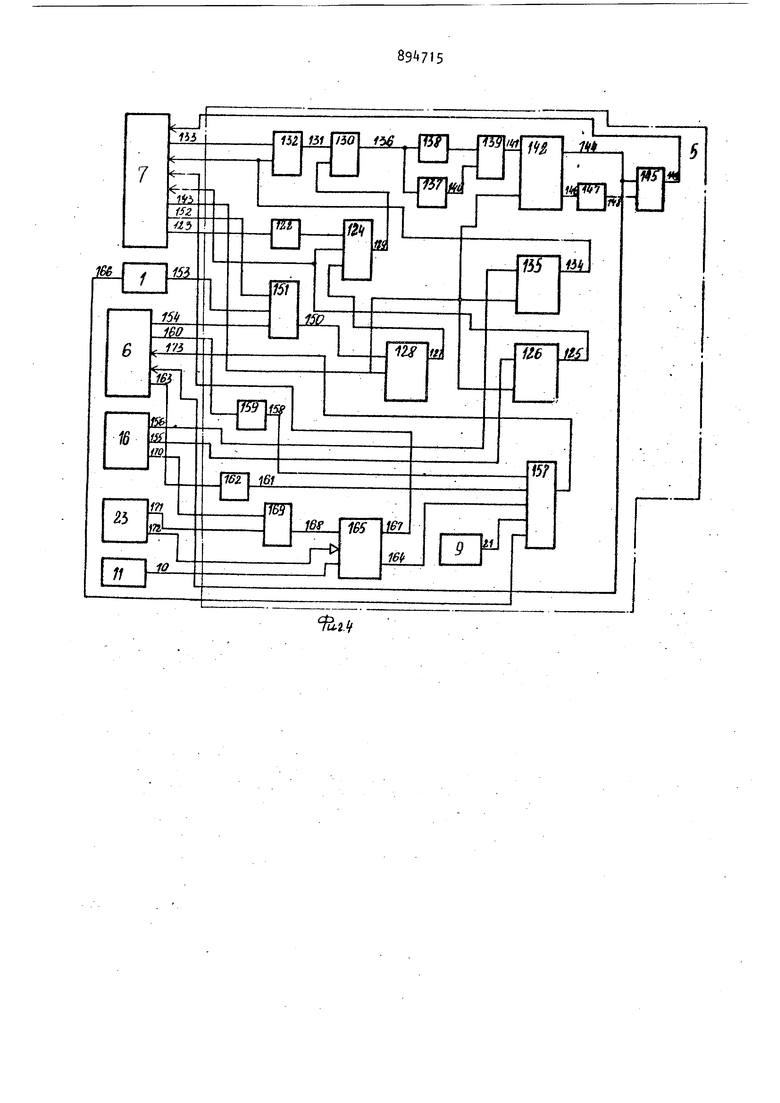

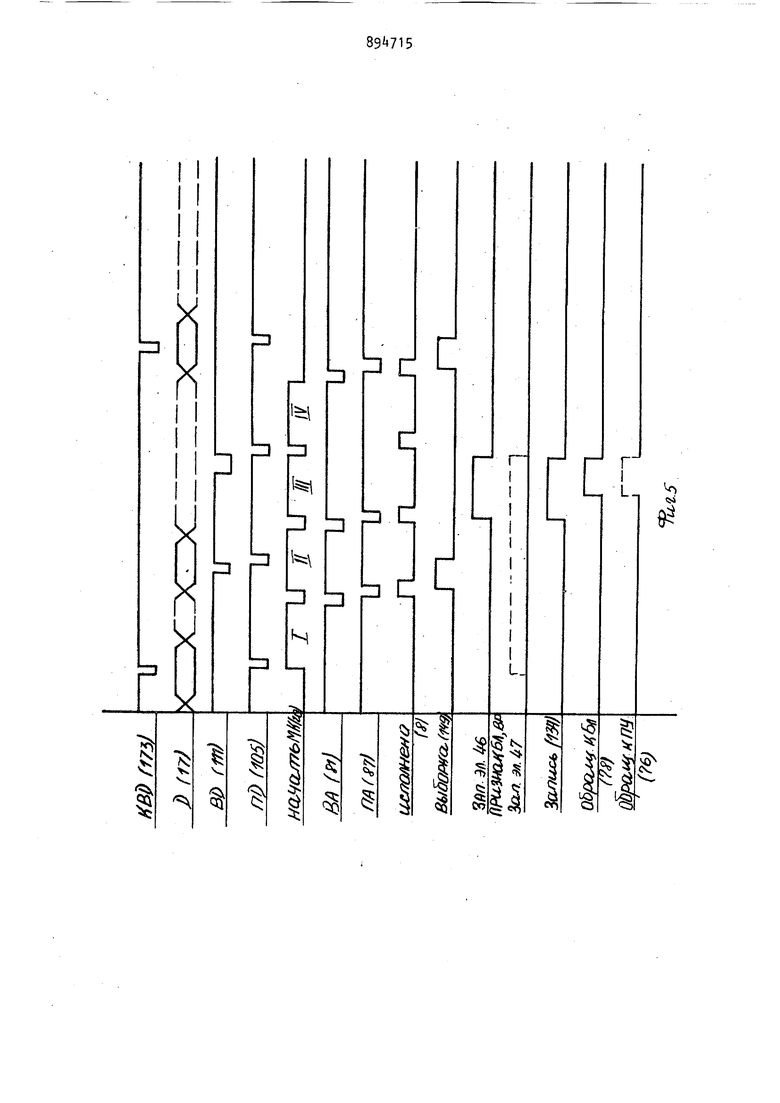

При этом блок управления адреса- . цией содержит первый, второй, третий и четвертый запоминающие элементы, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем первые входы первого, второго и третьего запоминающих элементов соединены соответственно с первым, вторым и третьим входами блока, вторые входы первого, второго и третьего запоминаю,дих элементов соединены со входом 5 (начальной установки блока, первый выход первого запоминающего элемент соединен соответственно с первыми в дами первого и второго элементов И, второй вход первого элемента И соединен с первыми входами третьего и четвертого элементов И и с четверты входом блока, второй выход первого поминающего элемента соединен со вторым входом третьего запоминающег элемента, первый выход второго запо минающего элемента соединен со вторым входом четвертого элемента И, выход которого соединен с управляющ входом счетчика команд, второй выхо второго запоминающего элемента соед нен с третьим входом третьего элеме та И, выход которого соединен с выходом синхронизации и первым управляющим выходом блока, выход первого элемента И соединен со вторым управляющим выходом блока, второй в второго элемента И соединен с первым входом пятого элемента И и с пятым входом блока, второй вход пятого элемента И соединен с первым выходом второго запоминающего элемента, выход второго элемента И соединен с первым счетным выходом блока, выход пятого элемента И соединен со вторым- счетным выходом блока, счетные входы первого, второго и третье запоминающих элементов соединены соответственно с первым, вторым и третьим счетными входами блока, пер вый вход шестого элемента И соединен со счетным входом третьего запоминающего элемента, выход которого соединен со вторым входом шестого элемента И, выход которого соединен со счетным входом четвертого запоминающего элемента, первый вход сед мого элемента И соединен с выходом третьего запоминающего элемента и первым входом восьмого элемента И, второй вход седьмого элемента И соединен с шестым входом блока и со вторым входом восьмого элемента И, выход седьмого элемента И соединен с первым и вторым адресными выходами блока, выход восьмого элемента И соединен с третьим адресным выходом блока, первый вход девятого элемента И соединен с адресным вхо дом блока, а второй вход - с седьмым входом блока, выход девятого элемента И соединен с первым входом четвертого запоминающего элемента, второй вход которого соединен со is вторым входом третьего запоминающего элемента, первый и второй выходы четвертого запоминающего элемента соединены соответственно с третьими входами восьмого и седьмого элементов И. Блок асинхронного приема-передачи содержит первый и второй запоминающие элементы, первый, второй, третий, четвертый, пятый и шестой элементы И, первый,, второй, третий, четвертый и пятый элементы задержки, первый, второй и третий магистральные переключающие элементы, элемент НЕ и элемент ИЛИ, причем вход первого элемента задержки соединен с первым входом блока, а выход - с первым входом первого элемента И, второй вход которого соединен со входом первого элемента задержки, выход первого элемента И соединен со входом второго элемента задержки и с первым входом первого магистрального переключающего элемента, второй вход которого соединен с выходом второго .элемента задержки и первым выходом блока,выход первого магистрального .переключающего элемента соединен со вто-. рым выходом блока, вход третьего элемента задержки соединен с первым входом второго элемента И и с входом выборки блока, а выход - с первым входом третьего элемента И, второй вход которого соединен со вторым входом блока и с первым входом четвертого элемента И, выход третьего элемента И соединен со входом четвертого элемента задержки, выход которого соединен со входом элемента НЕ, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом третьего элемента И, выход пятого элемента И соединен с первым входом первого запоминающего элемента, второй вход которого соединен с третьим выходом блока, второй вход четвертого элемента И соединен с третьим входом блока, первый вход шестого элемента И соединен со вторым выходом блока, вторые входы второго, четвертого и шестого элементов И соединены соответственно с четвертым, третьим и пятым входами блока, выход второго элемента И соединен со счетным входом второго запоминающего элемента, первый вход которого соединен с выходом шестого элемента И, второй вход второго запоминающего элемента соединен с первым входом шестого элемента И, а выход - с первым входом элемента ИЛИ и со входом пятого элемента задержки, выход которого соединен со вторым входом элемента ИЛИ, выход которого соедине с первым входом второго магистрального переключающего элемента, второй вход которого соединен с первым входом элемента ИЛИ, а выход - с третьим вьгходом блока и со вторым входом первого запоминающего элемента, выход которого соединен с первым вхо дом третьего магистрального переключающего элемента, второй вход кото.рого соединен с выходом четвертого элемента И, выход третьего магист рального переключающего элемента сое динен с первым входом шестого элемента И. На фиг. 1 представлена блок-схема микропроцессора; на фиг. 2 - блок управления адресацией для 8-битного микропроцессора; на фиг. 3 блок асинхронного приема-передачи для 8-битного микропроцессора; на фиг. k - блок синхронизации; на фиг. 5 и 6 - временные диаграммы выполнения команды. .Устройство содержит арифметикологический блок 1, соединенный управляющей шиной 2 с регистром 3 состояния, управляющей шиной 4с. блоком 5 синхронизации, блоком 6 управления адресацией и блоком 7 |асинхронного приема-передачи, управляющей шиной 8 и блоком 9 управляющей памяти, управляющей шиной 10 с блоком 11 начальной установки, с блоком 5 синхронизации, с блоком управляющей памяти, с блоком 6 управления адресацией, микрокомандной магистралью 12 с блоком 9 управляющей памяти, с регистром 3 состояния с накопительным регистром 13, с блоком 14 регистров (регистром обще го пользования) , со счетчиком 15 команд, с дешифратором 1б микрокоманд, а магистралью 17 данных - с накопительным регистром 13 и регистром 14 общего пользования, счетчиком 15 команд, со счетчиком 18 с блоком 19 блокнотной памяти, с блоком 9 управляющей памяти, регист 3 состояния, соединенный магистраль 20 с блоком 9 управляющей памяти, блок 5 синхронизации, соединенный по входу 21 с блоком 9 управляющей памяти, по входу 22 - с блоком 23 58 пучка, по входу 24 - с блоком 7 асинхронного приема-передачи, по выходу 25 - с блоком 6 управления адресацией,накопительный регистр 13 и регистры 14 общего пользования, счетчик 15 команд, связанные внутренней адресной магистралью 26 со счетчиком 27 адреса, со счетчиком 28 команд и регистром 29 адреса, регистр 29 адреса, соединенный по выходу 30 с управляемым объектом 31 и блоком 19 блокнотной пямяти, счетчик 29 команд, соединенный по выходу 32 с адресным мультиплексором 33, счетчик 27 адреса, соединенный по выходу 34 с адресным мультиплексором 33, блок 6 управления адресацией, соединенный по выходу 35 с блоком 19 блокнотной памяти, по выходу 36 - со счетчиками адреса 27 и команд 28, по выходу 37 - с регистром 29 адреса, по выходу ЗВ - с управляемым объектом 31, блок 19 блокнотной памяти, блок 9 управляющей памяти, блок 11 . начальной установки, соединенный по входу 39 с блоком 23 пуска, дешифратор 16 микрокоманд, соединенный по выходу 40 с блоком 5 синхронизации, по выходу 41 - с блоком 6 управления адресацией, адресный мультиплексор 33, соединенный по выходу 42 с управляемым объектом 31. : Блок 6 управления адресацией содержит четыре запоминающих элемента и девять элементов И, приЧем первый запоминающий элемент 43 по первому соединен с первым выходом 44 дешифратора 16 микрокоманд, по второму входу - со вторыми входами второго 45, .третьего 46 и четвертого 47 запоминающих элементов и с блоком 11 начальной установки, а по первому выходу 48 соединен с первыми входами первого 49 и второго 50элементов И, по второму выходу 51- со вторым входом третьего элемента И 52, соединенного по первому входу со BTopBiM входом первого элемента И 49, с первым входом четвертого 53 элемента И с первым выходом 54 арифметико-ло.гического блока 1, по третьему входу 55 - со вторым выходом второго запоминающего элемента 45, а по выходу 56 - со стробирующим входом регистра 29 адреса и первым входом блока 5 синхронизации, выход 57 первого элемента И 49 соединен со стробирующим входом счетчика 27 адреса, второй запоминающий элемент 45 по первому входу соединен со вторым выходом 58 дешифратора 16 микрокоманд, по первому выходу 59 со вторым входом четвертого элемента И. 53, выход 60 которого соединен со стробирующим входом счетчика 28 команд и вторым входом пятого элемента И 61 второй вход второго элемента И 50 соединен со вторым выходом 62 арифметико-логического блока 1 и с первым входом пятого элемента И 61, выход 63 которого соединен со счет- ным входом счетчика 28 команд, выход 64 второго элемента И 50 соединен со счетным входом счетчика 27 адреса, третий запоминающий элемент 46 по первому входу соединен с третьим выходом б5 дешифратора 16 микрокоманд, по счетному входу 66, с блоком 7 асинхронного приема-передачи, со счетными входами первого 43 и второ го 45 запоминающих элементов и с пер вым входим шестого элемента И б7, выход 68 которого соединен со счетны входом четвертого запоминающего элемента 47, а по выходу б9 со вторым входом шестого элемента И б7 и первыми входами восьмого 70 и седьмо го 71 элементов И, второй вход девятого эг1емента И 72 соединен со вторы выходом 73 блока 5 синхронизации, первый вход - с магистралью 17 данны а выход 74 - с первым входом четвертого запоминающего элемента 47, первый выход 75 которого соединен с третьим входом восьмого элемента И 70, выход 76 которого соединен с управляемым объектом 31, второй выход 77 четвертого запоминающего элемента 47 соединен с третьим входом седьмого элемента И 71, выход 78 которого соединен с блоком 19 блокнотной памяти и управляемым объектом 31, а второй вход 79 - со вторым вхо дом восьмого элемента И 70 и первым выходом блока 5 синхронизации. Блок асинхронного приема-передачи содержит два запоминающих элемента, шесть элементов И, пять элементов задержки три магистральных переключающих элемента, один элемент НЕ и один эле мент ИЛИ, причем первый элемент 80 задержки по входу соединен с первым выходом 81 арифметико-логического блока 1 и вторым входом первого элемента И 82, а по выходу 83 - с первы входом первого элемента И 82, выход :84 которого соединен с входом второ|го элемента 85 задержки и первым входом первого магистрального переключающего элемента 86, соединенного по выходу со вторым входом 87 арифметико-логического блока 1, а выход второго элемента 85 задержки соединен со вторым управляющим входом магистрального переключающего элемента и первым входом 88 блока 5 синхронйзации, третий элемент 89 задержки по входу соединен .с первым входом второго элемента И 90 и с первым выходом 91 блока 5 синхронизации, а по выходу 92 - с первым входом третьего элемента И 93, второй вход которого соединен со вторым выходом 94 блока 5 синхронизации и с первым входом четвертого элемента И 95, а выход 96 соединен со вторым входом пятого элемента И 97 и входом четвертого элемента 98 задержки, выход 99 которого соединен со входом элемента НЕ 100, соединенного по выходу 101 с первым входом пятого элемента И 97, выход 102 которого соединен с первым входом первого запоминающего элемента 103, соединенного по второму входу с выходом.второго магистрального переключающего элемента 104 и вторым выходом 105 арифметико-логического блока 1, причем выход 106 первого запоминающего элемента 103 соединен с первым входом третьего магистрального переключающего элемента 107, второй управляющий вход которого соединен с выходом 108 четвертого элемента И 95,а выход магистрального переключающего элемента 107спервым входом шестого элемента И 109, со вторым входом ВТОРОГО запоминающего элемента 110и первым входом 111 арифметико-логического блока 1, а втарые входы четвертого 95 и шестого 109 элементов И соединены с третьим 112 и пятым 113 выходами блока 5 синхронизации, выход 114 шестого элемента И 109 соединен с первым входом йторого запоминающего элемента 110, соединенного счетным входом с выходом 115 второго элемента И 90, выход 116 второго запоминающего элемента 110 соединен с первым входом второго, магистрального переключающего элемента 104, первым входом элемента ИЛИ 117 и с входом пятого элемента 118 задержки, выход 119 которого соеинен со вторым входом элемента ИЛИ 117, соединенного по выходу 120 со TODbiM управляющим входом второго |Магистрального переключающего элемента , второй вход второго элемента И 90 соединен с четвертым выходом 121 блока 5 синхронизации. Блок 5 синхронизации содержит пять запоминающих элементов, шесть элементов И, три элемента задержки, два элемента ИЛИ и три элемента НЕ, причем первый элемент 122 задержки включен между четвертым выходом 123 блока 7 асинхронного приема-передачи и первым входом первого элемента И 12, соединенного по второму входу с выходом 125 первого запоминаю,щего элемента 126 и четвертым ьходом блока 7 ac.нxpoннoгo приема-передани по .третьему входу - с выходом 127 второго запоминающего элемента 128, по выходу 129 - со вторым входом пер вого элемента ИЛИ 13Q соединенного по первому входу с выходом 131 второ го элемента И 132, первый вход которого соединен с первым выходом 133 блока 7 асинхронного приема-передачи, а второй вход элемента И 132 с выходом 13 третьего запоминающего элемента 135 и вторым входом блока 7 асинхронного приема-передачи, выход 13 первого элемента ИЛИ 130 соедине с входами второго элемента 137 задержки и первого элемента НЕ 138, соединенного с первым входом третьего элемента И139 выход второго элемента 137 задержки соединен со вторым входом третьего элемента И 139, выход Hi которого соединен с первым входом четвертого запоминаю щего элемента , соединенного по второму входу с вторым выходом блока 7 асинхронного приема - передачи, со вторыми входами первого 126, второго 128 и третьего 135 запо минающих элементов,по первому выходу }kk -с первым входом четвертого элемент И 145 и со вторым входом блока 6 управления адресацией, по второму выходу - с входом третьего элемента задержки, выход 148 которого соединен со вторым входом четвертого элемента И , соединенного по выходу 149 с первым входом блока, 7 аЬинхронного приема-передачи, причем второй запоминающий элемент 128 по первому входу соединен с выходом 150 пятого элемента И 151 соединенного по первому входу с третьим выхо дом 152 блока 7 асинхронного приемапередачи, по второму входу - с пер512вым выходом 153 арифметико-логического блока 1, по третьему входу - с первым выходом 154 блока 6 управления адресацией, причем первый 126 и третий 135 запоминающие элементы по первым входам соединены со вторым 155 и первым 15б выходами дешифратора 16 микрокоманд, первый вход шестого элемента И 157 соединен с выходом 158 второго элемента НЕ 159, вход которого соединен со вторым выходом 1бО блока 6 управления адресацией, второй вход - с выходом 161 третьего элемента НЕ 1б2, вход которого соединен с третьим выходом 163 блока 6 управления адресацией, третий вход - со вторым выходом 164 пятого запоминающего элемента 1б5, четвертый выход 21 - с блоком 9 управляющей памяти, пятый вход - со вторым выходом 166 арифметико-логического блока 1, причем пятый запоминающий элемент 1б5 по первому выходу 1б7 соединен с третьим входом блока 7 асинхронного приема-передачи, по первому входу - с выходом 168 второго элемента ИЛИ 16$, первый вход которого соединен с третьим выходом 170 дешифратора 16 микрокоманд, второй вход - с первым выходом 171 блока 23 пуска, по счетному входу пятый запоминающий элемент 1б5 соединен со вторым Выходом 172 блока 23 пуска, по второму входу 10 - с блоком 11 начальной установки, причем выход 173 шестого элемента И 157 соединен с первым входом блока 6 управления адресацией. Арифметико-логический блок 1 (АБ) предназначен для выполнения арифметических, логических и сдвиговых операций. Блок состоит из двух комбинационных схем параллельного четырехразрядного арифметическо-логического узла с асинхронным переносом. При выполнении арифметических, логических, сдвиговых операций формируются .четыре признака, определяющие состоя.ние арифметико-логического блока в данный момент, которые хранятся на реги(;тре состояния. Регистр состояния включает в себя триггер расширения (Р), триггер знака (З), триггер переполнения (П), триггер нуля (Н). Блок 5 синхронизации организует цикл .выполнения команд. 13 Блок 6 управления адерсацией формирует 16-разрядный адрес по коротко му 8-разрядному адресу. Блок 7 асинхронного приема-переда чи формирует сигналы, обеспечивающие асинхронный обмен информацией по магистрали. Блок 9 управляющей памяти (УП) предназначен для хранения и выдачи микрокоманд, обеспечивающих управление различными блоками процессора. Блок 11 начальной установки форми рует сигналы, обеспечивающие приведе ние в исходное состояние БИС и всех триггеров процессора. Накопительный регистр 13 предназначен для промежуточного хранения операндов. Регистры 14 общего пользования обеспечивают возможность написания эффективных программ. Счетчик 15 команд предназначен для автоматического выполнения послeдoвaтeJ.1ьнocти команд. Дешифратор 16 микрокоманд обеспечивает формирование управляющих сигналов. Счетчик 18 предназначен для организации программного стека. Блок 19 блокнотной памяти (БП) хранит промежуточные результаты и пе ременнью параметры процесса. Счетчик 27 адреса предназначен для хранения старшего байта адреса операнда. Счетчик .28 команд обеспечивает хранение старшего байта адреса коман Регистр 29 адреса предназначен дл хранения младшего байта адреса. Арифметико-логический блок и блок управляющей памяти представляют собо блок обработки адресов и операндов, АБ, получив микрокоманду из УП, выпо няет арифметические, логические и сдвиговые операции над числами, храня«;имися в его регистрах или поступа щими по магистрали. Команды, включаю щие в себя собственно операции над числами и вычисления адресов операндов и следующей команды, реализуются как последовательности микрокоманд УП, разворачивающиеся на магистрали микрокоманд, при поступлении на вход УП команд. Функциональное распределение регистров блока регистров следующее: Р1 т - регистры общего назначения; S РЗ - регистр-указатель старшего байта адреса; Pt - регистр-указатель младшего байта адреса; Р5 - регистр-указатель стека; Рб - регистр старшего байта адреса команды; Р7 - регистр-счетчик команд. Одной из основных структурных проблем в 8-битных микропроцессорах является проблема адресации к памяти, поскольку 8-битным словом непосредственно можно адресоваться только к 25б ячейкам. Для того, чтобы адресоваться к большему числу ячеек необходимо на регистр адреса передать два байта адреса. 8-битный микропроцессор позволяет адресоваться к ячейкам памяти с помощью одного байта, при этом память целесообразно разбить на 3 части: область программ и данных (ОПД); область памяти блокнотного типа (ОПБ); область регистров периферийных устройств (оп). Каждая из перечисленных областей выбирается с помощью специальных признаков. Область памяти блокнотного типа (ОПБ) используется в качестве стека или как ЗУ, для хранения промежуточ-. ных результатов и переменных параметров. В качестве ОПБ в устройстве используется блок 19, содержащий 256 ячеек. Для считывания (или записи) информации из блокнотной памяти (или в блокнотную память) необходимо задать адрес, а так как блокнотная память состоит из 256 ячеек памяти, то для адресации достаточно восьми младших разрядов адреса, поэтому младшая часть адреса поступает в блок 19. Старшая часть адреса поступает в лок.постоянного (ПЗУ) или оперативного (ОЗУ) заполняющего устройства акже, как и младшая часть. ПЗУ или ЗУ образуют область программ и даных и область регистров периферийных стройств. Область регистров периферийных стройств (ОРП) вводится для логиеского сопряжения микропроцессора управляемым объектом. Емкость областей ОПБ и ОРП равна 56 ячейкам. Таким образом, адресаЦия к областям ОПБ и ОРП производитс 8 битами, причем без изменения старш Масти адреса области ОПД. В1нешняя адерсная магистраль включ ет в себя магистраль 30 (младших 8 раз рядов адреса) и магистраль k2 (старших 8 разрядов адреса). Признак памяти типа ОПД задается микропрограммно. Наличие в 13 разряд микрокоманды 1 определяет область ОПБ или ОРП, а отсутствие его опреде ляет область ОПД. Адрес данных от адреса команд отделяется микропрограммно. Обращаясь к счетчику 28 команд, определяют .область программ, а обращаясь к реги стру адреса 29 - область данных. , По сигналу 73 - Команда выдана, сформированному в блоке синхронизации 5, и при наличии на магистрали данных 17 команды обращения к ОРП элемент И 72 формирует сигнал 7, ус танавливающий запоминающий элемент 47 в 1. При выполнении команды блок 9 управляющей памяти генерирует последовательность микрокоманд, кото рая поступает на дешифратор 16 микро команд в случае обращений или К ОПБ, или к ОРП, формирует сигнал б5 уста навливающий запоминающий элемент k6 в 1.При выполнении команды блок 5 синхронизации формирует сигнал обращения к памяти 79 и в зависимости от состояния двух запоминающих элементо 6 и 7 производится выбор или ОПБ с помощью элемента И 71, или ОРП с помощью элемента И 70 по младшему байту адреса. После выполнения коман ды из блока 7 асинхронного приемапередачи поступает сигнал 66 - Информация принята, по которому запоминающие элементы и 7 устанавливаются в О. Благодаря тому, что обмен данными производится массивом и программа выполняется последовательно, в качестве узла, определяющего адрес следующей ячейки, выбирается счетчик Если хранить старшую часть адреса области данных и области программ на счетчиках адреса 27 и команд 28, топри выборке ячейки памяти достаточно будет передавать только младший байт адреса, микропрограммно определив обращение или к счетчику адреса, или к счетчику команд. Введение дополнительного блока управления адресаций не означает полного исключения адресации к памяти по 16-разрядному абсолютному адресу. Более того, адресация в поле памяти объемом ячеек без наличия на адресном регистре. 16-разрядного адреса принципиально невозможна. В отличие от известного в предлагаемом устройстве вместе с обычной полноразрядной адресацией, при которой требуется передача 2-х Байтов адреса, введена адресация по короткому 8-разрядному адресу к подобласти памяти. При выполнении программы команды выбираются из памяти, как правило, последовательно команда за. командой. Для перехода на программы имеются специальные команды. В электронно-вычислительных машинах (ЭВМ), построенных на элементной базе малой и средней интеграции счетчик команд наращивается на 1 при выполнении каждой команды и непосредственно адресует следующую команду. Иное дело в ЭВМ на микропроцессорной элементной базе. Здесь счетчик команд строится на регистрах большой интегральной схемы (БИС) микропроцессора. При выполнении каждой команды он также наращивается на 1, но уже не может непосредственно адресовать команду, поскольку дополнительно требуется передать сформированныйадрес по адресной магистрали в большие интегральные схемы памяти. Примерно то же происходит и при обращении к последовательному массиву операндов в содержательных командах, где необходима передача адреса операнда. Из-за ограниченности контактов БИС микропроцессора адресная магистраль выполняется 8-разрядной. Введение короткой адресации позволяет передать старший байт адреса только один раз для выбора подобласти памяти, а затем передавать при работе в подобласти только младший байт. Причем, поскольку старшие 8 разрядов схемы адресации выполнены как счетчик, а микропроцессор анализирует переполнение младших разрядов, объем выбранной подобласти может быть равным . Время передачи каждого байта адреса соизмеримо со временем выполнения операции в микропроцессоре, поэтому .исключение необходимости передачи старшего байта приводит к уменьшению времени выполнения команд, т.е. повышению быстродействия. Обычно программы и операнды размещаются в различных областях памяти Для микропроцессора, применяемого как элемент управления, появляются и внешние регистры, вводимые как область памяти. При этом эффективность адресации еще более снижается если эти оЬласти не разделены физическими признаками, что и происходит в известном устройстве, поскольку необходимо передавать 2 байта адреса как для операнда в памяти, для операнда во внешнем регистре, так и для выборки следующей- команды. Использование короткой адресации совместно с физическим разделением памяти на область программ, блокнотную память и область внешних регистров, еще более повышает эффективность структуры, так как позволяет обратиться ко всем трем областям с передачей только одного байта для каждой обла ти. Прежде чем начать работу, необходимо привести в исходное состояние БИС АБ и УП и запоминающие элементы микропроцессора. Для этого в блоке 23 пуска необходимо нажать кнопку Сброс. БИСы АБ и УП устанавливаютс в исходное состояние при подаче положительного импульса на выходе 10 блока 11 начальной установки, длительность которого должна быть больше или равна 2,1 мкс. При этом в УП 9 формируется микро команда Исходное состояние, по которой сигнал Конец команды устанавливается в 1 состояние, а в регистр следующего адреса заносится адрес начала команды, таким образом БИС готов к приему команды. По сигналу Пуск 22 с пульта оператора 23 команда Начальный пуск принимается на регистр команд УП 9 формирует последовательность микрокоманд, по которым выполняются следующие действия. Устанавливается в 1 состояние указатель стека Р5; устанавливается в О состояние старший байт адреса Рб; устанавливается в О состояние счетчик команд Р7; содержимое регистра Рб передается в адресную магистраль; содержимое регистра Р7 пер дается в адресную магистраль. В момент выдачи старшего байта адреса команды (содержимое Рб) де1518шифратор 16 микрокоманд формирует сигнал 58, устанавливающий в 1 запоминающий элемент S, а АБ 1 формирует сигнал 5 Адрес выдан, по которому возбуждается элемент И 53 и старший байт адреса команды, поступающий по внутренней адресной магистрали 26, принимается на счетчик команд 28, после приема старшего байта адреса формируется ответный сигнал Адрес принят 66 из блока 7 асинхронного приема-передачи . и запоминающий элемент устанавливается в О, а АУ 1, получив ответный сигнал Адрес принят, формирует сигнал Исполнено 8 для УП 9. Передача старшего байта адреса команды в счетчик команд осуществляется только один раз при.начальной установке. Затем изменение 8 младших разрядов счетчика команд выполняется микропрограммно, а 8 старших разрядов аппаратно. Если в момент изменения состояния счётчика команд в АУ 1 возникает импульс Переполнения б2, свидетельствующий о переходе в следующую страницу памяти, который поступает на логический элемент И 61, то к счетНИКУ 28 команд добавляется 1, обеспечивая переход к следующей странице. Передача старшего байта адреса команды осуществляется и при выполнении команды межстраничного условного перехода. После передачи старшего байта адреса команды УП переходит к формированию следующей микрокоманды Передача младшего байта адреса. Если при передаче адреса ни один из запоминающих элементов 3 и АЗ не установлен в 1, то возбуждается логический элемент И 52 и младший байт адреса принимается на регистр 29 адреса. При передаче младшего байта адре са блок 6 управления адресацией формирует сигнал Признак младшего байта 15 (56) АУ 1 - сигнал Выдан адрес 153, а блок 7 асинхронного приема-передачи - сигнал Выдан адрес, задержанный 152 (88). По этим сигналам в блоке 5 управения. возбуждается логический элемент 151 и устанавливает запоминающий лемент 128 в 1. Дешифратор 16 икрокоманд устанавливает запоминаю4|ий элемент 136 в 1, определяя режим чтения. После приема младшего байта адреса блок асинхронного приема-передачи формирует сигнал Адрес принят 123 по которому в блоке синхронизации возбуждается логический элемент И 12, устанавливая по цепи элемент ИЛИ 130, элемент НЕ 138, элемент 137 задержки, И 139 в 1, запоминаю щий элемент , формирующий по цепи элемент задержки , элемент И U5 сигнал Выборка. В блоке 7 асинхронного приема-пер дачи через 00 не относительно сигна ла Выборка по цепи элемент 89 задержки, элемент И 93, элемент НЕ 100, элемент 98 задержки, элемент И 97 устанавливается в 1 запоминающий элемент 103, формирующий сиг нал Информация выдана 111, по которому считанная из памяти команда принимается на регистр команд УП 9. По приему команды УП 9 формирует ответный сигнал Информация принята Пример 1. Рассмотрим алгоритм выполнения записи в блокнотную память или эо внешние регисты. На фиг. 5 и б изображены -временные диаграммы выполнения команды. Команда Запись в блокнотную память внешние регистры двух байтовая. В первом байте хранится команда, во втором - адрес ячейки блокнотной памяти или внешнего регистра. У известного устройства команда подобного типа байтовая, так как адрес ячейки или внешнего регистра задается 16 разрядами. Выполнение команды делится на 3 этапа: формирование адреса ячейки операнда; запись содержимого регистра в блокнотную память; формирова ние адреса следующей команды. При обращении к области блокнотн го типа или к области регистров периферийных устройств в коде команды задается признак области. В коде команды задается признак области внешних регистров, поэтому при обращении к блокнотной памяти запоминающий элемент 7 остается в СОСТОЯНИИ Команда состоит из четырех микро команд, по которым выполняются след ющие действия. 520 Содержимое счетчика команды увеличивается на 1 и выдается в адресную магистраль. Содержимое следующей за командой ячейки принимается по магистрали данных в АУ 1 на накопительный регистр, затем передается в адресную магистраль. Содержимое регистра передается в магистраль данных и формируется признак обращения к области блокнотной памяти или внешнего регистра. Содержимое счетчика команд увеличивается на 1 и передается.в адресную магистраль. В результате выполнения 1-ой микрокоманды содержимое счетчика 15 команд в АУ 1 увеличивается на 1 и передается.в адресную магистраль 26 с сигналом квитирования Выдан адрес (ВА). По сигналу ВА (5) блок 6 управления адресацией обеспечивает прием младшего байта (схема логического элемента И 52) адреса на регистр адреса, обеспечив прием адреса, блок 7 асинхронного приема-передачи формирует сигнал Принят адрес (ПА) элемент 87 задержки по цепи элемент 80, элемент И 82, элемент задержки 85, магистральный переключающий элемент 86. После выполнения акта обмена по адресной ,магистрали, АУ выдает сигнал Исполнено 8, по которому выбирается из УП9 следующая микрокоманда. По сигналу ПА блок синхронизации обеспечивает формирование сигнала Выборка памяти Й9 по цепи элемент И 151, запоминающий элемент 128, элемент 122 задержки, элемент И 12, элемент ИЛИ 130, элемент НЕ 138, элемент 137 задержки, элемент И 139, запоминающий элемент Й2, элемент задержки, элемент И U5 для считывания операнда, а блок асинхронного приема-передачи по цепи элемент 89 задержки, элемент И 93, элемент И 95, элемент 98 задержки, элемент НЕ 100, элемент И 97, запоминающий элемент 103, магистральный переключающий элемент 107 формирование сигнала Выданы данные 111. По второй микрокоманде АУ 1 принимает операнд по магистрали 17 анных, формируя сигнал Приняты даные, и лерадает его в адресную магистраль 2б с сигналом квитирования А 81, прием адреса выполняет аналогично вышеописанному.

По третьей микрокоманде содержани регистра передается на накопительный регистр, а затем в магистраль 1 данных. Дешифратор 16 микрокоманд дешифрирует микрокоманду и устанавливает запоминающий элемент 135 в блоке 5 синхронизации (режим записи) и запоминающий элемент 6, являющийся признаком области блокнотной памяти или области внешних регистров в блоке управления адресацией в состояние 1. По сигналу ВД, который формируется после выполнения третьей микрокоманды, блок-синхронизациивырабатывает сигнал Обращения к памяти 1, по которому в блоке 6 управления адресацией формируется сигнал Выборка блокнота 78 с помощью логического элемента И 71, и информация, поступающая из АУ, записывается в ячейку, адрес которой находится на регистре адреса. После записи информации в ячейку памяти блок асинхронного приема-передачи по цепи элемент И.90 запоминающий элемент 110, элемент 118 задержки, элемент ИЛИ 117, магистральный переключающий элемент 10 вырабатывает ответный сигнал Приняты данные, АУ1 выдает сигнал Исполнено 8 и УП 9 переходит к формированию следующей -микрокоманды, по которой содержимое счетчика команд (Р7) увеличивается на 1 и передается в адресную магистраль, формируя адрес следующей команды и единичное значение конца команды.

Аналогичная команда у известного устройства выполняется следующим образом.

Содержимое счетчика команд увеличивается на 1 и 6 старших разрядов и передается на регистр адреса. 8 младших разрядов передаются на регистр адреса. Содержимое следующей за командой ячейки принимается на регистр Н. Содержимое счетчика команд увеличивается на Гиб старших разрядов и передается на регистр адреса. 8 младших разрядов передаются на регистр адреса. Содержимое следующей ячейки принимается на .регистр. Содержимое регистра Н передается ка регистр адреса. Считывается содержимое ячейки памяти. Содержимое счетчика команд увеличивается на 1.

Выполнение записи информации во внешний регистр происходит аналогично вышеописанному за исключением

того, что при выполнении команды, в которой присутствует признак области внешних регистров, в блоке 6 управле-. ния адресацией устанавливается в 1 S запоминающий элемент по сигналу Команда выдана 73,сформированному в блоке 5 синхронизации с помощью логического элемента И 57 при совпадении следующих условий: отсутствие сигнала Выборка Бл 163; отсутствие сигнала Выборка ПУ 1бО; наличие признака Конец команды 21; отсутствие сигнала Останов 164; наличие сигнала Выданы данные 166 и

5 при наличии на магистрали 17 данных команды с признаком.

В случае команды записи во внешний регистр по t микрокоманде возбуждается логический элемент И 70 и

0 формируется сигнал Выборка внешнего регистра 7().

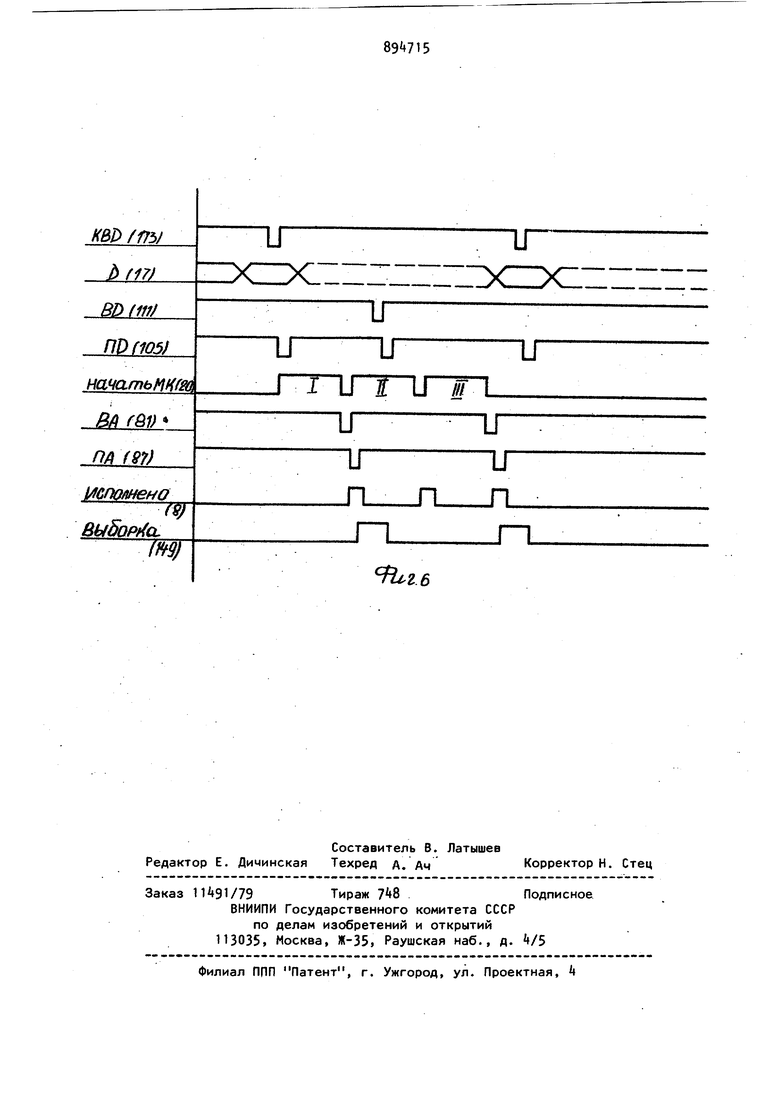

Пример 2. Рассмотрим алгоритм выполнения считывания из области данных.

5 Прежде чем начать обмен данными необходимо предварительно загрузить счетчик 27 адреса.

Загрузка счетчика выполняется командой, по которой содержимое региО стра 3 передается в адресную магистраль. При этом по сигналу kk с дешифратора 16 команд устанавливается в 1 запоминающий элемент и по сигналу ВЛ54 из АУ1 возбуждается логический элемент И 49, старший байт

5 адреса записывается на счетчик адреса

Благодаря тому, что обмен данными производится массивом и старшая часть адреса области данных хранится

0 на счетчике адреса, при выборке ячейки памяти достаточно будет передавать .только младший байт адреса.

Команда считывания из области 5 данных состоит из трех микрокоманд, по которым выполняются следующие действия.

Содержимое регистра Р4 (региструказатель младшего байта адреса) уве- 0 личивается на 1 и передается в адресную магистраль 26. Содержимое ячейки принимается на накопительный регистр 13, а затем передается на регистр (РО-Р2). Содержимое счет.чика команд увеличивается на 1 и передается в адресную магистраль.

В результате выполнения первой микрокоманды содержимое регистра-ука23зателя младшего байта адреса АУ1 уве личивается на 1 и передается в адресную магистраль 26 с сигналом витирования Выдан адрес (ВА), Осталь ные действия аналогичны действиям, выполняемым по первой микрокоманде в команде Запись информации в блокнотную память. По второй микрокоманде АУ1 принимает операнд по магистрали 17 данных формируя сигнал Приняты данные и записывает его в регистр. По третьей микрокоманде содержимое счетчика 15 команд увеличивается на 1 и передается в адресную магистраль 2б, формируя адрес сле,4Ую щей команды и единичное значение кон ца команды. Если в момент изменения состояния . указателя данных в АУ1 возникает импульс переполнения 62, свидетельству ющий о переходе в следующую страницу памяти, то возбуждается логический . элемент И 50, увеличивая счетчик адреса на 1. Таким образом, введение дополнительной схемы управления адресацией при последовательном выполнении опе раций над последовательным массивом данных в 8-разрядной структуре процессора позволяет исключить необходимость передачи двух байтов адреса при обращении к областям памяти емкостью до 64k ячеек. Это сокращае время выполнения операций типа регистр-регистр на цикл передачи стар го байта адреса команды, т.е. приме .но на 2Q%, при выполнении операций регистр-память на цикл передачи старшего байта адреса команды и цик передачи старшего байта адреса операнда, т.е. на 25. При- выпол нении 2-байтовых команд, над 2-байтовыми операндами время выполнения сокращается на 30%. Таким .образом, быстродействие системы увеличивается по сравнению с известной в среднем на 25%. Кроме того, для прямой адресации операнда- при использовании прототипа необходимо иметь два байта адреса в формате команды. В 8-байтном процессоре эта необходимость исключается, что обеспечивает экономию памяти примерно на 30. Формула изобретения 1. Микропроцессор, содержащий арифметико-логический блок, регистр 52k состояния, блок синхронизации, блок управляющей памяти, блок регистров, дешифратор микрокоманд, регистр адреса, причем первый управляющий входвыход арифметико-логического блока соединен с управляющим входом-выходом регистра состояния, информационный вход которого соединен с информационным входом арифметико-логического блока, второй управляющий входвыход которого соединен с первым управляющим входом-выходом блока управляющей памяти, выход которого соединен со входом арифметико-логического блока, третий управляющий вход-выход .которого соединен с первым входом - выходом блока синхронизации, второй вход-выход которого соединен со вторым управляющим входомвыходом блока управляющей памяти, первый информационный вход-выход которого является входом-выходом микропроцессора, информационный вход- . выход арифметико-логического блока соединен с первым информационным входом-выходом блока управляющей памяти, второй информационный входвыход которого соединен с информационным входом-выходом регистра состояния, второй вход блока синхронизации соединен с первым выходом дешифратора микрокоманд, вход которого соединен с выходом блока управляющей памяти, вход-выход блока регистров соединен с информационным входом-выходом арифметико-логического блока, первый и второй выходы блока регистров соединены со входом регистра адреса, выход которого является первым адресным выходом микропроцессора, вход блока регистров соединен с выходом блока управляющей памяти, отличающийся тем, что, с целью повышения быстродействия, в него введены блок управления адресацией, блок асинхронного приема-передачи, блок начальной установки, блок блокнотной памяти, блок пуска, счетчик адреса, счетчик команд и адресный мультиплексор, причем первый выход блока управления адресацией соединен с управляющим входом блока блокнотной памяти, адресный вход которого соединен с выходом регистра адреса, управляющий вход которого соединен со вторым выходом блока управления адресацией, третий выход которого соединен с управляющим входом счетчика адреса, информационный вход которого соединен со вторым выходом блока ре гистров, четвертый выход блока упра ления адресацией является управляю щим выходом микропроцессора, пятый, выход блока управления адресацией со динен с первым входом-выходом блока синхронизации, третий вход-выход коTopioro соединен с входом-выходом блока асинхронного приема-передачи, выход которого соединен с пятым выхо дом блока управления адресацией, пер вый вход которого соединен с выходом блока синхронизации, первый вход которого соединен с первым входом блока пуска, второй выход которого соединен со входом блока начальной уста новки, выход которого соединен с установочными входами блока управляющей памяти, арифметико-логического блока, блока синхронизации и блока управления адресацией, второй вход которого соединен с выходом дешифратора микрокоманд, вход-выход блока блокнотной памяти соединен со входом выходом блока регистров, выход счетчика адреса соединен с первым входом адресного мультиплексора, выход кото рого является вторым адресным выходом микропроцессора, информационный вход счетчика адреса соединен со вто рым выходом блока регистров, управля ющий вход счетчика команд соединен с третьим выходом блока управления адресацией, выход счетчика команд соединен со входом адресного мультиплексора . 2. Микропроцессор по п.1, о т л и ч. ающийся тем, что блок управления адресацией-содержит первый, второй, третий и четвертый запоми нающие элементы, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем первые входы первого второго и третьего запоминающих элементов соединены соответственно с первым, вторым и третьим входами блока, вторые входы первого, второго и третьего запоминающих элементов соединены со входом начальной установки блока, первый выход первого запоминающего элемента соединен соответственно с первыми входами первого и второго элементов И, второй вход первого элемента И соединен с первыми входами третьего и четвертого элементов И и с четвертым входом блока, второй выход первого запоминающего элемента соединен 1со вторым входом третьего запоминающего элемента, первый выход второго запоминающего элемента соединен со вторым входом четвертого элемента И, выход которого соединен с управляющим входом счетчика команд, второй выход второго запоминающего элемента соединен с третьим входом третьего элемента И, выход которого соединен с выходом синхронизации и первы1-( управляющим выхсдом блока, выход первого элемента И соединен со вторым управляющим выходом блока, второй вход второго элемента И соединен с первым входом пятого элемента И и с пятым входом блока, второй вход пятого элемента И соединен с первым выходом второго запоминающего элемента, выход второго элемента И соединен с первым счетным выходом блока, выход пятого элемента И соединен со вторым счетным выходом блока, счетные входы первого, второго и третьего запоминающих элементов соединены соответственно с.первым, вторым и третьим счетными входами блока, первый вход шестого элемента И соединен со счетным входом третьего запоминающего элемента, выход которого соединен со вторым входом шестого элемента И, выход которого соединен со счетным входом четвертого запоминающего элемента, первый вход седьмого элемента И соединен с выходом третьего запоминающего элемента и первым входом восьмого элемента И, второй вход седьмого элемента И соединен с шестым входом блока и со вторым входом восьмого элемента И, выход седьмого элемента И соединен с первым и вторым адресными выходами блока, выход восьмого элемента И соединен с третьим адресным выходом блока, первый вход девятого элемента И соединен с адресным входом блока, а второй вход - с седьмым входом блока, выход девятого элемента И соединен с первым входом четвертого запоминающего элемента, второй вход которого соединен со вторым входом третьего запоминающего элемента, первый и второй выходы четвертого запоминающего элемента соединены соответственно с третьими входами восьмого и седьмого элементов И. 3. Микропроцессор по п.1, от ичающийся тем, что блок асинхронного приема-передачи содержит первый и второй запоминающие элементы, первый, второй, третий, четвертый, пятый и шестой элементы И, первый, второй, третий, четвертый и пятый элементы задержки, первый, второ и третий магистральные переключающие элементы, элемент НЕ и элемент ИЛИ, причем вход первого элемента задержки соединен с первым входом блока, а выход - с первым входом первого элемента И, второй вход которого сое динен со входом первого элемента задержки, выход первого элемента И соединен со входом второго элемента задержки и с первым входом первого магистрального переключающего элемента, второй Вход которого соединен с выходом второго элемента задержки и первым выходом блока, выход первого магистрального переключающего эле мента соединен со вторым выходом блока, вход третьего элемента задер ки соединен с первым входом второго элемента И и с входом выборки блока, а выход - с первым входом третьего элемента И, второй вход которого сое динен со вторым входом блока и с первым входом четвертого элемента И, выход третьего элемента И соединен со входом четвертого элемента задерж ки, выход которого соединен со входом элемента НЕ, выход которого соед нен с первым входом пятого элемента И, второй вход которого соединен с выходом третьего элемента И, выход пятого элемента И соединен с первым входом первого запоминающего элемента , второй вход которого соединен с третьим выходом блока, второй вход четвертого элемента И соединен 528 с третьим входом блока, первый вход шестого элемента И соединен со вторым выходом блока, вторые входы второго, четвертого и. шестого элементов И соединены соответственно с четвертым, третьим и пятым входами блока, выход второго элемента И соединен со счетным входом второго запоминающего элемента, первый вход которого соединен с выходом шестого элемента И, второй вход второго запоминающего элемента соединен с первым входом шестого элемента И, а выход - с первым входом элемента ИЛИ и со входом пятого элемента задержки, выход которого соединен со вторым входом элемента ИЛИ, выход которого соединен с первым входом второго магистрального . переключающего, элемента, второй вход которого .соединен с первым входом элемента ИЛИ, а выход - с третьим выходом блока и со вторым входом первого запоминающего элемента, выход которого соединен с первым вxoдo третьего магистрального переключающего элемента, второй вход которого соединен с выходом четвертого элемента И, выход третьего магистрального переключающего элемента соединен с первым, входом шестого элемента И. Источники информации, принятые во внимание при экспертизе 1.8-битный микропроцессор 8008-1. Каталог интегральных схем фирмы Intel США. 2.Руководство к пользованию микро-ЭВМ Micral фирмы Р2Е (прототип) .

Авторы

Даты

1981-12-30—Публикация

1979-12-12—Подача