Область техники, к которой относится изобретение

Изобретение относится к области автоматического управления, запуском, синхронизации и стабилизации генераторов электронных колебаний или импульсов.

Уровень техники

Среди существующих методов синтеза гармонических сигналов широкое распространение приобрели схемы с фазовой автоподстройкой частоты (ФАПЧ). Системы с ФАПЧ относятся к следящим системам со сравнивающим устройством, выполненном в виде фазового дискриминатора (фазовый детектор). В качестве схемы фазового сравнения может применяться пассивный балансный смеситель, субгармонический смеситель, логический элемент исключающего «ИЛИ» и др. Недостатком таких схем является ограниченная полоса захвата, что требует введение дополнительных мер по обеспечению синхронизма петли.

Известна схема частотно-фазового детектора (ЧФД) по патенту US 4322643, 30.03.1982 в которой предложена схема фазового компаратора на основе цифровых логических схем с петлей обратной связи и сбросом состояния триггеров, что обеспечивает помимо сравнения фаз входных сигналов, также сравнение частот сигналов. Описанная особенность максимально расширяет полосу захвата петли ФАПЧ до предела, который может обеспечить генератор, управляемый напряжением (ГУН). Схема ЧФД вырабатывает короткие импульсы управления ключами зарядно-разрядного блока (ЗРБ), длительность которых соответствует разнице фаз входных сигналов.

Недостатком данной схемы является искусственно увеличенная длительность импульсов управления из-за задержки распространения сигнала сброса триггеров, что приводит к одновременному включению режимов стока и истока блока ЗРБ, которое приводит к увеличению среднего действующего значения напряжения шума.

Наиболее близким к заявленному техническому решению является схема ЧФД с двумя блоками задержки сигнала, отличающиеся тем, что срабатывают на фронт или спад сигнала. При этом длительность импульса сброса определяется разницей времени задержки двух блоков и выбирается так чтобы иметь минимальное значение достаточное для срабатывания схемы сброса в блоках триггеров US 6192094 B1, 20.02.2001. Недостатком данного решения является расширенное время управляющих импульсов, которое складывается из времени сброса триггеров, дополнительного времени задержки в течении которого происходит срабатывание ключей зарядно-разрядного блока и другие эффекты, дополнительно затягивающие время активной работы ключей.

Раскрытие сущности изобретения

Задачей, на решение которой направлено заявляемое изобретение является создание схемы ЧФД с минимальной длительностью импульсов управления для снижения среднего действующего значения шумового напряжения.

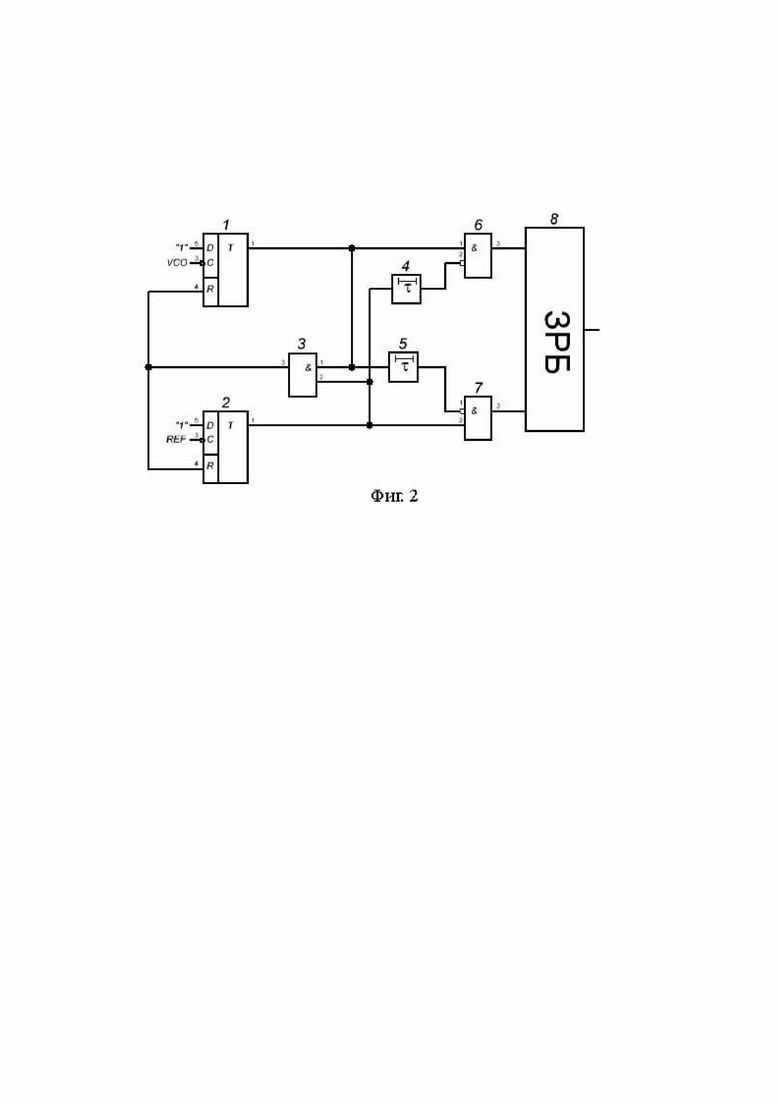

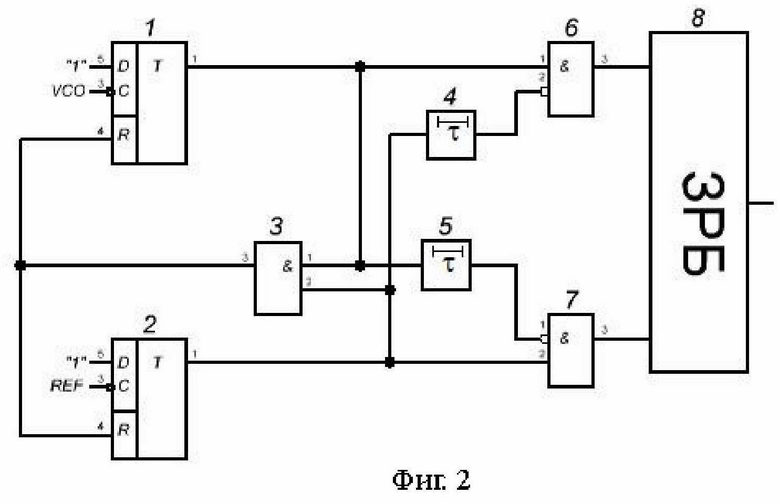

Данная задача решается за счет того, что заявленная схема частотно-фазового детектора, характеризующаяся тем, что состоит из триггера с асинхронным сбросом, синхронизируемого по фронту (1), на вход синхроимпульса, которого подается сигнал подстраиваемой частоты и триггера с асинхронным сбросом, синхронизируемого по фронту (2), на вход синхроимпульса, которого подается сигнал опорной частоты, выход триггера (1) подключен к первому входу логического элемента с функцией логического умножения (3), выход триггера (2) подключен ко второму входу логического элемента с функцией логического умножения (3), выход элемента (3) подключен ко входам сигнала асинхронного сброса триггеров (1) и (2), выход триггера (1) подключен к первому входу логического элемента с функцией логического умножения (6) и ко входу элемента задержки (5), выход триггера (2) подключен ко второму входу логического элемента с функцией логического умножения (7) и ко входу элемента задержки (4), выход элемента задержки (4) подключен ко второму инверсному входу логического элемента с функцией логического умножения (6), выход элемента задержки (5) подключен к первому инверсному входу логического элемента с функцией логического умножения (7), выход логического элемента с функцией логического умножения (6) поступает на первый вход управления зарядо-разрядного блока (8), выход логического элемента с функцией логического умножения (7) поступает на второй вход управления зарядо-разрядного блока (8).

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является обеспечение возможности независимой настройки длительности времени срабатывания управляющих импульсов напряжения ЧФД независимо от времени срабатывания схемы асинхронного сброса триггеров. Длительности управляющих импульсов напряжения ЧФД определяются временем срабатывания в элементах задержки (4) и (5) и могут выбираться независимо друг от друга, что обеспечивает независимую настройку длительности для каждого импульса управления отдельно.

Схема частотно-фазового детектора с минимальной длительностью управляющих импульсов, характеризующийся тем, что состоит из двух триггеров с асинхронным сбросом 1, 2, три логических элемента с функцией логического умножения 3, 6, 7, два элемента задержки 4, 5, причем на первый вход триггера 1 поступает сигнал подстраиваемой частоты, а на первый вход триггера 2 поступает сигнал опорной частоты, при этом выход триггера 1 соединен с первым входом логического элемента 3 и с первым входом логического элемента бис входом элемента задержки 5; выход триггера 2 соединен со вторым входом логического элемента 3 и со вторым входом логического элемента 7 и с входом элемента задержки 4; выход элемента задержки 4 соединен со вторым инверсным входом логического элемента 6, а выход элемента задержки 5 соединен с первым инверсным входом логического элемента 7; при этом импульсы управляющего напряжения формируются на выходах логических элементов 6, 7.

Краткое описание чертежей

Сущность изобретения поясняется чертежами, на которых изображено:

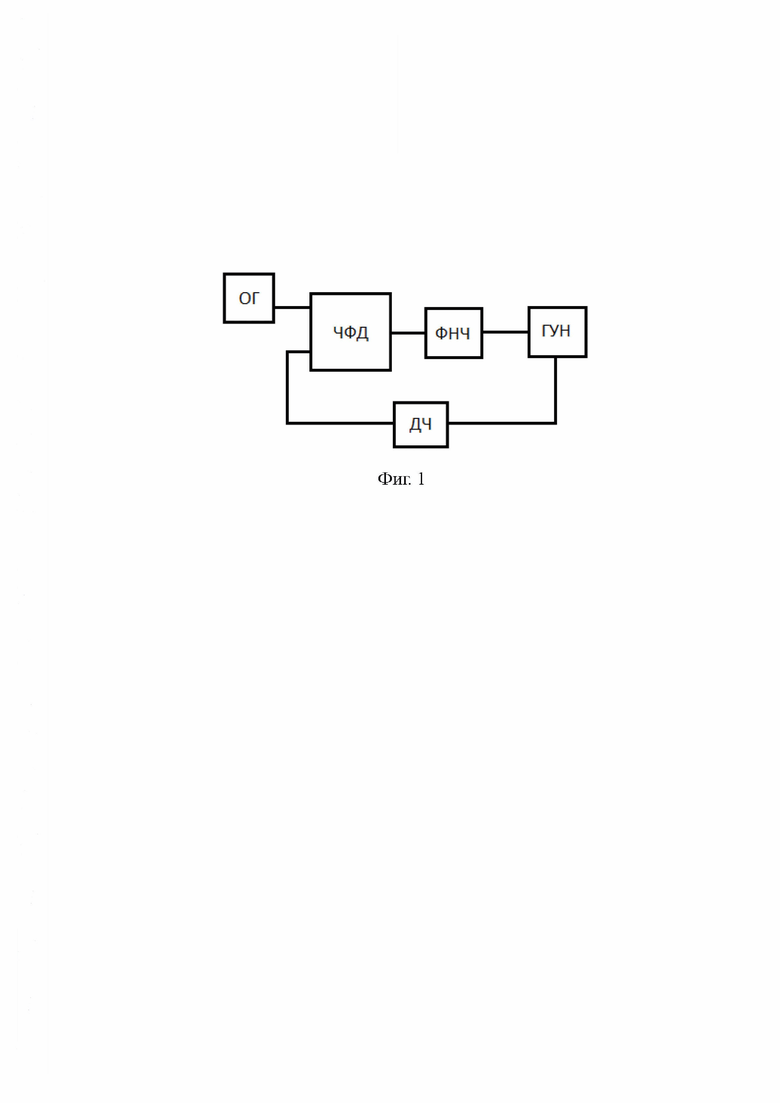

На фиг. 1 - блок-схема петли фазовой автоподстройки частоты;

На фиг. 2 - принципиальная электрическая схема ЧФД с минимальной длительностью управляющих импульсов;

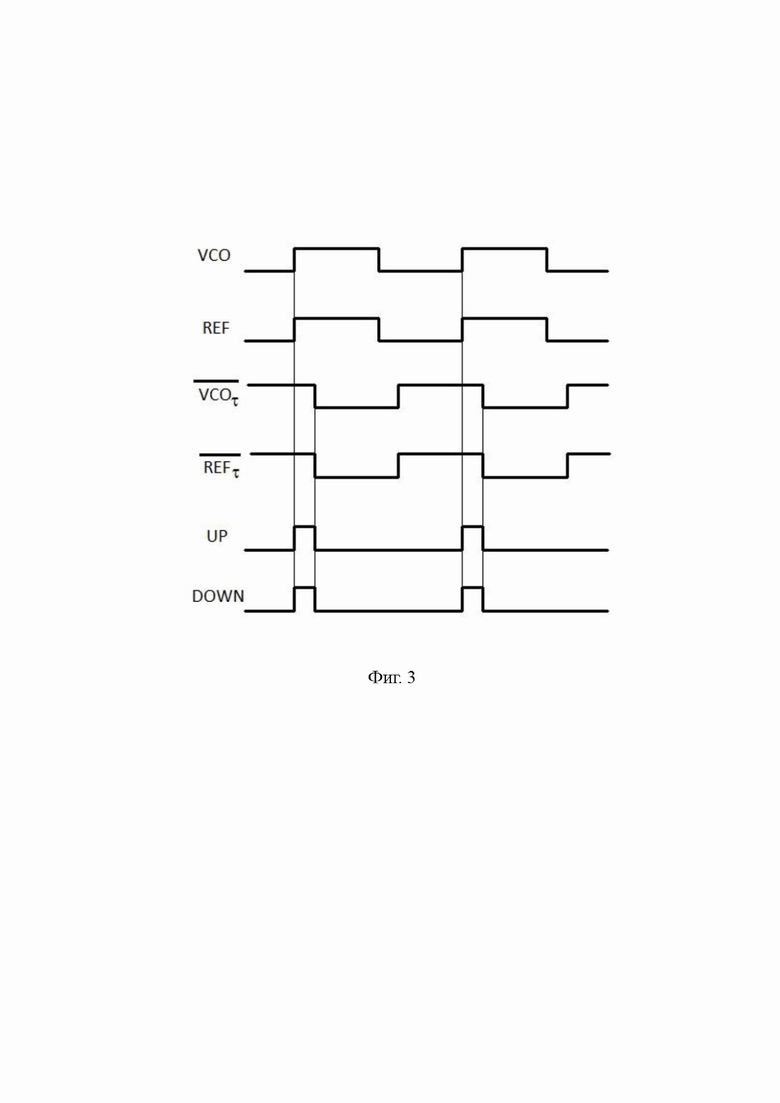

На фиг. 3 время-импульсная диаграмма работы ЧФД с минимальной длительностью управляющих импульсов.

Осуществление изобретения

Схема частотно-фазового детектора формирует два импульсных сигнала управления, которые поступают на вход зарядо-разрядного блока. Каждый из управляющих импульсов отвечает за повышение либо снижение напряжение управления генератора, управляемого напряжением. Изменение напряжения управления пропорционально разнице длительности импульсов управления ЧФД. В режиме синхронизма петли фазовой авто подстройки частоты после процесса захвата частоты корректировка управляющего напряжения больше не требуется, поэтому длительность двух управляющих импульсов на выходе ЧФД будет практически одинаковой. На вход синхроимпульса триггера 1 поступает сигнал подстраиваемой частоты, который вызывает переключение состояние триггера в состояние с логической единицей. Аналогичное переключение состояния происходит в триггере 2 при поступлении на его вход синхроимпульса сигнала опорной частоты. После того как на выходах триггеров 1 и 2 сформируется сигналы логически высокого уровня, то логический элемент 3 переключится в состояние логического нуля, что приведет к срабатыванию асинхронной схемы сброса в обоих триггерах 1 и 2 и переключению обоих в состояния логического нуля после некоторой задержки связанной с распространением сигнала сброса триггеров. После сброса при поступлении сигналов опорной и подстраиваемой частоты процесс переключения состояний триггеров повторяется. Сигналы с выхода триггеров 1 и 2 поступают на входы элементов 4 и 5, на выходе которых формируются копии выходных сигналов триггеров с определенной задержкой τ. В логическом элементе 6 производится процесс логического умножения выходного сигнала триггера 1 и инверсной копии выходного сигнала триггера 2 с задержкой τ, а в логическом элементе 7 производится процесс логического умножения выходного сигнала триггера 2 и инверсной копии выходного сигнала триггера 1 с задержкой τ. На выходах логических элементов 6 и 7 формируются управляющие импульсы напряжения, которые поступают на вход ЗРБ. В режиме синхронизма длительность управляющих импульсов одинакова и равна времени задержки т и может быть выбрана с минимальной длительностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1981 |

|

SU1014123A1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Цифровой синтезатор частот | 1986 |

|

SU1403367A1 |

| Синтезатор частоты | 1984 |

|

SU1257845A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2394367C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2016 |

|

RU2622628C1 |

| Цифровой синтезатор частот | 1987 |

|

SU1510080A1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2665241C1 |

| Цифровой синтезатор частот | 1984 |

|

SU1197073A2 |

Изобретение относится к частотно-фазовым детекторам (ЧФД). Техническим результатом является обеспечение возможности независимой настройки длительности времени срабатывания управляющих импульсов напряжения ЧФД независимо от времени срабатывания схемы асинхронного сброса триггеров. Для этого схема частотно-фазового детектора состоит из двух триггеров с асинхронным сбросом 1, 2, трех логических элементов с функцией логического умножения 3, 6, 7, двух элементов задержки 4, 5. Причем на первый вход триггера 1 поступает сигнал подстраиваемой частоты, а на первый вход триггера 2 поступает сигнал опорной частоты, при этом выход триггера 1 соединен с первым входом логического элемента 3, и с первым входом логического элемента 6, и с входом элемента задержки 5. Выход триггера 2 соединен со вторым входом логического элемента 3, и со вторым входом логического элемента 7, и с входом элемента задержки 4; выход элемента задержки 4 соединен со вторым инверсным входом логического элемента 6, а выход элемента задержки 5 соединен с первым инверсным входом логического элемента 7; при этом импульсы управляющего напряжения формируются на выходах логических элементов 6, 7. 3 ил.

Схема частотно-фазового детектора с минимальной длительностью управляющих импульсов, характеризующаяся тем, что состоит из двух триггеров с асинхронным сбросом 1, 2, трех логических элементов с функцией логического умножения 3, 6, 7, двух элементов задержки 4, 5, причем на первый вход триггера 1 поступает сигнал подстраиваемой частоты, а на первый вход триггера 2 поступает сигнал опорной частоты, при этом выход триггера 1 соединен с первым входом логического элемента 3, и с первым входом логического элемента 6, и с входом элемента задержки 5; выход триггера 2 соединен со вторым входом логического элемента 3, и со вторым входом логического элемента 7, и с входом элемента задержки 4; выход элемента задержки 4 соединен со вторым инверсным входом логического элемента 6, а выход элемента задержки 5 соединен с первым инверсным входом логического элемента 7; при этом импульсы управляющего напряжения формируются на выходах логических элементов 6, 7.

| US 6192094 B1, 20.02.2001 | |||

| Частотно-фазовый детектор | 1980 |

|

SU1040591A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

Авторы

Даты

2024-02-28—Публикация

2023-10-02—Подача