СП

со

о

О)

Изобретение относится к вычислительной технике и может быть использовано в устройствах синхронизации, обеспечивающих требуемую последовав тельность операций.

Известно устройство синхронизации, используемое для выработки определенной последовательности синх роимпульсов и содержащее элемент И, счетчик,переключатель и одновибратор 1.

Однако в известном устройстве отсутствует режим ожидания, что не позволяет осуществлять синхронизацию работы двух устройств.

Наиболее близким к предлагаемому является устройство синхронизации, содержащее два регистра, два блока ко1ммутации и элемент ИЛИ. В каждом текущем состоянии формируется следующее состояние устройства синхронизации . Запись кодов в регистры осуществляется в четные и нечетные такты синхроимпульсами, поступающим по шинам фазовой синхронизации. Входение в режим ожидания осуществляется при отсутствии логических условий на входах схем коммутации, при этом в соответствующий регистр записывается полностью нулевой код 00

Состояние, соответствующее нулевому коду для этого регистра, является нерабочим и используется схемой ИЛИ для выработки сигнала, запрещающего изменение состояния другого регистра, в котором он может находиться до тех пор, пока на входах соответствующей схемы коммутаци не появятся логические условия, необходимые для перевода устройства синхронизации в следующее состояние 2 .

Недостатками указанного устройства являются наличие одного нерабочего состояния, соответствующего коду 000, а также невозможность использования всех кодов (кроме кода 000) для организации режима ожидания. Кроме того, отсутствует аппаратный Контроль для режима разделения времени по каналам синхронизации. Все это сужает функциональные возможности устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в устройство для синхронизации, содержащее два регистра, два коммутатора, причем выходы первого и второго коммутаторов соединены соответственно с информационными входами первого и второго регистров, группа выходов первого регистра является первой группой выходов фазовой синхронизации устройства и соединена соответственно с группой управляющих входов второго коммутатора, группа информационных входов которого является первой группой входов сигналов логического условия устройства, вторая группа входов сигналов логического условия устройртва соединена соответственно с группой информационных входов первого коммутатора, группа управляющих входов первого коммутатора соединена с группой выходов второго регистра и является второй группой выходов фазовой синхронизации устройства, первый и второ входы фазовой синхронизгщии устройства соединены соответственно с синхровходами первого и второго регистров, вход разрешения следующего состояния устройства соединен с управляющим входом второго регистра, введен блок сравнения, первая и вторая группы входов которого соединены с группой выходов первого и второго регистров соответственно, выход блока сравнения соединён с управляющим входом первого регистра и является контрольным выходом режима ожидания устройства.

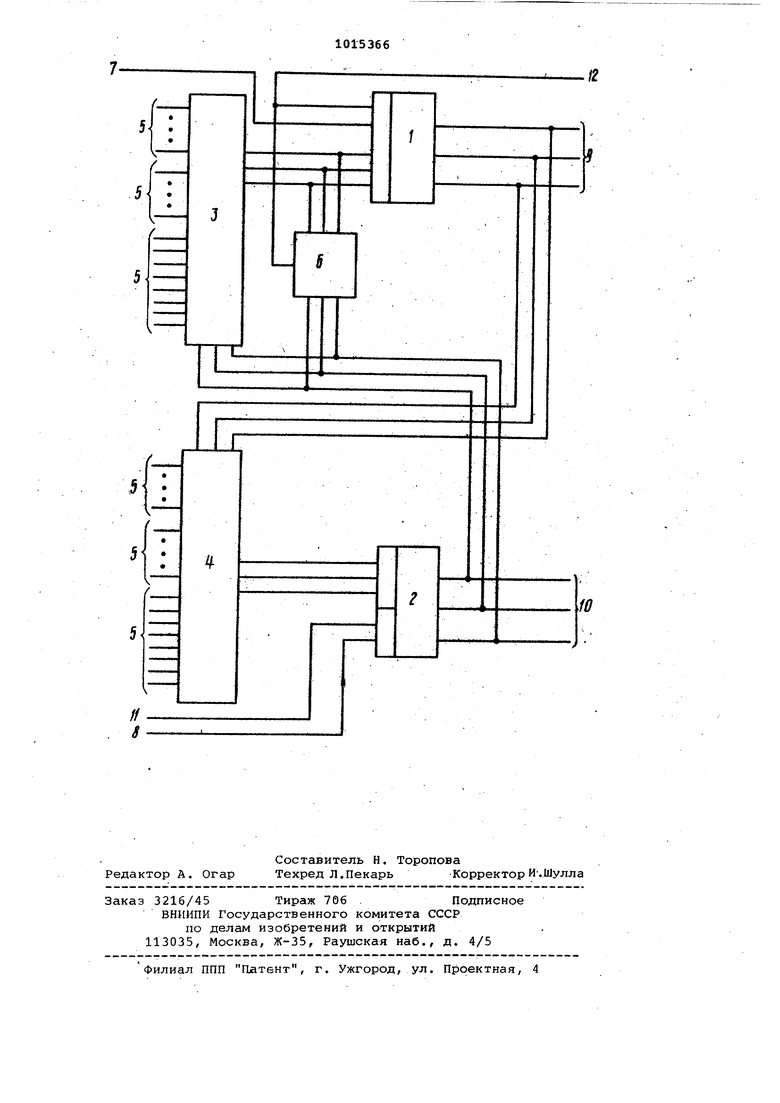

На чертеже приведена схема устройства.

Устройство содержит регистры 1 и 2, коммутаторы 3 и 4, группы 5 входов сигналов логических ус,ловий, блок 6 сравнения, входы 7,8 и 11 фазовой синхронизации и группы 9 и 10 выходов фазовой синхронизации.

Устройство работает следующим образом.

Устройство для синхронизации, изображенное на чертеже, позволяет организовать режим ожидания на первом регистре. Аналогичным образом может быть организован режим ожидания и на втором регистре. Для этбго входы блока сравнения необходимо подключить к выходам регистра 1 и коммутатора 4, а его выход - к управляющему входу регистра 2. Подключение двух блоков сравнения позволяет организовать режим ожидания попеременно и на первом, и на втором регистрах. Принцип работы устройства при организации режима ожидания во всех случаях одинаков и заключается в выработке блоком сравнения сигнала, запрещающего изменение состояния регистра при попытке на нем в данный момент времени повторить состояние другого регистра.

Предположим, что код на выходе регистра 2 определяет состояние устройства синхронизации в данный момент времени и поступает на управляющие ВХОД5Л ко№ утатора 3 и первую группу входов блока 6 сравнения В соответствии с .этим кодом коммутатор 3 пропускает на входы регистра 1 код одного из логических условий, подаваемых на группы 5 входных ший устройства синхронизации. Код, выработанный коммутатором 3,

является кодом, определяющим следующее состояние устройства, и запоминается регистром 1 в момент прихода сигнала синхронизации по входу 7 и в случае отличия этого кода от кода на выходе регистра 2. Изменение состояния на выходе регистра

1приводит, в свою очередь, к выработке коммутатором 4 следующего состояния регистра 2, в которое он переключается в момент прихода сигнала по входу 8 и т.д. В случае равенства кодов на выходах регистра

2и коммутатора 3 блок 6 сравнения выдает на управляющий вход регистра 1 сигнал, запрещающий .изменение его состояния и в котором он находится до тех пор, пока коды на входах схемы; сравнения остаются одинаковыми.

Выход из режима ожидания осущестляется в направлении, определяемом логическими условиями на входных шинах коммутатора 3. Изменение логических условий приводит к изменению кода на выходе коммутатора 3 и к изменению сигнала на управляющем ;входе.регистра 1. С приходом синх;росигнала по входу 7 регистр 1 изменит свое состояние и т.д. Условием выхода из режима ожидания является отличие кодов на входах блока сравнентля. Формирование логических условий выхода из режима ожидания и задания следующего Состояния устройства осуществляется, например, попараметру времени (таймеру),. количеству тактов задакяцего генератора, по результатам вьшолн ния какой.либо асинхронной операции и т.д.

Наличие сигнала с выхода блока на входе 12 позволяет устройству управления, в составе которого работает устройство синхронизации, вести дополнительный контроль режима ожидания. По нему можно начинать формиров а ть п араметры време ни, количество тактов, начать асинхронную операцию и т.д. Одновременной смены логических условий на входах двух блоков коммутации быть не может, так как каждый предыдущий такт, четный или нечетный, изменяя условия.

подготагливает последующий, нечетный или четный.

Описанный порядок работы предлагаемого устройства синхронизации одинаково верен для любого кода и позволяет, в отличие от прототипа . использовать все коды для организации режима ожидания. Кроме того, нулевой код также является рабочим состоянием..

Такое включение блока сравнения в устройство обеспечивает также аппаратный контроль за режимом разделения временных состояний на выходах обоих регистров {аппаратный контроль и

обеспечение режима разделения време- ни по каналам синхронизации). Практическим примером такой работы ус.тройства для синхронизации может быть синхронизация работы двух устройств с одним (например, работа двух контроллеров на одну магистраль, на одно ОЗУ и т.д.) и обеспечение режима разделения времени. В предлагаемом устройстве синхронизация работы двух устройств задается состояниями с выходов первого и второго регистров, а их взаимодействие с общим устройством синхронизируется одинаковыми состояниями. При этом режим разделения времени обеспечивается автоматически, поскольку появление одинаковых состояний на выходе регистров невозможно. ДоЯолнительйый эффект эаключаетс1я в исключении значительной части оборудования, предназначенного для

взаимных блокировок, и согласовании работы устройств во времени.

Таким образом, предлагаемое устройство для синхронизации по сравнению с известным позволяет с помощью введенного блока сравнения использовать все состояния регистров как рабочие,-все коды для организации режима ожидания, организовать

(вести) аппаратный контроль режима .разделения времени на выходах регистров. Тем самым обеспечиваются расширение функциональных возможностей устройства синхронизации при организации режима ожидания и повЕлиение его надежности.

// S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации | 1985 |

|

SU1251055A1 |

| Устройство микропрограммного управления | 1983 |

|

SU1151961A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Распределенная система для программного управления с мажоритированием | 1990 |

|

SU1727112A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1221655A1 |

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ, содержащее два регистра, два коммутато а, причем выходы первого и второго коммутаторов соединены соответственно с информационными входами первого и второго регистров, группа выходов первого регистра является первой группой выходов фазовой синхронизации устройства и соединена соответственно с группой управляющих входов второго коммутатора, группа информащюнных входов которого является первой группой входов сигналов логического уело-. ВИЯ устройства, вторая группа входов сигналов логического условия устройства соединена соответственно с группой.информационных входов первого коммутатора, группа управляющих входов первого коммутатора соединена с группой выходов второго регистра и является второй группой выходов фазовой синхронизации устройства, первый и второй ходы фазовой синхронизации устройства соединены соответственно с синхровходами первого и второго регистров, вход разрешения следующего состояния -устройства соединен с управляющим входом второго регистра, о тличающееся тем, что, с целью повьвыения надежности, в него введен блок сравнения, первая и (Л вторая группы входов которого соединены с группой выходов первого и второго регистров соответственно, выход блока сравнения соединен с управляющим входом первого регистра и является контрольным выходом режима ожидания устройства.

Авторы

Даты

1983-04-30—Публикация

1981-12-11—Подача