Изобретение относится к автоматике и вычислительной технике и может быть использовано в распределенных отказоустойчивых системах АСУ ТП (системах управления сложными взаимодействующими технологическими объектами, системах станков с ИЛУ и др,), использующих программный принцип управления, построенных по модульному принципу и допускающих наращивание структуры при расширении числа выполняемых функций.

Цель изобретения - повышение надежности функционирования модуля.

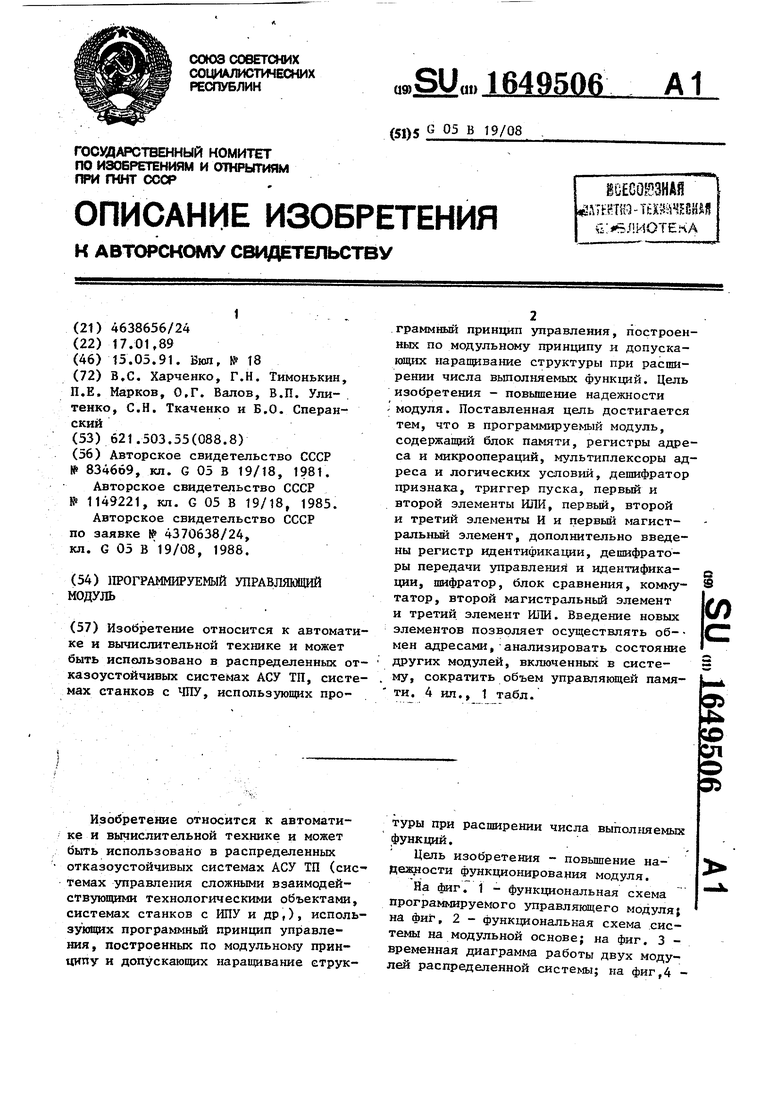

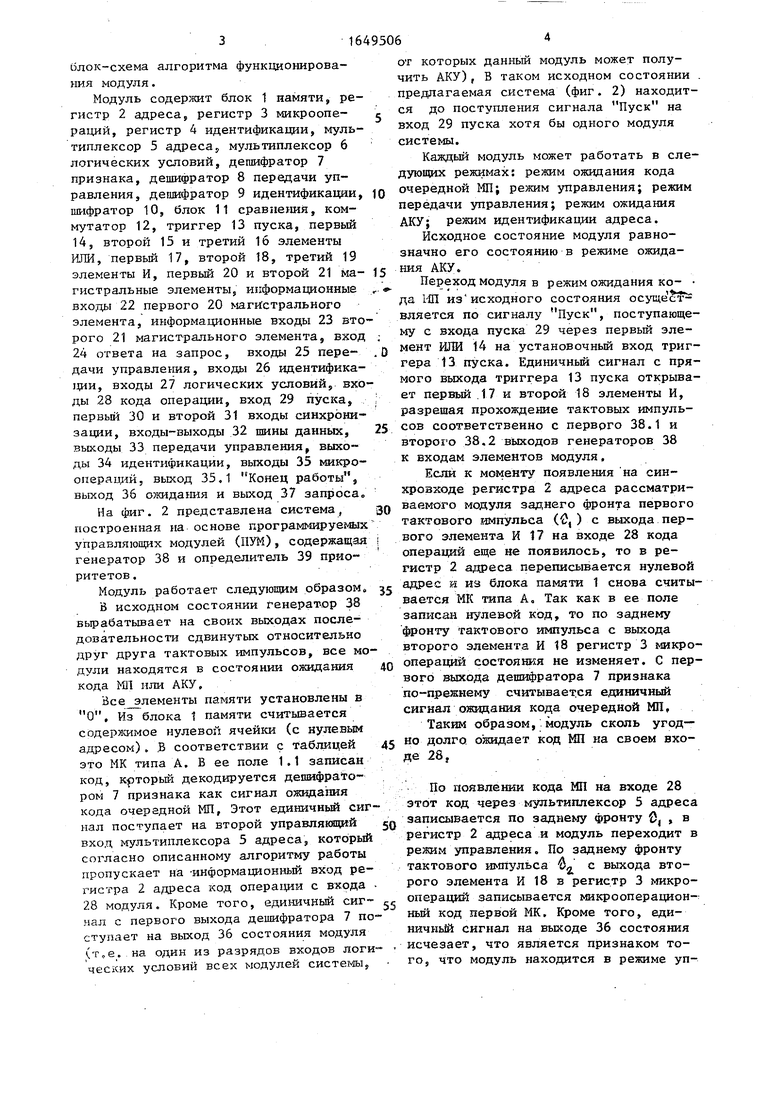

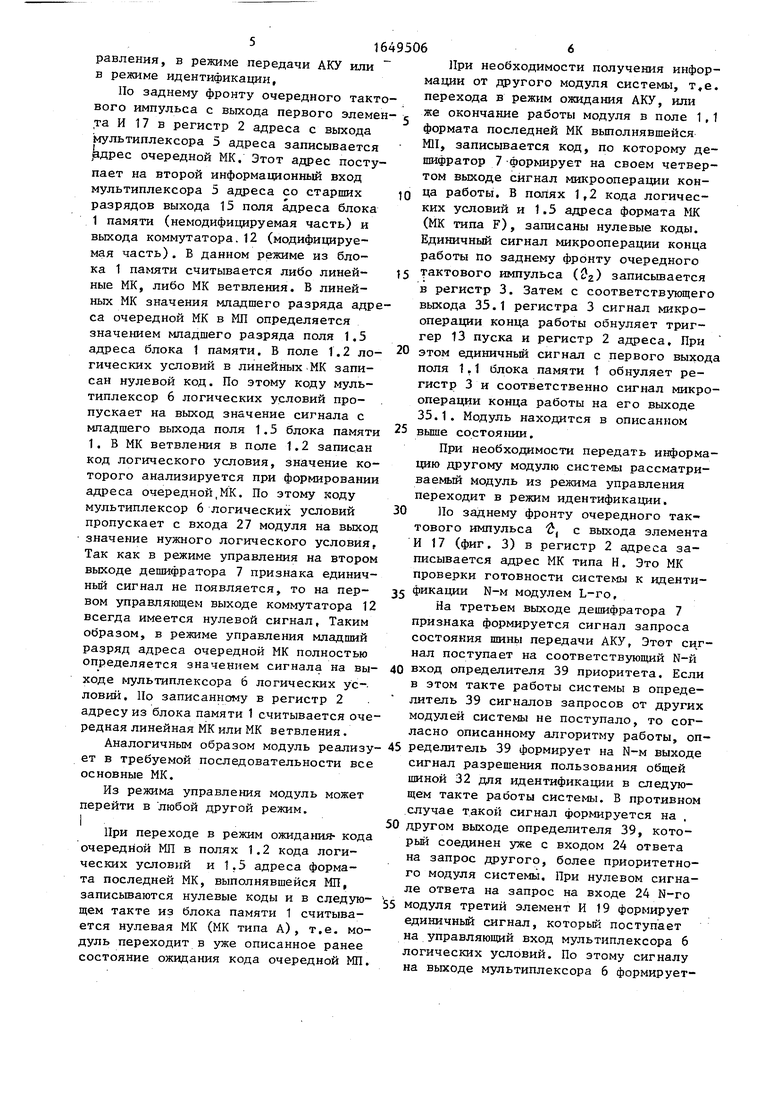

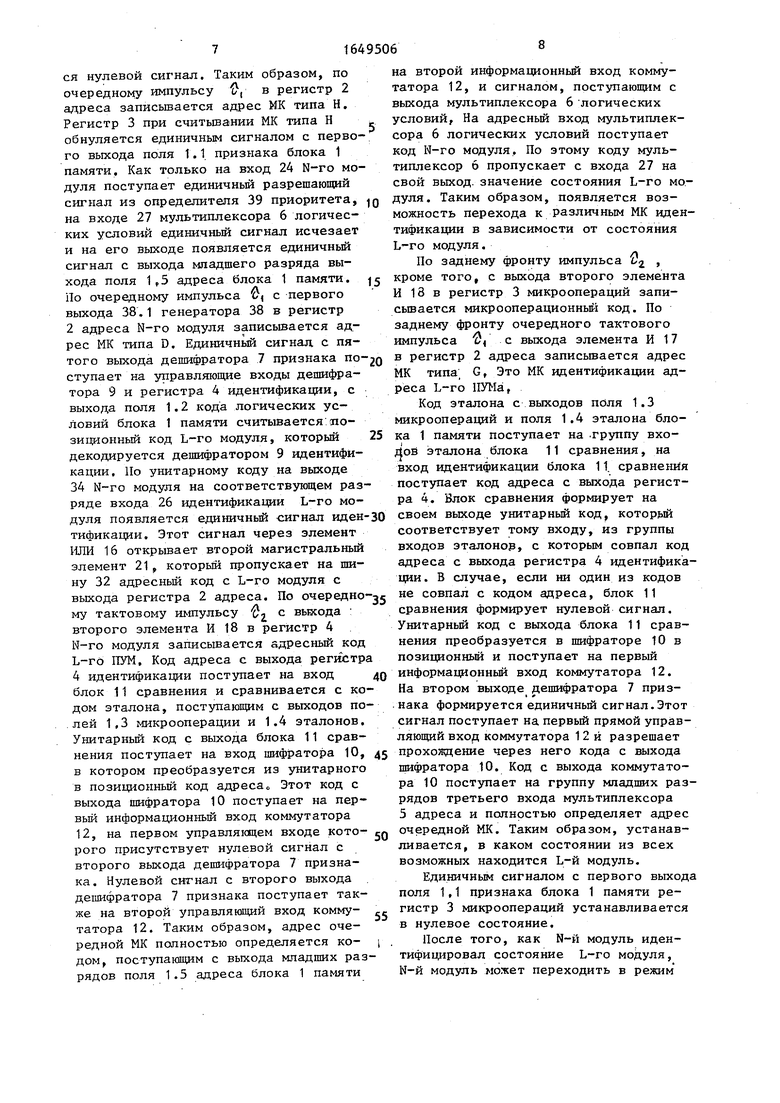

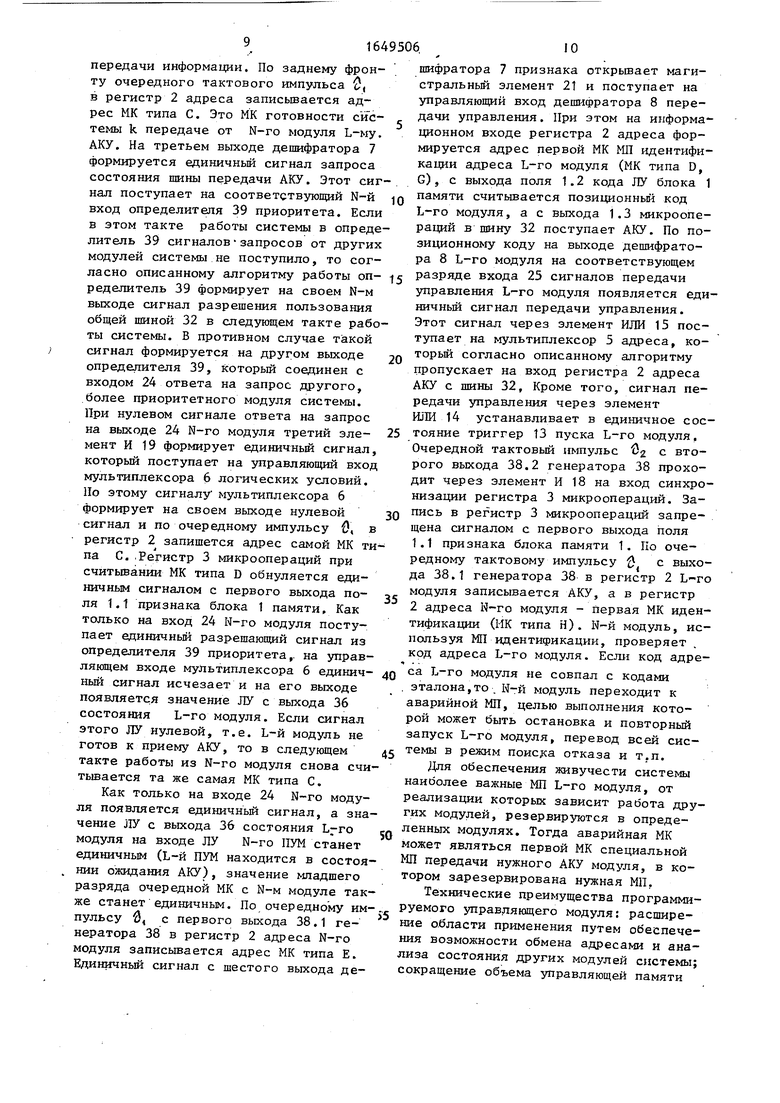

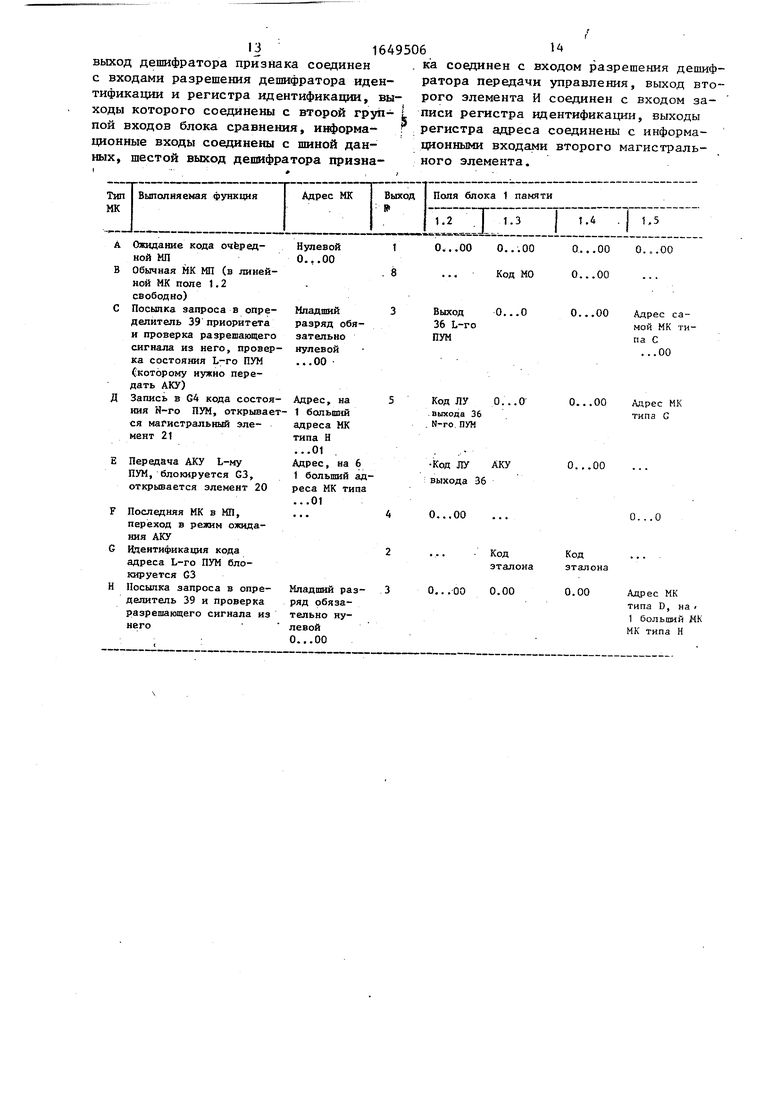

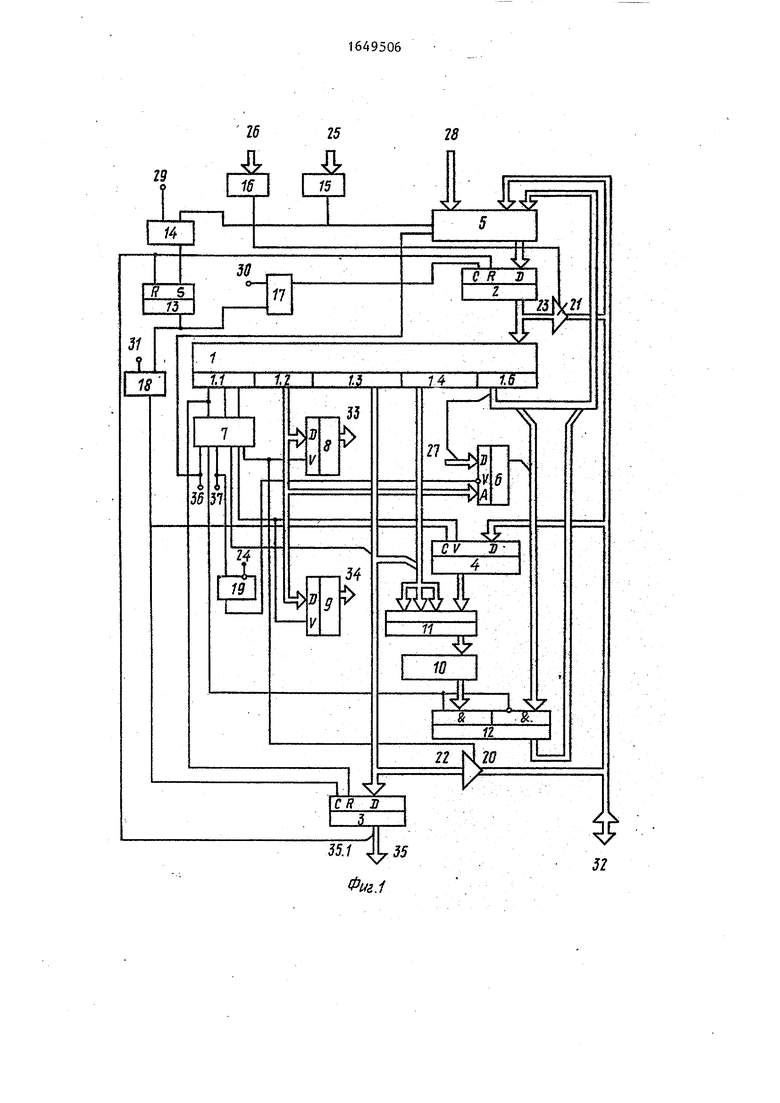

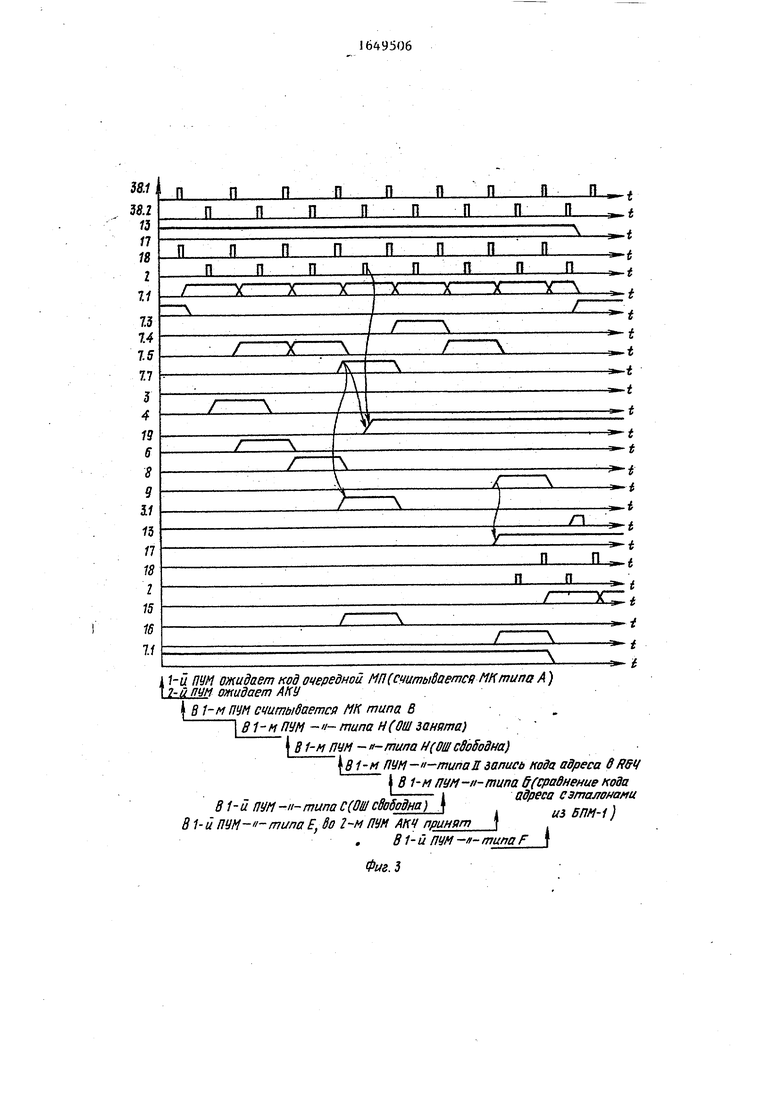

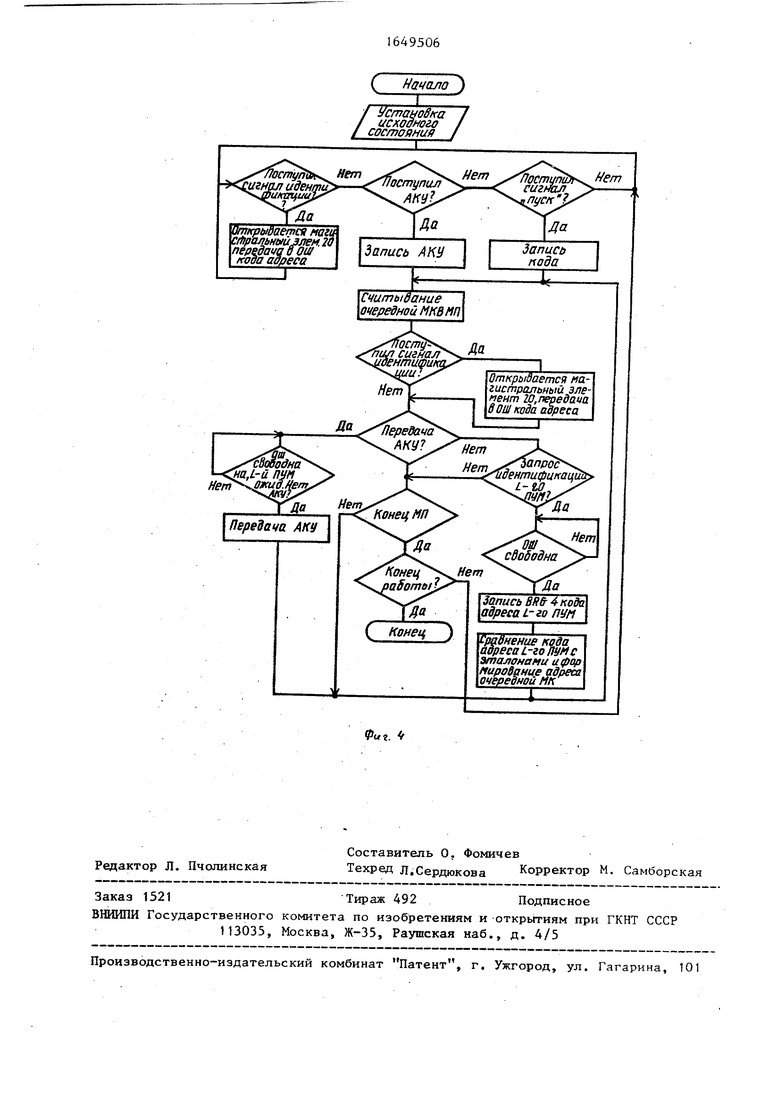

На фиг. 1 - функциональная схема программируемого управляющего модуля; на фиг, 2 - функциональная схема системы на модульной основе; на фиг. 3 - временная диаграмма работы двух модулей распределенной системы; на фиг,4 блок-схема алгоритма функционирования модуля.

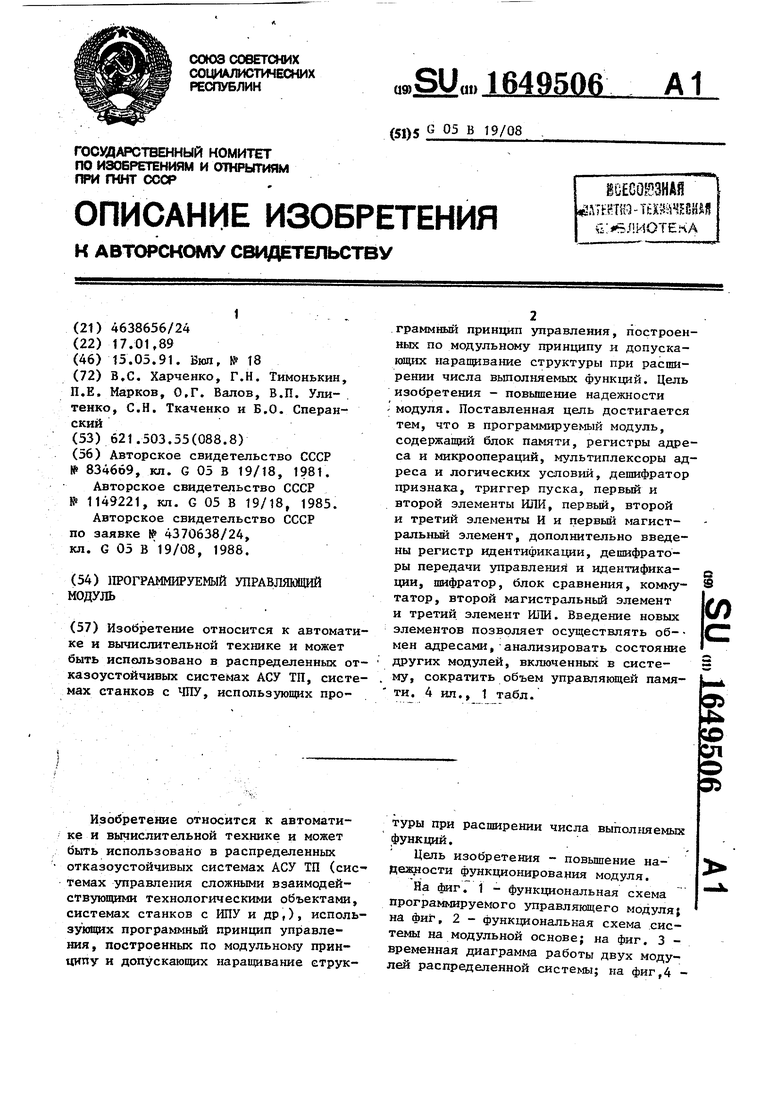

Модуль содержит блок 1 памяти, регистр 2 адреса, регистр 3 микроопе- раций, регистр 4 идентификации, мультиплексор 5 адреса, мультиплексор 6 логических условий, дешифратор 7 признака, дешифратор 8 передачи управления, дешифратор 9 идентификации, шифратор 10, блок 11 сравнения, коммутатор 12, триггер 13 пуска, первый 14, второй 15 и третий 16 элементы ИЛИ, первый 17, второй 18, третий 19 элементы И, первый 20 и второй 21 ма- гистральные элементы, информационные входы 22 первого 20 магистрального элемента, информационные входы 23 второго 21 магистрального элемента, вход 24 ответа на запрос, входы 25 пере- дачи управления, входы 26 идентификации, входы 27 логических условий, входы 28 кода операции, вход 29 пуска, первый 30 и второй 31 входы синхронизации, входы-выходы 32 шины данных, выходы 33 передачи управления, выходы 34 идентификации, выходы 35 микроопераций, выход 35.1 Конец работы 9 выход 36 ожидания и выход 37 запроса.

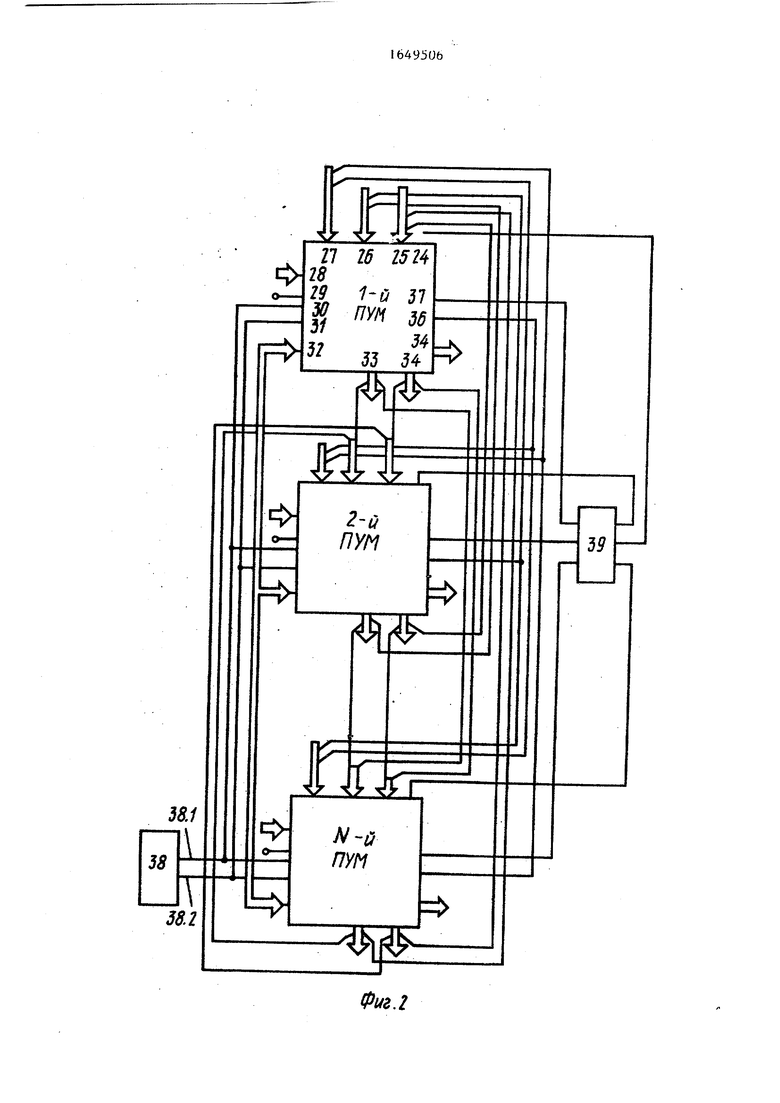

На фиг. 2 представлена система, построенная на основе программируемых управляющих модулей (ПУМ), содержащая генератор 38 и определитель 39 прио ритетов.

Модуль работает следующим образом. В исходном состоянии генерат-ор 38 вырабатывает на своих выходах последовательности сдвинутых относительно друг друга тактовых импульсов, все модули находятся в состоянии ожидания кода МП или АКУ,

Все элементы памяти установлены в О. Из блока 1 памяти считывается содержимое нулевой ячейки (с нулевым адресом). В соответствии с таблицей это МК типа А. В ее поле 1.1 записан код, который декодируется дешифратором 7 признака как сигнал ожидания кода очередной МП, Этот единичный сигнал поступает на второй управляющий вход мультиплексора 5 адреса, который согласно описанному алгоритму работы пропускает на -информационный вход регистра 2 адреса код операции с входа 28 модуля. Кроме того, единичный сиг- чад с первого выхода дешифратора 7 поступает на выход 36 состояния модуля (т.е. на один из разрядов входов логи условий всех модулей системы.

от которых данный модуль может получить АКУ), В таком исходном состоянии предлагаемая система (фиг. 2) находится до поступления сигнала Пуск на вход 29 пуска хотя бы одного модуля системы.

Каждый модуль может работать в следующих режимах: режим ожидания кода очередной МП; режим управления; режим передачи управления; режим ожидания АКУ; режим идентификации адреса.

Исходное состояние модуля равнозначно его состоянию в режиме ожидания АКУ.

Переход модуля в режим ожидания ко- да МП из исходного состояния осуще ст вляется по сигналу Пуск, поступающему с входа пуска 29 через первый элемент ИЛИ 14 на установочный вход триггера 13 пуска. Единичный сигнал с прямого выхода триггера 13 пуска открывает первый 17 и второй 18 элементы И, разрешая прохождение тактовых импульсов соответственно с перврго 38.1 и второго 38.2 выходов генераторов 38 к входам элементов модуля,

Если к моменту появления на син- хровходе регистра 2 адреса рассматриваемого модуля заднего фронта первого тактового импульса (Ј, ) с выхода первого элемента И 17 на входе 28 кода операций еще не появилось, то в регистр 2 адреса переписывается нулевой адрес и из блока памяти 1 снова считывается МК типа А. Так как в ее поле записан нулевой код, то по заднему фронту тактового импульса с выхода второго элемента И 18 регистр 3 микроопераций состояния не изменяет. С первого выхода дешифратора 7 признака по-прежнему считывается единичный сигнал ожидания кода очередной МП,

Таким образом, модуль сколь угодно долго ожидает код МП на своем входе 28,

По появлении кода МП на входе 28 этот код через мультиплексор 5 адреса записывается по заднему фронту 0( , в регистр 2 адреса и модуль переходит в режим управления. По заднему фронту тактового импульса $г с выхода второго элемента И 18 в регистр 3 микроопераций записывается микрооперационный код первой МК. Кроме того, единичный сигнал на выходе 36 состояния исчезает, что является признаком того, что модуль находится в режиме управления, в режиме передачи АКУ или в режиме идентификации,

По заднему фронту очередного тактового импульса с выхода первого элемента И 17 в регистр 2 адреса с выхода мультиплексора 5 адреса записывается рдрес очередной МК. Этот адрес поступает на второй информационный вход мультиплексора 5 адреса со старших разрядов выхода 15 поля адреса блока 1 памяти (немодифицируемая часть) и выхода коммутатора.12 (модифицируемая часть) . В данном режиме из блока 1 памяти считывается либо линейные МК, либо МК ветвления. В линейных МК значения младшего разряда адреса очередной МК в МП определяется значением младшего разряда поля 1.5 адреса блока 1 памяти. В поле 1.2 логических условий в линейных МК записан нулевой код. По этому коду мультиплексор 6 логических условий пропускает на выход значение сигнала с младшего выхода поля 1.5 блока памяти 1. В МК ветвления в поле 1.2 записан код логического условия, значение которого анализируется при формировании адреса очередной,МК. По этому коду мультиплексор 6 логических условий пропускает с входа 27 модуля на выход значение нужного логического условия, Так как в режиме управления на втором выходе дешифратора 7 признака единичный сигнал не появляется, то на первом управляющем выходе коммутатора 12 всегда имеется нулевой сигнал, Таким образом, в режиме управления младший разряд адреса очередной МК полностью

При необходимости получения информации от другого модуля системы, т.е. перехода в режим ожидания АКУ, или же окончание работы модуля в поле 1,1 формата последней МК выполнявшейся Mil, записывается код, по которому дешифратор 7 формирует на своем четвертом выходе сигнал микрооперации конца работы. В полях 1,2 кода логических условий и 1.5 адреса формата МК (МК типа F), записаны нулевые коды. Единичный сигнал микрооперации конца работы по заднему фронту очередного

тактового импульса (а) записывается в регистр 3. Затем с соответствующего выхода 35.1 регистра 3 сигнал микрооперации конца работы обнуляет триггер 13 пуска и регистр 2 адреса. При

0 этом единичный сигнал с первого выхода поля 1.1 блока памяти 1 обнуляет регистр 3 и соответственно сигнал микрооперации конца работы на его выходе 35.1. Модуль находится в описанном выше состоянии.

При необходимости передать информацию другому модулю системы рассматриваемый модуль из режима управления переходит в режим идентификации.

0 По заднему фронту очередного тактового импульса Ј, с выхода элемента И 17 (фиг, 3) в регистр 2 адреса записывается адрес МК типа Н. Это МК проверки готовности системы к иденти5 фикации N-м модулем L-ro,

На третьем выходе дешифратора 7 признака формируется сигнал запроса состояния шины передачи АКУ, Этот сигнал поступает на соответствующий N-й

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в распределенных отказоустойчивых системах АСУ ТП, системах станков с ЧПУ, использующих программный принцип управления, построенных по модульному принципу и допускающих наращивание структуры при расширении числа выполняемых функций. Цель изобретения - повышение надежности модуля. Поставленная цель достигается тем, что в программируемый модуль, содержащий блок памяти, регистры адреса и микроопераций, мультиплексоры адреса и логических условии, дешифратор признака, триггер пуска, первый и второй элементы ИЛИ, первый, второй и третий элементы И и первый магистральный элемент, дополнительно введены регистр идентификации, дешифраторы передачи управления и идентификации, шифратор, блок сравнения, коммутатор, второй магистральный элемент и третий элемент ИЛИ. Введение новых элементов позволяет осуществлять об- мен адресами, анализировать состояние других модулей, включенных в систему, сократить объем управляющей памяти. 4 ил., 1 табл. (Я о Јь СО У1

определяется значением сигнала на вы- 40 вход определителя 39 приоритета. Если ходе мультиплексора 6 логических ус- в этом такте работы системы в опреде- ловий. Но записанному в регистр 2 литель 39 сигналов запросов от других адресу из блока памяти 1 считывается оче- модулей системы не поступало, то сог- редная линейная МК или МК ветвления. ласно описанному алгоритму работы, оп- Аналогичным образом модуль реализу- 45 ределитель 39 формирует на N-м выходе

сигнал разрешения пользования общей шиной 32 для идентификации в следующем такте работы системы. В противном случае такой сигнал формируется на . 50 другом выходе определителя 39, который соединен уже с входом 24 ответа на запрос другого, более приоритетного модуля системы. При нулевом сигнале ответа на запрос на входе 24 N-ro записываются нулевые коды и в следую- 55 модуля треТий элемент И 19 формирует щем такте из блока памяти 1 считыва- единичный сигнал, который поступает

на управляющий вход мультиплексора 6 логических условий. По этому сигналу на выходе мультиплексора 6 формируетет в требуемой последовательности все основные МК.

Из режима управления модуль может перейти в любой другой режим.

I

При переходе в режим ожидания- кода

очередной МП в полях 1.2 кода логических условий и 1.5 адреса формата последней МК, выполнявшейся МП,

ется нулевая МК (МК типа А), т.е. модуль переходит в уже описанное ранее состояние ожидания кода очередной МП.

ся нулевой сигнал. Таким образом, по очередному импульсу Ј, в регистр 2 адреса записывается адрес МК типа Н. Регистр 3 при считывании МК типа Н обнуляется единичным сигналом с первого выхода поля 1.1 признака блока 1 памяти. Как только на вход 24 N-ro модуля поступает единичный разрешающий сигнал из определителя 39 приоритета, на входе 27 мультиплексора 6 логических условий единичный сигнал исчезает и на его выходе появляется единичный сигнал с выхода младшего разряда выхода поля 1,5 адреса блока 1 памяти. По очередному импульса v{ с первого выхода 38.1 генератора 38 в регистр 2 адреса N-ro модуля записывается адрес МК типа D. Единичный сигнал, с пятого выхода дешифратора 7 признака поступает на управляющие входы дешифратора 9 и регистра 4 идентификации, с выхода поля 1.2 кода логических условий блока 1 памяти считывается позиционный код L-ro модуля, который декодируется дешифратором 9 идентификации. По унитарному коду на выходе 34 N-ro модуля на соответствующем разряде входа 26 идентификации L-ro модуля появляется единичный сигнал идентификации. Этот сигнал через элемент ИЛИ 16 открывает второй магистральный элемент 21, который пропускает на шину 32 адресный код с L-ro модуля с выхода регистра 2 адреса. По очередно му тактовому импульсу с выхода второго элемента И 18 в регистр 4 N-ro модуля записывается адресный код L-ro ПУМ, Код адреса с выхода регистр 4 идентификации поступает на вход блок 11 сравнения и сравнивается с кодом эталона, поступающим с выходов полей 1,3 микрооперации и 1.4 эталонов. Унитарный код с выхода блока 11 сравнения поступает на вход шифратора 10, в котором преобразуется из унитарного в позиционный код адреса,, Этот код с выхода шифратора 10 поступает на первый информационный вход коммутатора 12, на первом управляющем входе кото- рого присутствует нулевой сигнал с второго выхода дешифратора 7 признака. Нулевой сигнал с второго выхода дешифратора 7 признака поступает также на второй управляющий вход комму- татора 12. Таким образом, адрес очередной МК полностью определяется ко- дом, поступающим с выхода младших разрядов поля 1.5 адреса блока 1 памяти

на второй информационный вход коммутатора 12, и сигналом, поступающим с выхода мультиплексора 6 логических условий, На адресньй вход мультиплексора 6 логических условий поступает код N-ro модуля. По этому коду мультиплексор 6 пропускает с входа 27 на свой выход, значение состояния L-ro модуля. Таким образом, появляется возможность перехода к различным МК идентификации в зависимости от состояния L-ro модуля.

По заднему фронту импульса ьг , кроме того, с выхода второго элемента И 18 в регистр 3 микроопераций записывается микрооперационньй код. По заднему фронту очередного тактового импульса Ј с выхода элемента И 17 в регистр 2 адреса записывается адрес МК типа, G, Это МК идентификации адреса L-ro ПУМа,

Код эталона с выходов поля 1.3 микроопераций и поля 1.4 эталона блока 1 памяти поступает на .группу входов эталона блока 11 сравнения, на вход идентификации блока 11. сравнения поступает код адреса с выхода регистра 4. Блок сравнения формирует на своем выходе унитарный код, который соответствует тому входу, из группы входов эталонор, с которым совпал код адреса с выхода регистра 4 идентификации. В случае, если ни один из кодов не совпал с кодом адреса, блок 11 сравнения формирует нулевой сигнал. Унитарный код с выхода блока 11 сравнения преобразуется в шифраторе 10 в позиционный и поступает на первый информационный вход коммутатора 12. На втором выходе дешифратора 7 призi

нака формируется единичный сигнал.Этот сигнал поступает на первый прямой управляющий вход коммутатора 1 2 и разрешает прохождение через него кода с выхода шифратора 10. Код с выхода коммутатора 10 поступает на группу младших разрядов третьего входа мультиплексора 5 адреса и полностью определяет адрес очередной МК. Таким образом, устанавливается, в каком состоянии из всех возможных находится L-й модуль.

Единичным сигналом с первого выход поля 1,1 признака блока 1 памяти регистр 3 микроопераций устанавливается в нулевое состояние.

После того, как N-й модуль идентифицировал состояние L-ro модуля, N-й модуль может переходить в режим

передачи информации. По заднему фронту очередного тактового импульса ь{ в регистр 2 адреса записывается адрес МК типа С. Это МК готовности сие- темы k передаче от N-го модуля L-му. АКУ. На третьем выходе дешифратора 7 Формируется единичный сигнал запроса состояния шины передачи АКУ. Этот сигнал поступает на соответствующий N-й JQ вход определителя 39 приоритета. Если в этом такте работы системы в определитель 39 сигналовзапросов от других модулей системы не поступило, то согшифратора 7 признака открывает маг стральный элемент 21 и поступает н управляющий вход дешифратора 8 пер дачи управления. При этом на инфор ционном входе регистра 2 адреса фо мируется адрес первой МК МП идентиф кации адреса L-ro модуля (МК типа G), с выхода поля 1.2 кода ЛУ блока памяти считывается позиционный код L-ro модуля, а с выхода 1.3 микрооп раций в шину 32 поступает АКУ. По зиционному коду на выходе дешифрат ра 8 L-ro модуля на соответствующем

ласно описанному алгоритму работы оп- $ разряде входа 25 сигналов передачи

20

25

30

35

ределитель 39 формирует на своем М-м выходе сигнал разрешения пользования общей шиной 32 в следующем такте работы системы. В противном случае такой сигнал формируется на другом выходе определителя 39, который соединен с входом 24 ответа на запрос другого, более приоритетного модуля системы. При нулевом сигнале ответа на запрос на выходе 24 N-ro модуля третий элемент И 19 формирует единичный сигнал, который поступает на управляющий вход мультиплексора 6 логических условий. Но этому сигналу мультиплексора 6 формирует на своем выходе нулевой сигнал и по очередному импульсу О, в регистр 2 запишется адрес самой МК типа С. Регистр 3 микроопераций при считывании МК типа D обнуляется единичным сигналом с первого выхода поля 1.1 признака блока 1 памяти. Как только на вход 24 Ы-го модуля поступает единичный разрешающий сигнал из определителя 39 приоритета, на управляющем входе мультиплексора 6 единичный сигнал исчезает и на его выходе появляется значение ЛУ с выхода 36 состояния L-ro модуля. Если сигнал этого ЛУ нулевой, т.е. L-й модуль не готов к приему АКУ, то в следующем такте работы из N-ro модуля снова считывается та же самая МК типа С.

Как только на входе 24 N-ro модуля появляется единичный сигнал, а значение ЛУ с выхода 36 состояния L-ro модуля на входе ЛУ N-ro ПУМ станет единичным (L-й ПУМ находится в состоянии ожидания АКУ), значение младшего разряда очередной МК с N-м модуле также станет единичным. По очередному им-.,. пульсу $, с первого выхода 38.1 ге- нератора 38 в регистр 2 адреса N-ro модуля записывается адрес МК типа Е. Единичный сигнал с шестого выхода де40

45

50

управления L-ro модуля появляется ничный сигнал передачи управления. Этот сигнал через элемент ИЛИ 15 п тупает на мультиплексор 5 адреса, торый согласно описанному алгоритму пропускает на вход регистра 2 адрес АКУ с шины 32, Кроме того, сигнал п редачи управления через элемент ИЛИ 14 устанавливает в единичное с тояние триггер 13 пуска L-ro модуля Очередной тактовый импульс QZ с вт рого выхода 38.2 генератора 38 прох дит через элемент И 18 на вход синх низации регистра 3 микроопераций. З пись в регистр 3 микроопераций запр щена сигналом с первого выхода поля 1.1 признака блока памяти 1. По оче редному тактовому импульсу Ј с вы да 38.1 генератора 38 в регистр 2 L модуля записывается АКУ, а в регист 2 адреса Ы-го модуля - первая МК ид тификации (ИК типа Н). N-й модуль, пользуя МП идентификации, проверяет

код адреса L-ro модуля. Если код ад ч

са L-ro модуля не совпал с кодами эталона,то. N-й модуль переходит к аварийной МП, целью выполнения кото рой может быть остановка и повторны запуск L-ro модуля, перевод всей си темы в режим поиска отказа и т.п.

Для обеспечения живучести систем наиболее важные МП L-ro модуля, от реализации которых зависит работа д гих модулей, резервируются в опреде ленных модулях. Тогда аварийная МК может являться первой МК специально МЛ передачи нужного АКУ модуля, в к тором зарезервирована нужная МП.

Технические преимущества програм руемого управляющего модуля: расшир ние области применения путем обеспе ния возможности обмена адресами и а лиза состояния других модулей систе сокращение объема управляющей памят

506

JQ10

шифратора 7 признака открывает магистральный элемент 21 и поступает на управляющий вход дешифратора 8 передачи управления. При этом на информационном входе регистра 2 адреса формируется адрес первой МК МП идентификации адреса L-ro модуля (МК типа D, G), с выхода поля 1.2 кода ЛУ блока 1 памяти считывается позиционный код L-ro модуля, а с выхода 1.3 микроопераций в шину 32 поступает АКУ. По позиционному коду на выходе дешифратора 8 L-ro модуля на соответствующем

$ разряде входа 25 сигналов передачи

0

5

0

5

.

0

5

управления L-ro модуля появляется единичный сигнал передачи управления. Этот сигнал через элемент ИЛИ 15 поступает на мультиплексор 5 адреса, который согласно описанному алгоритму пропускает на вход регистра 2 адреса АКУ с шины 32, Кроме того, сигнал передачи управления через элемент ИЛИ 14 устанавливает в единичное состояние триггер 13 пуска L-ro модуля. Очередной тактовый импульс QZ с второго выхода 38.2 генератора 38 проходит через элемент И 18 на вход синхронизации регистра 3 микроопераций. Запись в регистр 3 микроопераций запрещена сигналом с первого выхода поля 1.1 признака блока памяти 1. По очередному тактовому импульсу Ј с выхода 38.1 генератора 38 в регистр 2 LTO модуля записывается АКУ, а в регистр 2 адреса Ы-го модуля - первая МК идентификации (ИК типа Н). N-й модуль, используя МП идентификации, проверяет ,

код адреса L-ro модуля. Если код адре- ч

са L-ro модуля не совпал с кодами эталона,то. N-й модуль переходит к аварийной МП, целью выполнения которой может быть остановка и повторный запуск L-ro модуля, перевод всей системы в режим поиска отказа и т.п.

Для обеспечения живучести системы наиболее важные МП L-ro модуля, от реализации которых зависит работа других модулей, резервируются в определенных модулях. Тогда аварийная МК может являться первой МК специальной МЛ передачи нужного АКУ модуля, в котором зарезервирована нужная МП.

Технические преимущества программируемого управляющего модуля: расширение области применения путем обеспечения возможности обмена адресами и анализа состояния других модулей системы; сокращение объема управляющей памяти

11

й повышения на этой основе надежности

системы.

Формула изобре тения

Программируемый управляющий модуль, содержащий блок памяти, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, дешифратор признака, триггер пуска, первый и второй элементы ИЛИ, первый, второй и третий элементы И и первый магистральный элемент, информационные выхо, 1649506-12

ловий блока памяти соединены с адресными входами мультиплексора логических условии, выходы кода микроопераций соединены с входами старших разрядов группы информационных входов регистра микроопераций и первого магистрально| го элемента, младший разряд поля адреса и входы логических условий мульЮ типлексора логических условий являются информационными входами мультиплексора логических условий, выходы старших разрядов группы выходов поля адреса блока памяти соединены с входами

являются входами второго элемента ИЛИ, выход которого соединен с вторым

ды которого соединены с шиной данных,, старших разрядов третьей группы инфор- вход пуска модуля является первым мационных входов мультиплексора адре- входом первого элемента ИЛИ, выход ко- Са, входы передачи управления модуля торого соединен с входом установки триггера пуска, выход которого соединен с первыми входами первого и второ- 20 входом первого элемента ИЛИ и первым го элементов И, вторые входы которых адресным входом мультиплексора адре- являются соответственно первым и вто- са, отличающийся тем, что, рым входами синхронизации модуля, а с целью повышения надежности функцио- выходы соединены соответственно с вхо- нирования модуля, в него дополнитель- дами записи регистров микроопераций и 25 но введены регистр идентификации, дешифраторы передачи управления и идентификации, шифратор, блок сравнения, коммутатор, второй магистральный элемент и третий элемент ИЛИ, входы кото- 30 рого являются входами идентификации, а выход соединен с входом управления

адреса, выходы которого соединены с адресными входами блока памяти, выходы поля признака которого соединены с входами дешифратора признака, первый выход которого является выходом ожидания модуля и соединен с вторым адресным входом мультиплексора адреса, выходы которого соединены с информационными входа ми регистра адреса, а первая и вторая группы информационных входов соединены соответственно с входами хода операций и шиной данных, выход старшего разряда группы выходов поля признака блока памяти

второго1 магистрального элемента, выходы которого соединены с шиной данных, входы-выходы которой являются ин- 35 формационными входами-выходами модуля,

выходы кода логических условий блока памяти соединены с информационными входами дешифратора передачи управления и идентификации, выходы которых явля- соединен с входом сброса регистра мик- Q ются соответственно выходами передачи роопераций, выходы которого являются управления и идентификации модуля, выходами микроопераций модуля, а вы- четвертый выход дешифратора признака, ход Конец работы соединен с входа- выходы кода микроопераций и кода эта- ми сброса триггера пуска и регистра лонов блока памяти-являются первой адреса, третий выход дешифратора приз-д5 группой входов блока сравнения, выхо- нака является выходом запроса и соеди- ды которого соединены с входами шифра- нен с первым входом третьего элемен- тора, выходы которого соединены с пер- та И, второй инверсный вход которого вой группой информационных входов ком- является входом ответа на запрос, а мутатора, выходы которого соединены с выход соединен с инверсным входом раз- 50 входами младших разрядов третьей трупрешения мультиплексора логических условий, четвертый выход дешифратора признака соединен с выходом младшего разряда группы информационных входов регистра микроопераций и первого магистрального элемента, шестой выход дешифратора признака является управляющим входом первого магистрального элемента, выходы поля логических усявляются входами второго элемента ИЛИ, выход которого соединен с вторым

старших разрядов третьей группы инфор- мационных входов мультиплексора адре- Са, входы передачи управления модуля входом первого элемента ИЛИ и первым адресным входом мультиплексора адре- са, отличающийся тем, что, с целью повышения надежности функцио- нирования модуля, в него дополнитель- но введены регистр идентификации, дешифраторы передачи управления и идентификации, шифратор, блок сравнения, коммутатор, второй магистральный элемент и третий элемент ИЛИ, входы кото- рого являются входами идентификации, а выход соединен с входом управления

второго1 магистрального элемента, выходы которого соединены с шиной данных, входы-выходы которой являются ин- 35 формационными входами-выходами модуля,

выходы кода логических условий блока памяти соединены с информационными входами дешифратора передачи управления и идентификации, выходы которых явля- Q ются соответственно выходами передачи управления и идентификации модуля, четвертый выход дешифратора признака, выходы кода микроопераций и кода эта- лонов блока памяти-являются первой д5 группой входов блока сравнения, выхо- ды которого соединены с входами шифра- тора, выходы которого соединены с пер- вой группой информационных входов ком- мутатора, выходы которого соединены с 50 входами младших разрядов третьей труп5ы информационных входов мультиплексора адреса, выход мультиплексора ло- гических условий и выходы младших разрядов группы выходов поля адреса бло- ка памяти являются второй группой ин- формационных входов коммутатора, второй выход дешифратора признака соединен с первым и вторым инверсными входами управления коммутатора, пятый

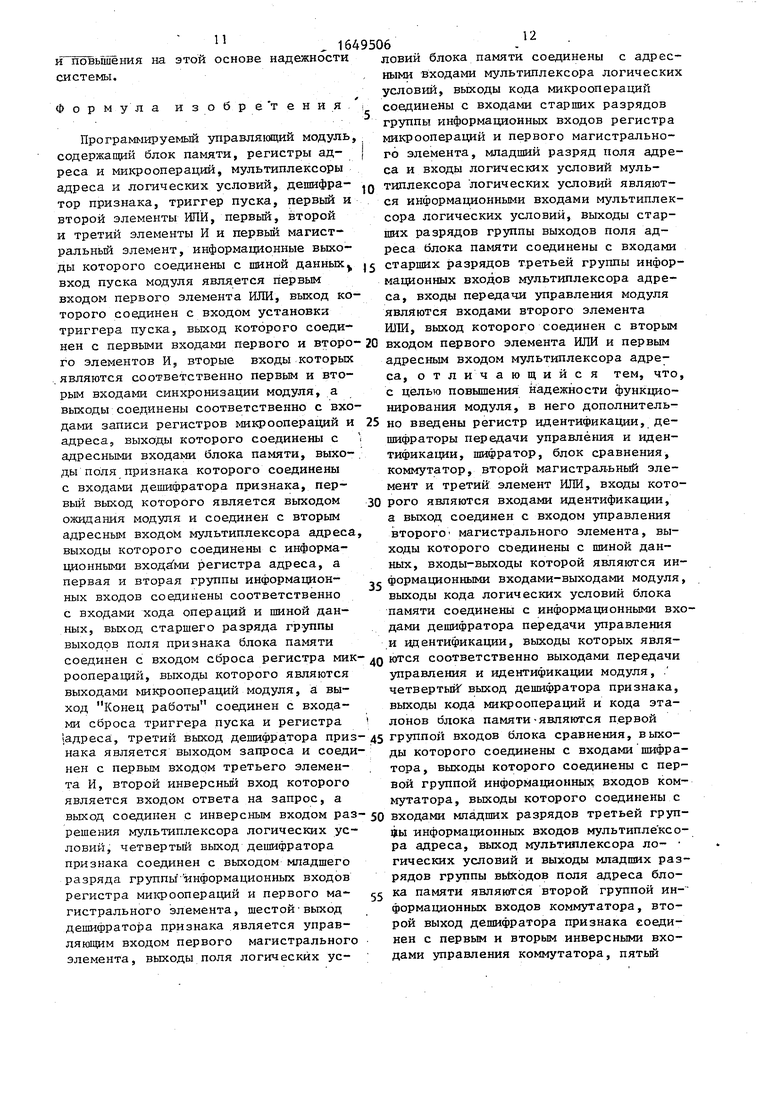

выход дешифратора признака соединен с входами разрешения дешифратора идентификации и регистра идентификации, выходы которого соединены с второй труп- I пой входов блока сравнения, информа- цнонные входы соединены с шиной данных, шестой выход дешифратора признаТип

мк

Выполняемая функция

Ожидание кода очередной МП

Обычная МК МП (в линейной МК поле 1.2 свободно)

Посыпка запроса в определитель 39 приоритета и проверка разрешающего сигнала из него, проверка состояния L-ro ПУМ (которому нужно передать АКУ)

Запись в G4 кода состояния N-ro ПУМ, открываеся магистральный элемент 21

Передача АКУ L-му ПУМ, блокируется G3, открывается элемент 20

Последняя МК в МП, переход в режим ожидания АКУ

Идентификация кода адреса L-ro ПУМ блокируется G3

Посылка запроса в определитель 39 и проверка разрешающего сигнала из него

ка соединен с входом разрешения дешифратора передачи управления, выход второго элемента И соединен с входом записи регистра идентификации, выходы регистра адреса соединены с информационными входами второго магистрального элемента.

0...00

Адрес самой МК типа С ...00

0...О

0...00

Адрес МК типа G

0...00

0...0

Код эталона

. ..00 0.00

Код эталона

0.00

Адрес МК типа D, на 1 больший МК МК типа Н

25

28

f

6Ј

Щ

4У

mi O-N

э

/УР

1

1

/W

W

DJ

И

2W

И

A/XZ/

-г

J О

и

«

z z и

kjJ

з

и

л:

16

16 11

1-й ПУМ ожидает код очередной МП (считывается ПК типа А) 2-и ПУМ ожидает АКУ

В 1-м пум считывается МК типа В

81-м ПУМ - ч- типа Н (ОШ занята)

В 1-н ПУМ - ч-типа Н(ОШ сМодна)

В1-м ПУМ-ч-типа Ж запись кода адреса ffftfftf

В 1-м ПУН-н-типа&(сраднениекоЗа

04 ,„,„ л 71-Tiадреса С эталонами

В 1-й ПУМ -и-типа С(ОВ/ свободна) зкпм1

В1- и ПУН- -типа Е, So 2-м ПУМ АКЧ принят и

. В 1-й ПУМ -я-типаF

Фиг. 5

П

JL

П

wBaenw магц

Э1/ИУ

передаvgвOiff

сгйральныизлем. 20 предана 8 Оь ffoaa адреса

J

Нет

С Начало)

/Установка 7 исходного / состояния /

Нет

Запись АКУ

С

Считывание очередной МКВНП

Открывается магистральный элемент 20,передача в ОШ кода адреса

| Устройство для автоматического раз-гОНА и ТОРМОжЕНия дВигАТЕля CTAHKA СпРОгРАММНыМ упРАВлЕНиЕМ | 1975 |

|

SU834669A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для автоматического разгона и торможения двигателя станка с программным управлением | 1983 |

|

SU1149221A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР по заявке 4370638/24, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-05-15—Публикация

1989-01-17—Подача