Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании самоконтролируемых микропроцессорных систем и микро-ЭВМ.

Цель изобретения - повьшение достоверности контроля.

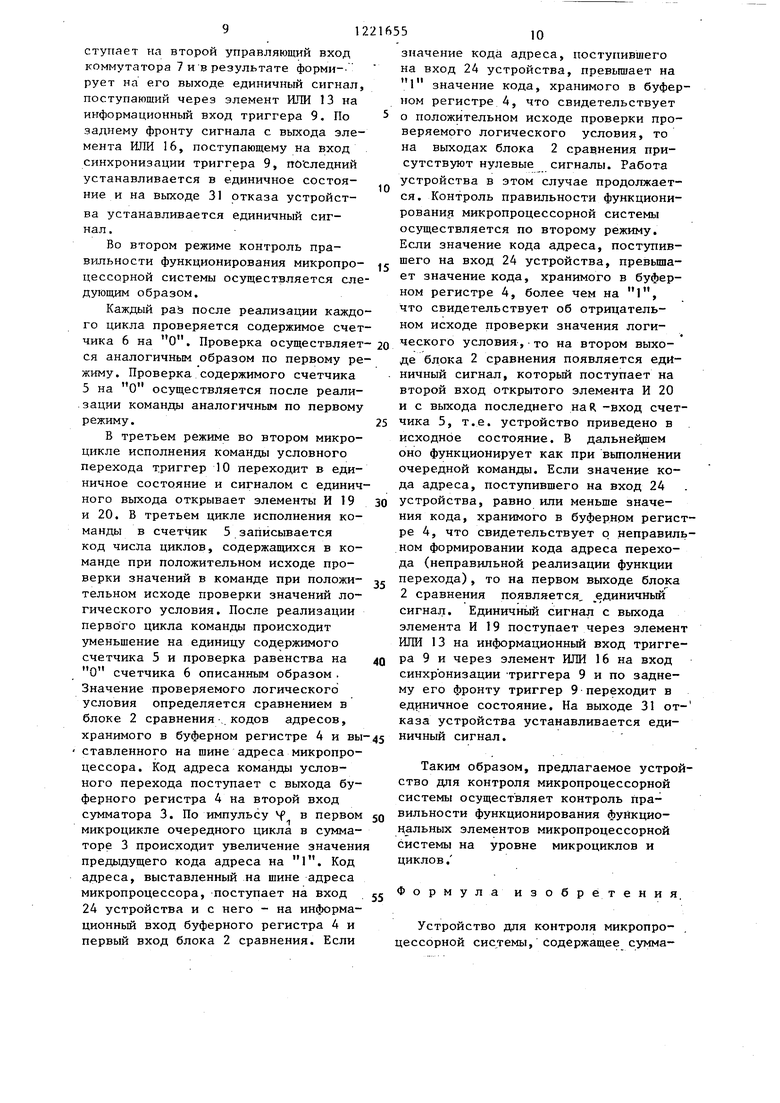

На фиг.1 изображена функциональная схема устройства для контроля микропроцессорной системы; на фиг.2 и 3 - временные диаграммы работы устройства.

Устройство (фиг.о содержит преобразователь 1 кода команды в код числа циклов и микроциклов, блок 2 сравнения, сумматор 3, буферный регистр 4, второй счетчик 5, первый счетчик 6, коммутатор 7, второй триггер 8, третий триггер 9, первый триггер 10, третий элемент ИЛИ 11, второй элемент ИЛИ-12, четвертый элемен ИЛИ 13, третий элемент И 14, четвер- тый элемент И 15, первый элемент ИЛИ 16, пятый элемент И 17, элемент НЕ 18, первый элемент И 19, второй элемент И 20, группу входов 21 кода состояния контролируемого микропроцессора устройства, группу входов 22 синхронизации устройства, группу управляющих входов 23 устройства, груп пу входов 24 адреса устройства, вход

25устройства соединен с выходом разрешения ввода микропроцессора, вход

26устройства соединен с выходом ожидания микропроцессора, вход 27 признака работы устройства соединен с , выходом захвата контролируемого микропроцессора, первый тактовый вход 28 и второй тактовый вход 29 устройства входят в группу входов 22 синхро

низации и соединены с- входами М и контролируемого микропроцессора, вход 30 устройства соединен с выходом синхронизации контролируемого микропроцессора. Выход 31 отказа устройства.

На фиг.2 и 3 обозначены: 5 - содержимое счетчика 5; 6 - содержимое счетчика 6; 8 - значение сигнала на единичном выходе триггера 8; 9 - значение сигнала на единичном выходе триггера 9; 10 - значение сигнала на единичном выходе триггера 10; 19- выходной сигнал элемента И 19; 21 - сигнал на входе 21 данных устройства; 24 - сигнал на входе адреса устройства; 25 - сигнал на входе четвертого разряда группы управляющих хо

0

0

5

дов 23 устройства; 26 - сигнал на входе первого разряда группы управляющих входов 23 устройства; 27 - сигнал на вкоде второго разряда группы управляющих входов 23 устройства;

28- сигнал на втором входе группы входов 22 синхронизации устройства;

29- сигнал на первом входе группы входов синхронизации устройства;

30- сигнал на входе третьего разряда группы управляющих входов 23 уст-- ройства.

Назначение функциональных элементов и связей устройства для контроля микропроцессорной системы следующее.

Преобразователь 1 кода команды в код числа циклов и микроциклов предназначен для определения по коду слова состояния процессора соответст- . вующего ему числа микроциклов в цикле команды и по коду командь - количества циклов в команде. Блок 2 сравнения предназначен для организации сравнения кодов адресов, выставляемых на шине адрес:а микропроцессора в каждом цикле реализации команды. Сумматор 3 - для организации естественного способа формирования адресов ячеек памяти внешних устройств микропроцессорной системы. Буферный регистр 4 - для записи и хранения кодов адре сов,

, по которым осуществляется обра-

щение к внешнш устройствам микропроцессорной системы. Второй счетчик 5- дяя осуществления счета числа реализованных в команде циклов. Счетчик 6 - для осуществления счета числа

0 реализованных в цикле микроциклов. Коммутатор 7 - для формирования сигнала результата проверки исходного состояния счетчиков 5 и 6 в каждом цикле реализации команды микропроцес5 .сора Триггер 8 - для запоминания

факта перехода микропроцессора к циклу выборки кода команды с внещнего устройства. Триггер 9 - для формирования сигнала отказа (сбоя) объекта

0 контроля. Триггер 10 - для запоминания факта реализации микропроцессором команды условного перехода. Элемент ИЛИ 11 - для формирования сигнала управления коммутатором 7 и

5 разрешения формирования сигнала синхронизации для счетчика 5. Элемент ИЛИ 12 - для формирования импульсов счета для счетчика 5. Элемент ИЛИ

13 - для передачи сигнала отказа i (сбоя) на информационный вход триггера 9, Элемент И 14 - для формирова ния сигналов синхронизации счетчика. 5 и установки в О триггера 8. Элемент И 15 предназначен для формиро-, вания импульсов счета для счетчика 6

Элемент ИЛИ 16 - для передачи сигналов синхронизации на соответствующий вход триггера 9, Элемент И 17 - для формирования сигналов управления коммутатором 7 и сигналов синхронизации счетчика 6 и триггера 10. Элемент НЕ 18 - для инвертирования сигнала, характеризующего тип реализуемой команды. Элемент И 19 - для формирования информационных сигналов и сигналов синхронизации для триггера 9. Элемент И 20 - для установки в о счетчика 5.

По входу 22 синхронизации устройства поступает последовательность импульсов синхронизации Ф и Ф , которая поступает на соответствуюпше входы синхронизации контролируемого микропроцессора.

На входы 25, 26, 27 и 30 группы входов 23 управления поступают сигналы соответственно отсутствия режима ожидания, запрета прямого обращения к памяти со стороны внешних устройств, признака того, что на шине данных находится слово состояния процессора и признака того, что шина данных находится в режиме ввода ин-- формации в микропроцессор.

Пример выполнения предлагаемого устройства (фиг.1) приведен для случая проверки правильности функционирования микропроцессорной системы, построенной на базе микропроцессоров типа К580, ИК-30, INTEL 8080 или других аналогичных.

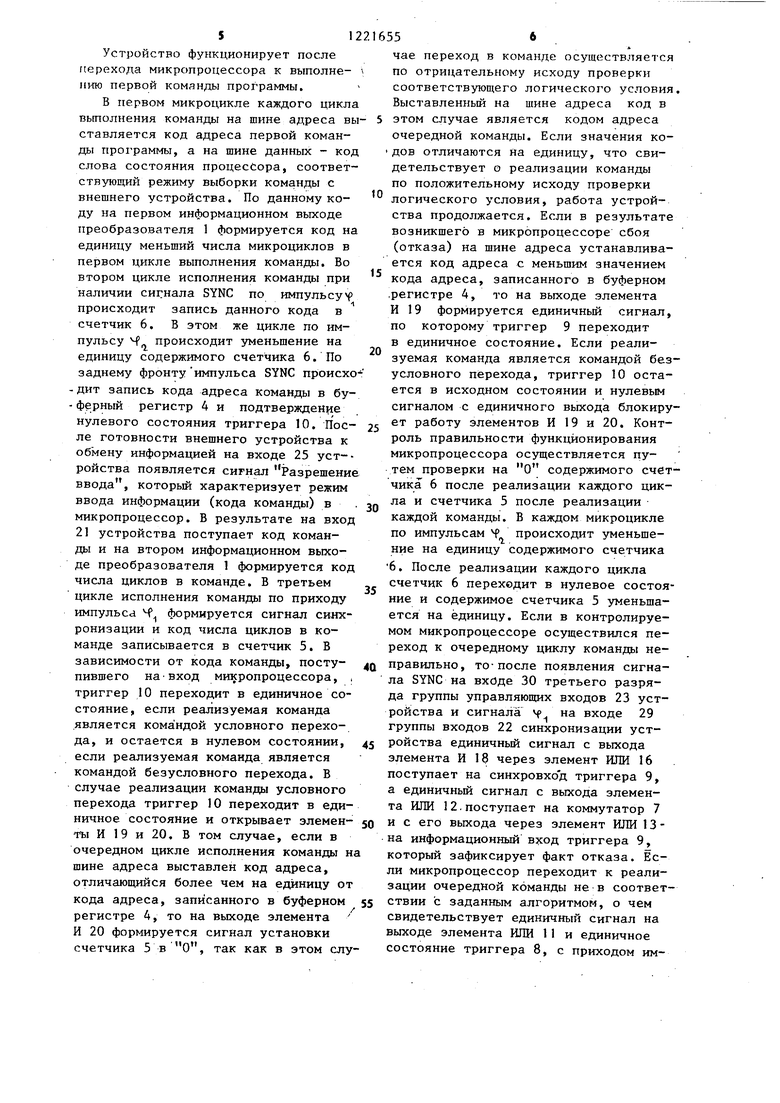

Преобразователь 1 является комбинационной схемой, его структура и работа определена таблицей истинности

Вход 21

Выходы

01001001

0101 001

01001110

0100 010

продолжение таблицы

5

5

Как видно из таблицы, единичное значение сигнал на втором управляющем выходе преобразователя 1 принимает в цикле выборки команда (в первом цикле). Единичное значение сигнал на первом управляющем выходе преобразователя 1 принимает также в первом цикле команды после счи- тьгоания кода команды условного пе- . рехода.

В предлагаемом устройстье контроль правильности функционирования микропроцессорной системы осуществляется следующим образом.

Устройство функционирует после Г1ерехода микропроцессора к выполне- ПИЮ первой команды программы.

В первом микроцикле каждого цикла выполнения команды на шине адреса выставляется код адреса первой команды про1 раммы, а на шине данных - код слова состояния процессора, соответствующий режиму выборки команды с внешнего устройства. По данному коду на первом информационном выходе преобразователя 1 формируется код на единицу меньший числа микроциклов в первом цикле выполнения команды. Во втором цикле исполнения команды при

наличии сигнала SYNC происходит счетчик 6.

по импульсу

запись данного кода в В этом же цикле по импульсу М происходит уменьшение на

чае переход в команде осуществ. тяетс по отрицательному исходу проверки соответствующего логического услови Выставленный на шине адреса код в этом случае является кодом адреса очередной команды. Если значения ко дов отличаются на единицу, что свидетельствует о реализации команды по положительному исходу проверки логического условия, работа устройства продолжается. Если в результат возникшего в микропроцессоре сбоя (отказа) на шине адреса устанавлива ется код адреса с меньшим значением кода адреса, записанного в буферном .регистре 4, то на выходе элемента И 19 формируется единичный сигнал по которому триггер 9 переходит в единичное состояние. Если реализуемая команда является командой бе условного перехода, триггер 10 оста ется в исходном состоянии и нулевым сигналом с единичного выхода блокир ет работу элементов И 19 и 20. Конт роль правильности функционирования микропроцессора осуществляется путем проверки на О содержимого сче чика 6 после реализации каждого цик ла и счетчика 5 после реализации каждой команды. В каждом микроцикле

20

25

30

35

единицу содержимого счетчика 6. По заднему фронту импульса SYNC происхо-дит запись кода адреса команды в бу фарный регистр 4 и подтверждение нулевого состояния триггера 10. После готовности внешнего устройства к обмену информацией на входе 25 уст-- ройства появляется сигнал Разрешение ввода, который характеризует режим ввода информации (кода команды) в микропроцессор. В результате на вход 21 устройства поступает код команды и на втором информационном выходе преобразователя 1 формируется код числа циклов в команде. В третьем цикле исполнения команды по приходу импульса Ч формируется сигнал сиих- ронизации и код числа циклов в команде записывается в счетчик 5. В зависимости от кода команды, поступившего на ВХОД микропроцессора, , триггер 10 переходит в единичное состояние, если реализуемая команда является командой условного перехода, и остается в нулевом состоянии, если реализуемая команда является командой безусловного перехода. В случае реализации команды условного перехода триггер 10 переходит в единичное состояние и открывает элементы И 1 9 и 20 . В том случае, если в очередном цикле исполнения команды на шине адреса выставлен код адреса, отличающийся более чем на единицу от кода адреса, записанного в буферном §5 ствии с заданным алгоритмом, о чем

40

45

50

по импульсам f, происходит уменьшение на единицу содержимого счетчика 6. После реализации каждого цикла счетчик 6 переходит в нулевое состо ние и содержимое счетчика 5 уменьша ется на единицу. Если в контролируе мом микропроцессоре осуществился пе реход к очередному циклу команды не правильно, то-после появления сигна ла SYNC на входе 30 третьего разряда группы управляющих входов 23 уст ройства и сигнала Ч, на входе 29 группы входов 22 синхронизации устройства единичный сигнал с выхода элемента И 18 через элемент ИЛИ 16 поступает на синхровхо д триггера 9, а единичный сигнал с выхода элемента ИЛИ 12.поступает на коммутатор 7 и с его вьпсода через элемент ИЛИ 13 на информационный вход триггера 9, который зафиксирует факт отказа. Ес ли микропроцессор переходит к реали зации очередной команды не в соотве

регистре 4, то на выходе элемента И 20 формируется сигнал установки счетчика 5 в О, так как в этом слусвидетельствует единичный сигнал на выходе элемента ИЛИ 11 и единичное состояние триггера 8, с приходом им

10

16556

чае переход в команде осуществ. тяется по отрицательному исходу проверки соответствующего логического условия. Выставленный на шине адреса код в этом случае является кодом адреса очередной команды. Если значения кодов отличаются на единицу, что свидетельствует о реализации команды по положительному исходу проверки логического условия, работа устройства продолжается. Если в результате возникшего в микропроцессоре сбоя (отказа) на шине адреса устанавливается код адреса с меньшим значением кода адреса, записанного в буферном .регистре 4, то на выходе элемента И 19 формируется единичный сигнал, по которому триггер 9 переходит в единичное состояние. Если реализуемая команда является командой безусловного перехода, триггер 10 остается в исходном состоянии и нулевым сигналом с единичного выхода блокирует работу элементов И 19 и 20. Контроль правильности функционирования микропроцессора осуществляется путем проверки на О содержимого счетчика 6 после реализации каждого цикла и счетчика 5 после реализации каждой команды. В каждом микроцикле

15

20

25

30

§5 ствии с заданным алгоритмом, о чем

ствии с заданным алгоритмом, о чем

по импульсам f, происходит уменьшение на единицу содержимого счетчика 6. После реализации каждого цикла счетчик 6 переходит в нулевое состояние и содержимое счетчика 5 уменьшается на единицу. Если в контролируемом микропроцессоре осуществился переход к очередному циклу команды неправильно, то-после появления сигнала SYNC на входе 30 третьего разряда группы управляющих входов 23 устройства и сигнала Ч, на входе 29 группы входов 22 синхронизации устройства единичный сигнал с выхода элемента И 18 через элемент ИЛИ 16 поступает на синхровхо д триггера 9, а единичный сигнал с выхода элемента ИЛИ 12.поступает на коммутатор 7 и с его вьпсода через элемент ИЛИ 13 - на информационный вход триггера 9, который зафиксирует факт отказа. Если микропроцессор переходит к реализации очередной команды не в соответсвидетельствует единичный сигнал на выходе элемента ИЛИ 11 и единичное состояние триггера 8, с приходом импульсов / , и SYNC триггер 9 переходит в единичное состояние и зафиксируется факт отказа.

Предлагаемое устройство для контроля микропроцессорной системы работает в синхронном режиме с контролируемым микропроцессором (входы установки режима работы устройства не показаны).

В исходном состоянии все элементь1 памяти находятся в нулевом состоянии (сходы установки в О не показаны).

Рассмотрим работу npeAnaraeh:oro устройства на примере реализации команды, содержащей один цикл реализации команды безусловного перехода, содержащей более одного цикла и реализации команды условного перехода.

Пример.(Первый режим). В первом микроцикле первого цикла на вход 21 данных поступает код слова состояния процессора (для микропроцессора указанного типа это код цикла выборки команды FETCH). В результате на первом информационном выходе преобразователя 1 появляется код числа микроциклов в данном цикле, а на первом управляющем его выходе появляется единичный сигнал, который переводит триггер 8 в единичное состояние. На входе 24 адреса устройства появляется код адреса команды, который поступает ла информационный вход буферного регистра 4 и первый вход бло блока 2 сравнения. В случае отсутствия режима Ожидание и режима Захват на входы 26 и 27 устройства поступает единичный и нулевой сигналы соответственно и открывают элемент И 15. Во втором микроцикле (после прихода сигнала SYNC на вход 30 устройства) по импульсу У на выходе элемента И 17 формируется единичный сигнал, который поступает на вход синхронизации счетчика 6, в .который записывается код числа микроциклов в первом цикле, уменьшенный на 1, а по импульсу у в данном цикле происходит уменьшение содержимого счетчика 6 на 1. После готовности внешних устройств к обмену информацией . с микропроцессором на входе 25 устройства появляется единичный сигнал, который свидетельствует о переводе шины данных микропроцессора в режим ввода информации. В третьем микроцикле на вход 21 устройства поступает код считанной

команды. На втором информационном выходе преобразователя 1 появляется код числа циклов в команде, а на

втором управляющем его выходе - ну- левой сигнал. По импульсу ч в третьем микроцикл е на выходе элемента И 14 формируется единичный, сигнал, , который поступает на вход синхронизации счетчика 3 и в него записывается код числа циклов в команде.

Этим же сигналом происходит установка триггера 8 ь нулевое состояние. В последнем микроцикле цикла команды по. импульсу Ч происходит установка в О счетчика 6. В результате отрицательным фронтом сигнала на выходе элемента ИЛИ 12 счетчик 5 переходит в нулевое состояние. В случае

неправильного функционирования контролируемого устройства (перед началом реализации очередного цикла команды счетчик 6 не устанавливается в О) во втором.цикле очередной команды перед записью новой информации в счетчик 6 по импульсу на выходе элемента И 17 формируется единичный сигнал, который поступает на второй управляющий вход коммутатора 7 на

второй информационный вход которого поступает единичньш сигнал с выхода элемента ИЛИ 12. Единичный сигнал с выхода коммутатора 7 поступает на первый вход элемента ИЛИ 13 и с его выхода на информационный вход триггера 9. По заданному фронту импульса синхронизации с выхода элемента И 17, поступающему через элемент ИЛИ 16 на вход синхронизации триггера 9, происходит установка в единичное состояние триггера 9 и на выходе 31 устройства формируется сигнал отказа (сбоя). Если по отрицательному фронту сигнала с выхода

элемента ИЛИ 12 счетчик 5 не устанавливается в О, то единичный сигнал

с вьпгода элемента ИЛИ 11 поступает на первый информационный вход коммутатора 7. В первом цикле очередной

команды после установки на шине данных кода слова состояния процессора триггер 8 переходит в единичное состояние и сигнал с его единичного выхода поступает на первый управляющий вход коммутатора 7. Во втором микроцикле по импульсу на выходе пятого элемента И 17 формируется единичный сигнал, который по

ступает па второй управляющий вход коммутатора 7 и в результате формн-- рует на его выходе единичный сигнал, поступающий через элемент ИЛИ 13 на информационный вход триггера 9, По заднему фронту сигнала с выхода элемента ИЛИ 16, поступающему на вход синхронизации триггера 9, гто следний устанавливается в единичное состояние и на выходе 31 отказа устройства устанавливается единичный сигнал .

Во втором режиме контроль правильности функционирования микропроцессорной системы осуществляется следующим образом.

Каждый pas после реализации каждого цикла проверяется содержимое счетчика 6 на О, Проверка осуществляет ся аналогичным образом по первому режиму. Проверка содержимого счетчика 5 на о осуществляется после реали- .зации команды аналогичным по первому режиму.

В третьем режиме во втором микроцикле исполнения команды условного перехода триггер 10 переходит в единичное состояние и сигналом с единичного выхода открывает элементы И 19 и 20. В третьем цикле исполнения команды в счетчик 5 записывается код числа циклов, содержащихся в команде при положительном исходе проверки значений в команде при положительном исходе проверки значений логического условия. После реализации первого цикла команды происходит уменьшение на единицу содержимого счетчика 5 и проверка равенства на О счетчика 6 описанным образом . Значение проверяемого логического условия определяется сравнением в блоке 2 сравнения .. кодов адресов, хранимого в буферном регистре 4 и вы ставленного на шине адреса микропроцессора. Код адреса команды условного перехода поступает с выхода буферного регистра 4 на второй вход сумматора 3. По импульсу f в первом микроцикле очередного цикла в сумматоре 3 происходит увеличение значени предыдущего кода адреса на 1. Код адреса, выставленный на шине адреса микропроцессора, поступает на вход 24 устройства и с него - на информа- ционньш вход буферного регистра 4 и первый вход блока 2 сравнения. Если

10

15

20 5

О 5 0 5

5

0

значение кода адреса, поступившего на вход 24 устройства, превышает на 1 значение кода, хранимого в буферном регистре 4, что свидетельствует о положительном исходе проверки проверяемого логического условия, то на выходах блока 2 сравнения присутствуют нулевые сигналы. Работа устройства в этом случае продолжается. Контроль правильности функционирования микропроцессорной системы осуществляется по второму режиму. Если значение кода адреса, поступившего на вход 24 устройства, превьш1а- ет значение кода, хранимого в буферном регистре 4, более чем на 1, что свидетельствует об отрицательном исходе проверки значения логи

ческого условия,то на втором выходе блока 2 сравнения появляется единичный сигнал, который поступает на второй вход открытого элемента И 20 и с выхода последнего HaR -вход счетчика 5, т.е. устройство приведено в исходное состояние. В дальне щем оно функционирует как при вьшолнении очередной команды. Если значение кода адреса, поступившего на вход 24 устройства, равно или меньше значения кода, хранимого в буферном регистре 4, что свидетельствует о неправильном формировании кода адреса перехода (неправильной реализации функции перехода), то на первом выходе блока 2 сравнения появляется, единичный сигнал. Единичный сигнал с выхода элемента И 19 поступает через элемент ИЛИ 13 на информационный вход триггера 9 и через элемент ИЛИ 16 на вход синхронизации триггера 9 и по заднему его фронту триггер 9переходит в единичное состояние. На выходе 31 от- каза устройства устанавливается единичный сигнал.

Таким образом, предлагаемое устройство для контроля микропроцессорной системы осуществляет контроль правильности функционирования фуйкцио- нальных элементов микропроцессорной системы на уровне микроциклов и циклов.

Формула изобретения.

Устройство для контроля микропроцессорной системы, содержащее сумма11

тор, первый, второй и третий триггеры первый, второй и третий элементы ИЛИ, первый, второй, третий, четвертый и пятый элементы И, элемент НЕ1 и первый счетчик, причем единичный выход первого триггера соединен с ;первыми входами первого и второго элементов И, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход третьего элемента И соединен с входом установки О второго триггера, информационные выходы первого счетчика соединены с входами второго элемента ИЛИ, отличающееся тем, -что, с целью повьпиения достоверности контроля, в устройство введены буферный регистр, преобразователь кода команды в код числа циклов и микроциклов, блок сравнения, второй счетчик коммутатор и четвертьш элемент ИЛИ, причем информационные выходы второго счетчика соединены с входами -.. третьего элемента ИЛИ, выход которого соединен с первым информационным входом коммутатора и инверсным входом третьего элемента И, выход которого соединен с тактовым входом второго счетчика, выходы кода числа микроциклов и циклов в ;команде преобразователя кода команды в код числа циклов и микроциклов соединены с информациодными входами первого и второго счетчиков соответственно, единичный выход второго триггера соединен с первым управляющим входом коммутатора, выход которого соединен с первым входом, четвертого элемента ИЛИ, выход второго элемента ИЛИ соединен со счетным входом второго счетчика и вторым информационным входом коммутатора, выход начала цикла контроля преобразователя кода команды в число циклов и микроциклов соединен с единичным входом второго триггера, выход начала цикла выборки преобразователя кода команды в число циклов и микроциклов соединен с D -входом первого триггера и через элемент НЕ - с К -входом

22165512

первого триггера, выходы контролируемой микропроцессорной системь разрешения ввода, ожидания, первого тактового признака, разрешения коит5: роля соединены соответственно с первым входом третьего элемента И, с первым и вторым прямыми и инверс- ным входами четвертого элемен- ,та И, выход которого соединен со

О счетным входом первого счетчика,

второй тактовый вход устройства соединен с вторым входом третьего элемента И, с тактовым входом сумматора и с первым входом пятого

5 .элемента И, выход которого соединен с тактовым входом первого счетчика, с вторым управляющим входом коммутатора и вторым входом первого элемента ИЛИ, выход синхрониза-

20 ции контролируемой микропроцессорной системы соединен с вторым входом пятого элемента И, с входом синхронизации буферного регистра, с тактовым входом первого триггера, адресный вход устройства соединен с первым информационным входом блока сравнения и с информационным входом буферного регистра, выход которого соединен с информационным входом . - сумматора, выход которого соединен с вторым информационным входом блока сравнения, выходы неравенства и равенства блока сравнения соединены с вторыми входами соответственно пер- 35 вого и второго элементов И, выход -. второго элемента И соединен с входом установки о второго счетчика, выход первого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с информационным входом третьего триггера, выход первого элемента ИЛИ соединен с тактовым входом третьего триггера, выход которого является выходом неисправности устройства, входы состояния устройства соединены с информационными входами пребразователя кода команды в код числа циклов и микроцик25

30

40

45

50

лов.

фиг 2

Редактор М,Воловик

Составитель И.Сигалов Техред Н.Бонкало

Заказ 1614/55 Тираж 671Подписное

BHifflnii Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

Корректор М.Самборская

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Устройство для контроля условных переходов микропроцессора | 1984 |

|

SU1238076A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство приоритета | 1990 |

|

SU1829033A1 |

| Устройство для обмена информацией | 1978 |

|

SU941978A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

Изобретение относится области цифровой вьгчислительной техники и может быть использовано при проектировании самоконтролирующих микропроцессорных систем. Целбю изобретения является повышение достоверности контроля путем обеспечения контроля правильности функционирования системы на уровне микроциклов и циклов. Поставленная цель достигается введением буферного регистра, преобразователя кода команды в код числа циклов и микроциклов, блока сравнения, второго счетчика, коммутатора и четвертого элемента ИЛИ. 3 ил, таблица. (Л К) а СП ел

| Коффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| М.: Мир, 1983, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-30—Публикация

1984-08-08—Подача