выбора адреса перехода дешифратора микрокоманд, а первьш и второй входы данных и управляющий вход коммутатора условия перехода подключены соответственно к входу условия пе1151961 рехода устройства, выходу адреса замещения блока памяти микрокоманд и выходу признака выбора перехода дешифратора микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1984 |

|

SU1239715A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287156A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1287154A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Микропрограммный процессор | 1978 |

|

SU744587A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр микрокоманд, блок памяти адресов возврата, дешифратор микрокоманд, реверсивный счетчик, два элемента И и элемент ИЛИ, первьй и второй входы и выход которого соединены соответственно с выходами первого и второго элементов И и тактовым входом реверсивного счетчика, вход управления счетом которого подклвэчен к выходу признака возврата дешифратора микрокоманд, первые йходы адреса чтения первой и второй групп и первый вход адреса записи блока памяти адресов возвра та соединены с выходом реверсивного счетчика, вторые входы адреса чтения первой и второй групп подключены соответственно к шине нулевого потенциала и выходу признака входа в подпрограмму дешифратора микрокоманд, первые входы первого и второго элементов И соединены с синхровхрдом устройства, вторые входы первого и второго элементов И подключены соответственно к выходу признака входа в подпрограмму и выходу признака возврата дешифратора микрокоманд, вход которого соединен с выходом кода управления блока памяти микрокоманд, а вход данных, синхровход и выход регистра микрокоманд подключены соответственно к операционному выходу блока памяти микрокоманд, синхровходу и операционному выходу устройства, о тлич ающее с я тем, что, с целью упрощения, оно содержит коммутатор адреса перехода, коммутатор условия перехода, две группы сумматоров по модулю два и элемент ИЛИ-НЕ, первый и второй входы и выход которого соединены соответственно с синхровходом устрой(Л ства, выходом признака возврата дешифратора микрокоманд и синхровходом блока памяти адресов возврата, вход данных, второй вход адреса записи, первый и второй выходы которого подключены соответственно к выходу коммутатора адреса перехода, ел выходу коммутатора условия перехода, первым входам сумматоров по модулю два первой и второй групп, со вторые входы которых соединены с Од выходом признака возврата дешифратора микрокоманд, выходы сумматоров по модулю два первой и второй групп подключены соответственно к первому и второму адресньм входам блока памяти микрокоманд, первый и второй входы данных и управляющий вход коммутатора адреса перехода соединены соответственно с входом внешнего адреса перехода устройства, выходом адресного полуслова блока памяти микрокоманд и выходом признака

Изобретение относится к вычислительной технике и может быть использовано при реализации различных уровней управления в процессорах.

Цель изобретения - упрощение путем использования логического способа формирования исполнительных адресов перехода и совмещения оборудования при организации различных видов перехода.

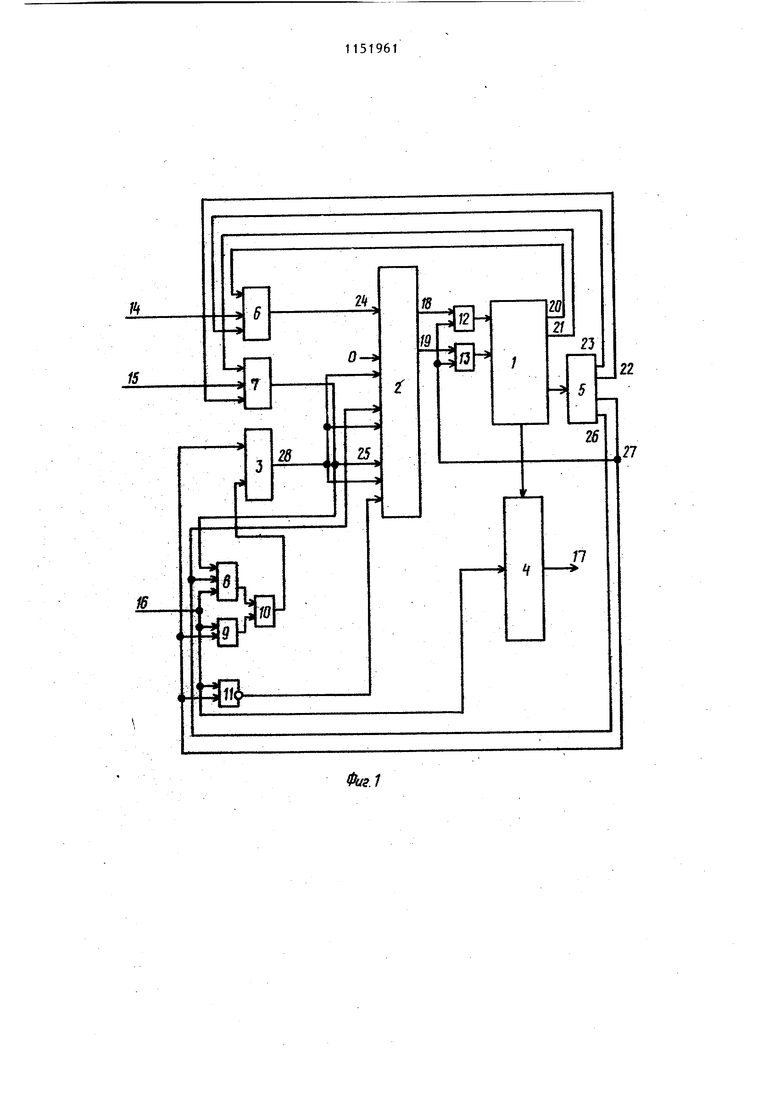

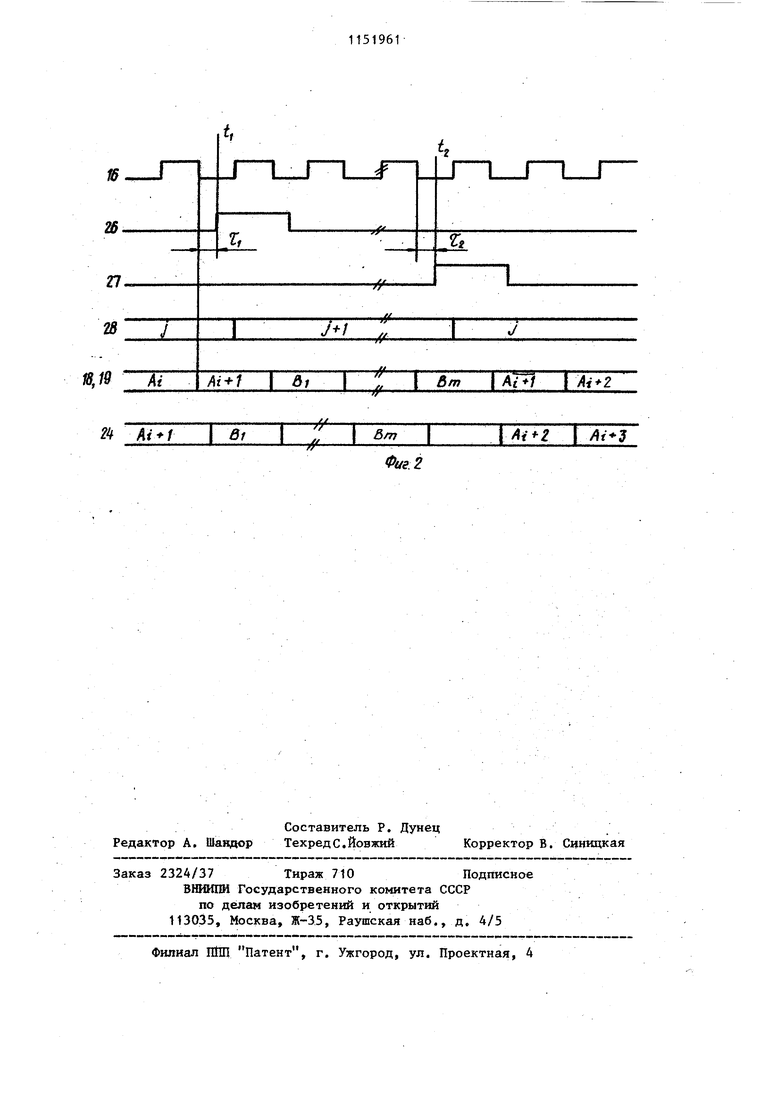

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 временная диаграмма устройства.

В состав устройства входят блок 1 памяти микрокоманд, блок 2 памяти адресов возврата, реверсивный счетчик 3, регистр 4 микрокоманд, дешифратор 5 микрокоманд, коммутатор 6 адреса перехода, коммутатор 7 условия перехода, элементы И 8 и 9, элемент ИЛИ 10,.элемент ИЛИ-НЕ 11, группы сумматоров по модулю два 12 и 13, вход Т внешнего адреса перехода, вход 15 условия перехода синхровход 16, выход 7 операционных микрокоманд, выходы 18-20 адресных полуслов, выход 21 адреса замещения, вход 22 Сигнала выбора безусловного или условного перехода, вход 23 сигнала выбора внешнего или внутреннего адреса перехода, йход 24 данных, выход 25 сигнала условия перехода, признак входа 26 в подпрограмму, признак возврата в программу 27, выход состояния реверсивного счетчика 28. , Устройство работает следующим образом.

Формат слова микрокоманд, хранящихся в блоке 1 памяти микрокоманд имеет вид

т+2

т+1

га

JA

20 21

где и/ - код управляющих микрокоманд, поступающих на вход дешифратора 5 микрокоманд; и,, - код операционных микрокоманд, поступающих на вход

регистра 4 микрокоманд.

Адрес микрокоманды на входе блока 1 представляется в виде двух адд :ресных полуслов, которые поступают с выходов сумматоров по модулю два 12 и 13. Блок 2 памяти адресов возврата представляет собой трехадресное ОЗУ, в котором первые два адреса служат для одновременного считывания информации на два независимых выхода 18 и 19, а третий - для записи информации с выхода 24.

Адрес чтения данных на выходе 18 формируется состоянием реверсивного счетчика 3 и сигналом нулевого потенциала (логического нуля) , а на выход 19 - состоянием реверсивного счетчика 3 и сигналом признака входа 26 в подпрограмму. Адрес записи образуется состоянием реверсивного счетчика 3 и сигналом с выхода коммутатора 7 условия перехода. При совпадении адреса чтения и адреса записи по фронту синхроимпульса на выходе считывается данное, записанное в блок 2 памяти адресов возврата в предьщущем такте, а по спаду синхроимпульса на выходе - данное с входа 24.

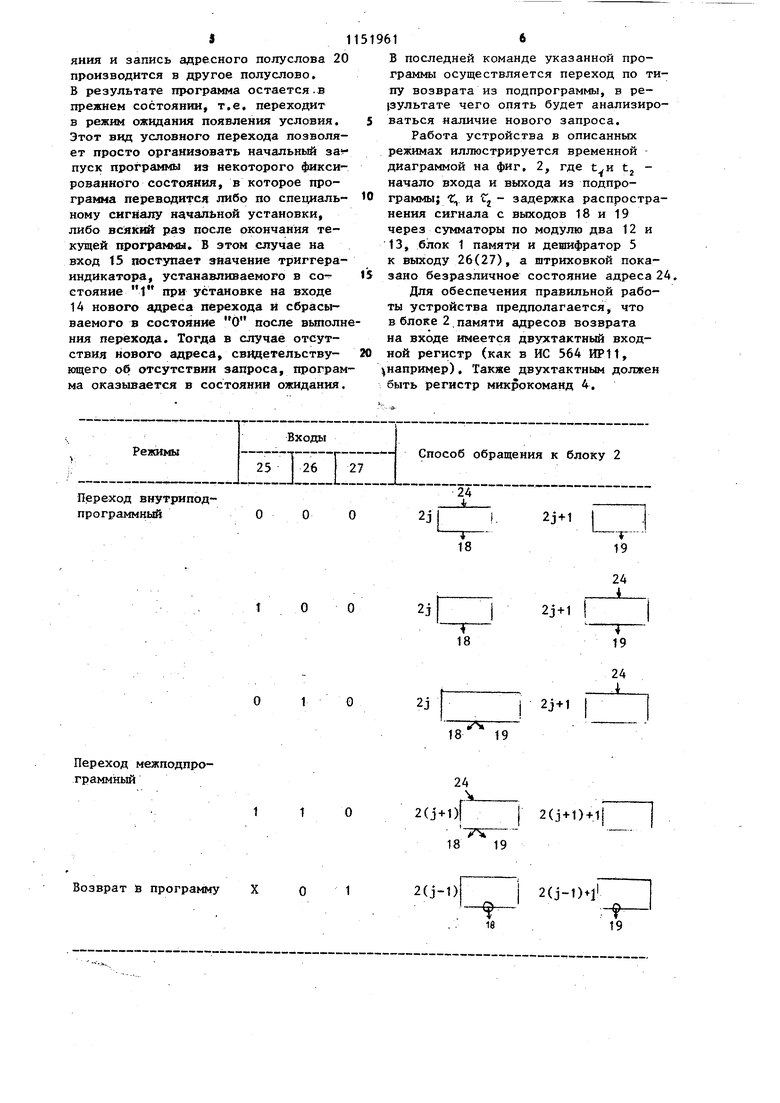

В зависимости от способа обращения к блоку 2 памяти адресов возврата имеет место четыре режима, пред- ставленных в таблице, где j - состояние реверсивного счетчика 3. Отметим особенности каждого из режимов.

J. Переход внутриподпрограммный. Здесь состояние реверсивного счетчика не изменяется, Одно из полуслов 5 заменяется содержимым из поля 20 сло3ва микрокоманды. Выбор замещаемого полуслова определяется полем 21 сло ва микрокоманды. При этом соответст вующий сигнал через коммутатор 7 поступает на выход 25. В результате при чтении одно полуслово оказывает ся новым, а второе старым. 2. Переход межподпрограммный. Перед загрузкой в блок 2 памяти адр сов возврата нового адреса, в случа наличия на выходе 25 сигнала логиче кой 1, на синхровходе реверсивног .счетчика формируется один импульс, которбму его содержимое увеличивается на 1. После этого в блоке памяти адресов возврата происходит запись с входа 24 нового адресного полуслова, которое затем при чтении мультиплицируется на выходах 18 и 1 т.е. начальный адрес подпрограммы предполагается состоящим на двух одинаковых полуслов. При этом старое значение адреса, бывшее перед выполнением перехода, сохраняется. Этот вид перехода используется при входе в подпрограмму. Если при выполнении рассматриваемого вида перехода на выходе 25 имеет место сигнал логического О, то состояние реверсивного счетчика не меняется, а запись производится в правое полуслово старого адреса. |В результате переход будет осуществлен по адресу, полученному модификацией старого адреса путем мультиплицирования его левого полуслова. Этот вид перехода для различных зна чений адреса места замещения на вхо де 25 может использоваться, в частности, при организации начальных пусков. 3. Возврат в программу. Перед возвратом в программу предварительно уменьшается на 1 содержимое реве сивного счетчика 3. Для этого по признаку 27 на входе управления сче том реверсивного счетчика устанавли вается сигнал обратного направления счета, а на входе элемента И 9 разрешение счета. После изменения состояния реверсивного счетчика, старое значение адреса, по которому находилась команда входа в подпрограмму, считывается из блока памяти адресов возврата в инверсном коде, т.е. все адреса возврата предполагаются равными инверсному значению адресов команд входа в рассматрива614емую подпрограмму. Для исключения i стирания адреса возврата в процессе выхода из подпрограммы запись в блок 2 блокируется путем формирования запрета в виде высокого уровня на входе элемента ИЛИ-НЕ 11. Инверсия- адреса команды входа в подпрограмму при этом осуществляется с помощью двух групп сумматоров по модулю два 12 и 13, которые по сигналу 27 становятся инверторами. Рассмотрим теперь подрежимы работы устройства, возникающие в зависимости от способа формирования адреса на входе 24. Эти подрежимы определяются с одной стороны значениями самых замещающих адресных полуслов, а с другой стороны - сигналами 22 и 23. . 1.Условный внутрипрограммный пербход. Здесь по сигналу 22 в качестве адреса замещения выбирается внутренний 20 либо внешний адрес 14. При этом, если полуслово на входе 24 оказывается отличным от обоих адресных полуслов в текущей команде, то переход в зависимости от условия 15 осуществляется по одному из двух направлений. Если же полуслово на входе 24 совпадает с одним из двух старых полуслов 18 или 19, то при одном из значений условия 15 переход фактически будет отсутствовать, поскольку произойдет замещение одного адресного полуслова другим полусловом с тем же значением. Это свойство позволяет очень просто организовать в программе режим ожидания путем соответству-. ющего распределения адресов. Использование внешнего адреса при рассмотренном виде условного перехода позволяет осуществлять автоматическую синхронизацию процессов управления, реализуемых различными устройствами управления . Этот же вид перехода при использовании внешнего адреса 14 удобно, применять для организации многозначного условного перехода, в котором в качестве внешнего адреса используется набор проверяемых условий, а признак 15 выбирает адрес 21. 2.Условный межподпрограммный переход. Здесь-на вход 24 поступает адресное полуслово 20. При этом в случае выполнения условия 15 производится переход на выполнение подпрограммы, а при отсутствии реверсив.jibM счетчик 3 не меняет своего состояния и запись адресного полуслова 20 производится в другое полуслово, В результате программа остается-в прежнем состоянии, т.е. переходит в режим ожидания появления условия. Этот вид условного перехода позволяет просто организовать начальный за- пуск программы из некоторого фиксированного состояния, в которое программа переводится либо по специальному сигналу начальной установки, либо всяк1& раз после окончания текущей программы, В этом случае на вход 15 поступает значение триггераиндикатора, устанавливаемого в состояние 1 при установке на входе 14 нового адреса перехода и сбрасываемого в состояние О после вьтолн ния перехода. Тогда в случае отсутствия нового адреса, свидетельствующего об отсутствии запроса, програм ма оказывается в состоянии ожидания.

Т 00

О 10

Переход межподпрограммный

Возврат в программу

2J + 1 I

2J

Ч

4 19

18

2J

24

J

2(J4-1)

2(j + 1) + l|

18 19

2(j-1)ll

-t19

ie В последней команде указанной программы осуществляется переход по типу возврата из подпрограммы, в ре|зультате чего опять будет анализироваться наличие нового запроса. Работа устройства в описанных режимах иллюстрируется временной диаграммой на фиг, 2, где t,и t начало входа и выхода из подпрограммы; Z;, и fj - задержка распространения сигнала с выходов 18 и 19 через сумматоры по модулю два 12 и 13, блок 1 памяти и дешифратор 5 к выходу 26(27), а щтриховкой показано безразличное состояние адреса 24, Для обеспечения правильной работы устройства предполагается, что в блоке 2 памяти адресов возврата на входе имеется двухтактный входной регистр (как в ИС 564 ИР11, например), Также двухтактным должен быть регистр микрокоманд 4.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807288A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-02-25—Подача