и второй вход деления второго арифметического блока первой группы, второй вход сложения Г1-го арифметического блока первой группы объединены и подкшчены к выходу второго вспомогательного регистра первой группы, вторые входы сложения первого и второго арифметических блоков первой группы, вторые входы умножения и деления п-го арифметического блока первой группы и второй вход первого сумматора объединены и подключены к выходу п-го вспомогательного регистра первой группы, выходы (п+1)-го вспомогательного регистра первой группы подклочены к входу первого вспомогательного регистра, выход первого сумматора подключен к входу регистра инiтервальиого индекса, выходы j-x блоков умножения группы подключены к входам J-X вспомогательных регистров третьей группы, выходы f-X и у-X вспомогательных регистров третьей группы подключены соответственно к входам -X и j-X вспомогательных регистров четвертой группы,выходы j-х из которых подключены к входам j-x вспомогательных регистров пятой группы, выходы j-x вспомогательных регистров третьей группы подключены к первым входам 2f-1 ) групп элементов И первого блока, выходы i-x вспомогательных регистров пятой группы подключены к первым входам 2i-x групп элементов И первого блока, входы первого и второго адресных регистров являются соответственно первым и вторым управляю,щими входами устройства, а выходы подключены к адресным входам соответственно первого и второго блоков памяти вторые входы элементов всех групп перв ого блока объединены и являются третьим управляющим входом устройства, выходы элементов И (.i-1 ) 2 i-x групп первого блока подключены соответственно к первым и вторым входам i-x формирователей переполнения группы, первые и вторые входы которых подключены к входам первого регистра переполнения, первый выход которого подключен к первому входу формирователя числа переполнений, второй вход которого подключен к выходу триггера, вход которого является четвертым управляющим входом устройства, первые и вторые входы первого и второго сумматоров первой группы соответственно объединены и подключены к выходам соответственно первого и второго входных регистров группы.

входы третьего сумматора первой группы подключены к выходам п-го и(п+1 )го входных регистров группы, выходы i-X сумматоров первой группы подключены к входам i-x вспомогательных регистров шестой группы, выход первого из которых подключен к второму входу первого сумматора, а (п-1)-го и п-го - к входам второго сумматора, 5-е выходы i-x арифметических блоков первой группы подключены к входам i k-x вспомогательных регистров седьмой группы (к 1,2,3), выходы i-x из которых (i 2,3,5,6,8,9) подключены к первым входам i-x сумматоров второй группы, выходы первого, четвертого и седьмого из которых подключены к вторым входам соответственно второго, пятого и восьмого сумматоров второй группы, первые входы (J+2J+1) сумматоров второй группы (j 1,2,.., п) объединены и подключены к первому выходу четвертого вспомогательного регистра третьей группы, первый вход первого, вторые входы седьмого, десятого и одиннадцатого сумматоров второй группы объединены и подключены к первому выходу пятого вспомогательного регистра третьей группы, вторые входы первого и четвертого сумматоров второй гоуппы объединены и подключены к выходу п-го вспомогательного регистра третьей группы, вторые входы 3j-x сумматоров второй группы (,2,..., п+1) объединены и подключены к выходу регистра интервального индекса, выход сумматоров второй группы подключены к входам соответствующих вспомогательных регистров восьмой группы, выходы j-x из которых (j 1,,7,in,11j подклчены к nepBbtM входам сложения соответственно К X (к 1,2,,..,п+2 арифметических блоков второй группы, выходы }-х вспомогательных регистров восьмойгруппы ( j 2,5,8 )подключены к вторым входам сложения соответственно К-х (К 1,2,...,П)арифметических блоков второй группы, выходы j-x вспомогательных регистров восьмой группы (j 3,6,9,12 подключены к первым входам умножения соответственно К-х (к 1,2,3,5) арифметических блоков второй группы, вторые входы умножения К-х ( К 1,2,...,4г) арифметических блоков второй группы, выходы вспомогательных регистров восьмой группы (, 6, Я, 12 подключены к первым вхсЗдам умножения соответственно (К 1,2, 3, 5) арифметических блоков.второй группы, вторые входы умножения (, 2, ..., п) арифMetM4ecKMX блоков второй группы подключены к выходам К-х вспомогательных регистров четвертой группы, первые входы умножения {п+1 )-го и( арифметических блоков второй группы подключены к выходам соответственно третьего и чет|вертого регистров, входы которых подключены к соответствуюдим выходам ,второго блока памяти, вторые входы сложения {п+1 )-го и ( арифметических блоков второй группы Ы5ъедииены и подключены к выходу шестого вс 10могательного регистра третьей группы, выходы суимы и произведения арифметических блоков второй группы соответственно подключены к входам вспомогательных регистров девятой группы, выходы К-и пары (К 1,2,,.. ,П+2) которых подк/ючены к соответствующим входам Ц-х сумматоров третьей группы выходы которых соответственно под лвчены к входам вспомогательных регистров десятой группы, выходы которых подключены соответственно к входам вспомогательных регистров одиннадма той группу., выходы которых подключены соответственно к первым входам сумматоров четвертой группы, вторые

входы которых объединены и подключены к выходу второго регистра переполнения, входом подключенного к выходу формирователя числа переполнения, выходы сумматоров четвертой группы подключены к входам соответствующих вспомогательных регистров десятой группы, ;выходы которых подключены к первым входам элементов И соответствующих четных групп второго блока, первые входы элементов И четных групп второго блока подключены к выходам соответствующих вспомогательных регистров десятой группы, вторые входы элементов И всех групп второго блсжа объединены и являются пятым управляющим входом устройства, выходы элементов И каждой пары нечетной и четной групп подключены соответственно к первым и вторым входам соответствующих сумматоров пятой группы, выходы которых подключены к входам соответствующих вспомогательных регистров ,. нздцатой группы, выходы которых, кром (n-f2)-ro, подключены к первым входам соответствующих сумматоров шестой группы, вторые входы которых объединены и подключены к выходу (п+2)-го регистра тринадцатой группы, выходы сумматоров пятой группы является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Устройство для нормализации чисел в модулярном коде | 1984 |

|

SU1242942A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

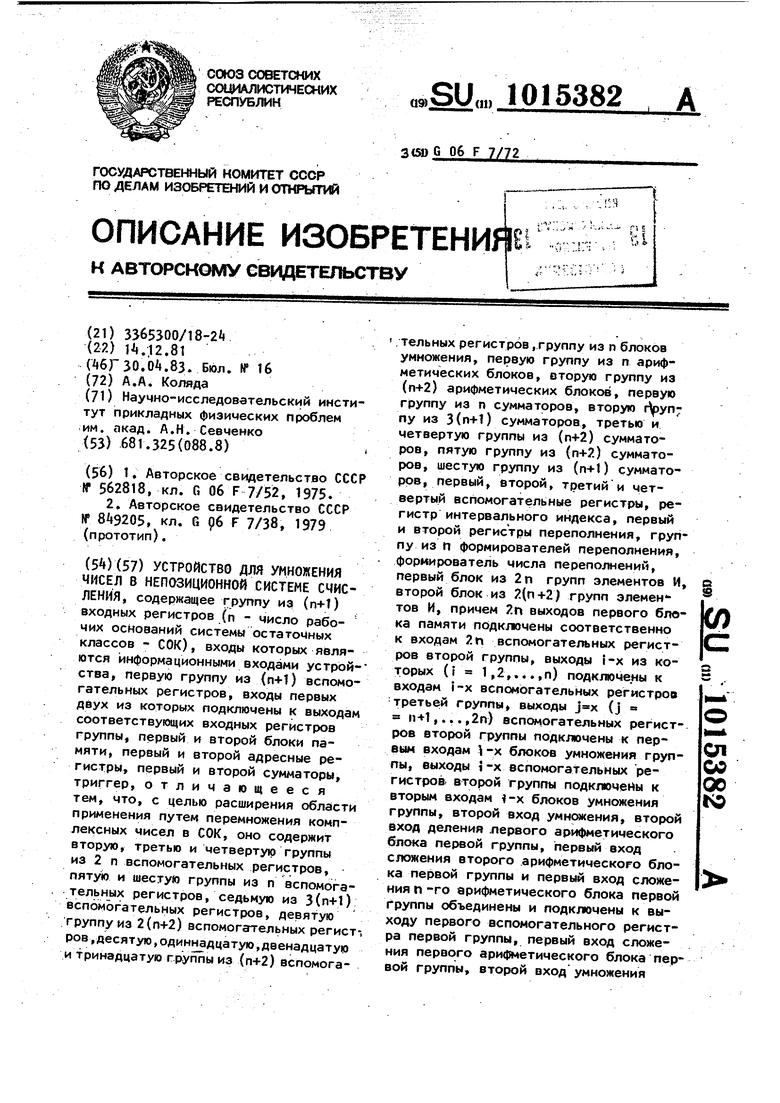

Изобретение относится к вычислитель ной технике и может быть использовано 8 быстродействующих процессорах быстрого преобразования Фурье (БПФ), ориентированных на об работку сигналов невысокой разрядности. Изоестно устройство для умножения, /содержащее регистры, коммутаторы, фор мирователь . кратных множимого, регистр вывода, блок управления, формирователь знака, блок сложения кратных мно жимого, сумматор порядков, блок анали за множителя, блок анализа множимого, формирователь сдвига, блок анализа неопределенной позиции, сдвиговый регистр и соответствующие связи С13Недостаток устройства - ограниченная область применения, связанная с невозможностью обработки комплексных чисел. Наиболее близким к предлагаемому является конвейерное устройство для ;выполнения арифметических операций над множеством чисел, содержащее h каскадов (h- разрядность чисел), причем каждый каскад содержит первый регистр сомножителя, первый сумматор, первый управляющий триггер, выходы первого регистра частичного результата соединены с входами первого сумматора, первая шина тактовых импульсов устройства соединена с тактовыми входами триггеров и регистров, кроме того, каждый каскад устройства содержит второй регистр частичного результата, первый и второй регистры переносов, второй регистр сомножителя, первый и второй регистры делителя второй сумматор, первый и второй блоки постоянной памяти, первый и второй преобразователи прямого кода в дополнительный, элемент ИЛИ, одиннадцать триггеров, второй управляющий триггер, Причем выходы первого, второго, третьего и четвертого триггеров соединены соответственно с входами седьмого.

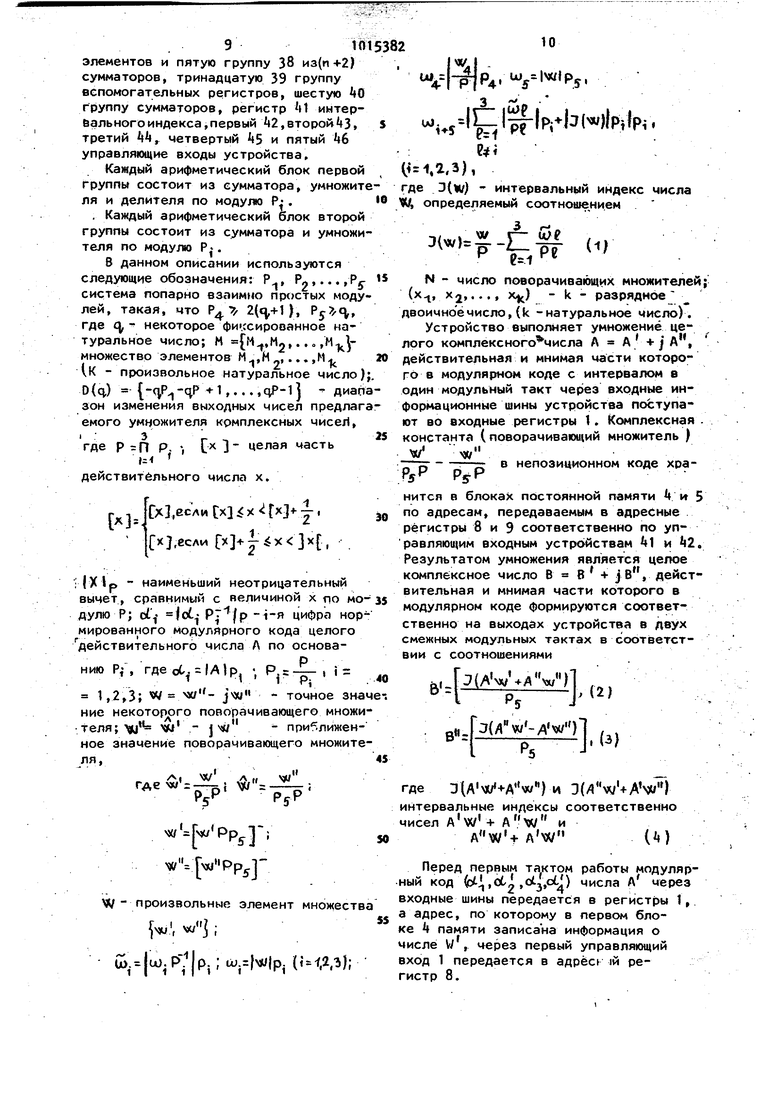

восьмого, девятого и десятого триггеров, выходы пятого и шестого триггеров подключены к управляющим входам первого преобразователя прямого кода в дополнительный, входы старших разр дов которого соединены с выходами пе врго регистра сомножителя, а вход мл шего разряда - с выходом элемента ИЛ ВХОДЫ которого соединены с выходом младшего разряда первого регистра сомножителя и выходом первого управляющего триггера, который подключен также к управляющему входу первого блока постоянной памяти, входы которого соединены с выходами четырех старших разрядов первого сумматора, а выходы - с входами один надцатого и двенадцатого триггеров, входы первого сумматора соединены с выходами первого регистра переносов и выходами первого преобразователя прямого кода в дополнительный, выходы первого сумматора соединены , с входами второго регистра частичного результата и второго регистра переносов, выходы первого регистра де лителя соединены с входами второго регистра делителя, выходы которого содинены с входами первого регистра делителя следующего каскада устройст ва и входами старших разрядов второго преобразователя прямого кода в , дополнительный,вход младшего разряда которого соединен с выходом второго управляющего Триггера, а управляющие входы - с выходами одиннадцатого и двенадцатого триггеров, выходы второго преобразователя прямого кода в дополнительный соединены с входами второго сумматора, другие входы которого соединены с выходами второго регистра перекосов и второго регистра частичного результата, выходы пер косов (п+2 ) младших разрядов Второго сумматора соединены с входами (п+2) старших разрядов первого регистра перекосов следующего каскада, выходы суммы ( ) младших разрядов второго сумматора соединены с входами ) старших разрядов первого регистра частичного результата следующего каскада, выходы седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого триггеров подключены к входам второго блока постоянной памяти, выходы которого соединены соответ ственно с входами пятого и шестого триггеров каскада, предшествующего предыдущему и первого, второго, третьего и четвертого триггеров следующего каскада, выход первого управляющего триггера соединен с входом второго управляющего триггера, выход которого подключен к входу первого управляющего триггера следующего каскада, выходы первого регистра сомножителя подключены к входам второго регистра сомножителя, выходы которого 1 подключены к входам первого регистра сомножителя следующего каскада, тактовые входы второго, третьего, четвертого, пятого и шестого триггеров, первого регистра переносов и первого регистра делителя соединены с первой шиной тактовых импульсов устройства, тактовые входы седьмого, девятого, десятого, одиннадцатого, и двенадцатого триггеров, второго регистра сомножителя второго регистра частичного результата, второго регистра делимого и второго управлякхнего триггера соединены с второй шиной тактовых импульсов устройства 2 }. Недостаток устройства - ограниченная область применения, связанная с невозможностью обработки комплексных чисел. Цель изобретения - расширение области применения. Поставленная цель достигается тем, что устройство для умножения чисел в непозиционной системе счисления, содержащее группу из (п+1) входных регистров (h - число рабочих оснований системы остаточных классов - СОК ), входы КОТОРЫХ являются информационными входами устройства, первую группу из (п+1) вспомогательных регистров, входы первых двух из которых подключены к в.ыходам соответствующих входных регистров группы, первый и второй блоки памяти, первый и второй адресные регистры, первый и второй сумматоры, триггер, содержит вторую,третью и четвертую группы из 2п вспомогательных регистров, пятую и шёстую группы из п вспомогательных регистров, седьмую из. 3 (ti+l ) вспомогательных регистров,восьмую группу из (п + 1) вспомогательных регистров,девятую группу из 2(п+2 ) вспомогательных регистров, десятую, одиннадцатую, двенадцатую и тринадцатую группы из(п+2) вспомогательных регистров, группу из п блоков умножения, первую группу из п арифметических блоков, вторую группу из П+2 арифметических блоков, пер1зую группу из П сумматоров, вторую группу из 3{п+1 ) сумматоров, третью и четвертую группы из h +Л сумматоров, пятую груп5101пу из(п+2) сумматоров, шестую группу из(п+1) сумматоров, первый, второй третий и четвертый BcnoMoratenbHHe регистры, регистр интервального индек йа первый и второй регистры переполнеНИИ, группу и5 |л формирователей переполнения, формирователь числа перепол нений, первый блок из 2И групп элементов И, второй блок из 2(п+2) групп элементов И, причем2 выходов первоГО блока памяти подключены соответственно к входам 2п вспомогательных регистров второй группы, выходы f-х из которых Xi 1,2,...,и) подключены к входам .i-x вспомогательных регистров третьей гоуппы. выходы j-x (j h +1,.... 2 n ) вст)могательных oeгистров втооой группы подключены к первым входам -х блоков умножения группы, выходы t-x вспомогательных регистров второй группы подключены к вторым входам т-х блоков умножения группы, второй вход умножения, второй вход деления первого арифметического блока первой группы, первый вход сложения второго арифметического блока первой гоуппы и первый вхоа сложения п-го арифметического блока первой группы объединены и подк/ночены к выходу первого вспомогательного регистра первой группы, первый {вход сложения первого арифметическо1го блока первой группы, второй вход умножения и второй вход деления второго арифметического блока первой группы, второй вход сложения п-го арифметического блока первой группы объединены и подключены к выходу второго вспомогательного регистра первой группы, вторые бходы сложения перового и второго арифметических блоков первой группы, вторые входы умножения и деле ния п-го арифметического блока первой группы и второй вход первого сумматора объединены и подключены к выходу п-го вспомогательного регистра первой группы, выходы (ин-1)-го вспомогательного регистра первой группы под ключены к входу первого вспомогательного регистра, выход первого сумма.ора подключен к входу второго вспомога тельного регистра, выход второго сумматора подключен к входу регистра интервального индекса, выходы i-x блоков умножения группы подключены к вхо дам J-X вспомогательных регистров третьей группы, выходы i-x и j-x вспомогательных регистров третьей группы подключены соответственно к входам 1-х и J-X вспомогательных ре2гистров четвертой группы, выходы J-x из которых подключены к входам j -х вспомогательных регистров пятой группы, выходы J-X вспомогательных регистров третьей группы подключены к первым входам Д2--1)7Х групп элементов И первого блока, выходы i-x вспомогательных регистров пятой группы подключены к первым входам 2t-x групп элементов И первого б.лрка, входы первого и второго адресных регистров являются соответственно первым и вторьт управляющими входами устройства, а выходы подключены к адресным входам соответственно первого и второго блоков памяти, вторые входы элементов всех групп первого блока объединены и являются третьим управляющим входом устройства, выходы элементов И 12--1 ) и групп первого блока подклочены соответственно к первым и вторым входам i-х формирователей переполнения группы, первые и вторые еходь) которых подключены к входам первого регистра переполнения, первый выход которого подключен к первому входу формирователя числа переполнений, второй вход которого подключен к выходу триггера, вход которого является четвертым управляющим входом устройства, первые и вторые входы первого и второго сумматоров, первой группы соответственно объединены и подключены к выходам соответ- ственно первого и второго входных ре-п гистров группы, входы третьего сумма- . тора первой группы подключены к выходам п-го и(п+1 J-го входных регистров группы, выходы i-x сумматоров первой группы подключены к входам i-x вспомогательных регистров шестой группы, выход первого из которых подключен к второму входу первого сумматора, а (п -1 1-го и п-го - к входам второго сумматора, i -е выходы t-х арифметических блоков первой группы подкгиочены к входам t-X вспомогательных регистров седьмой группы (К 1,2,3), выходы i-x из которых (v 2,, 8,9 ) подключены к первым входам -х сумматоров второй группы, выходы пер-: вого, четвертого и седьмого из которых подключены к вторым входам соответственно второго, пятого и восьмого сумматоров второй группы, первые входы . (j+21Ч-1 )-х сумматоров второй группы (у 1,2 ..;,, П ) объединены и подключены к первому выходу четвертого вспомогательного регистра третьей группы, первый вход первого, вторые входы седьмого, десятого и одиннадцатого суммато ров второй группы объединены и подклочены к первому выходу пятого вспо могательного регистра третьей группы вторые входы первого и четаертого су маторов второй группы объединены и подключены к выходу rt-го вспомогател ного регистра третьей группы, вторые входы 3i-x сумматоров второй группы л . - , - (,2,1.. ,П+1 )объединены И подключе ны к выходу регистра интервального и декса, выходы сумматоров второй груп пы подключены к. входам соответствующих вспомогательных регистров восьмо группы, выходы J-X из которых (J - ,) подключены к первым входам сложения соответственно К-х (к 1,2,.,.,П+2) арифметических бло ков второй группы, выходы J-X вспомогательных регистров восьмой группы (J 2,5,8), подключены к вторым входам сложения соответственно К-х CK 1,2,..,п) арифметических блоко второй группы, выходы j-X вспомогательных регистров восьмой группы {j 3,6,9,12 jf подключены к первым входам умножения соответственно К-х (к 1,2,3,5 )арифметических блоков второй группы, вторые входы умножения К-х (к 1,2,...,П ) арифметических блоков второй группы подключены к выходам К-х вспомогательных оегист оов четвертой группы, первые входы умножения (п +1 )-го и (п+2 )го арифметических блоков второй группы подключены к выходам соответственно тре тьего и четвертого регистров, входы которых подключены к соответствующим выходам второго блока памяти, вторые входы сложения ih-t-l )-го и (п+2 Ьго арифметических блоков второй группы объединены и подключены к выходу шестого вспомогательного регистра тр тьей группы, выходы суммы и произведения арифметических блоков второй группы соответственно подключены к входам вспомогательных регистров девятой группы, выходы К-й пары (К l,2,...,h+. которых подключены к соответствующим входам К-х сумматоров третьей группы, выходы которых соответственно подключены к входам вспомогательных регистров десятой группы, выходы которых подключены соответственно к входам вспомогатель ных регистров одиннадцатой группы, выходы которых подключены соответственно к первым входам сумматоров чет вертой группы, вторые входы которых объединены и подключены к выходу вто рого регистра переполнения-, входом подключенного к выходу формирователя числа переполнения, выходы сумматоров четвертой группы подключены к входам соответствующих вспомогательных регистров десятой группы, выходы которых подключены к первым входам элементов И соответствующих четных ГРУПП второго блока, первые входы элементов И четных групп второго блока подключены к выходам соответствующих вспомогательных регистров десятой группы, вторые входы элементов И всех групп второго блока объединены и являются пятым управляющим входом устройства выходы элементов И каждой пары нечетной и четной групп подключены соответственно к первым и вторым входам соответствующих сумматоров пятой группы, выходы которых подключе-. ны к входам соответствующих вспомогательных регистров тринадцатой группы, выходы которых, кроме {п+2 )-го,.подключены к первым входам соответствующих сумматоров шестой группы, вторые входы которых объединены и подключены к выходу (h+/. )-го регистра тринадцатой группы, выходы сумматоров пятой группы являются выходом устройства. На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит группу 1 входных регистров, первую группу 2 сумматоров,, первую группу 3 вспомогательных регистров, первый k и второй 5 блоки памяти, первый 6 и второй 7 сумматоры, первый 8 и второй 9 адресные регистры, вторую 10 группу вспомогательных регистров, группу 11 из блоков умножения,первую 12 группу арифметических блоков, третью 13, четвертую k, пятую 15, шестую 16 и седьмую 17 группы вспомогательных регистров, вторую группу 18 из четырех сумматоров,, восьмую 19 группу вспомогательных регистров, первый 20 и второй 21, третий 22 и четвертый 23 регистры,вторую группу 2( арифметических блоков, первый блок 25 из 2п групп элементов, девятую 26 группу вспомогательных регистров, группу 27 формирователей переполнения,третью 28 группу сумматоров, триггер 29, первый 30 регистр переполнения, десятую 31 и одиннадцатую 32 группу вспомогательных регистров, формирователь 33 числа переполнения, второй З регистр переполнения, четвертую 35 группу сумматоров, двенадцатую 36 вспомогательных регистров, второй блок 37 из 2() 9101 элементов и пятую группу 38 из{п4-2) сумматоров, тринадцатую 39 группу вспомогательных регистров, шестую 0 группу сумматоров, регистр И интервального индекса, первый А2, второй , третий tik четвертый А5 и пятый А6 управляющие входы устройства. Каждый арифметический блок первой группы состоит из сумматора, умножите ля и делителя по модулю . Каждый арифметический блок второй группы состоит из сумматора и умножителя по модулю Рj. В данном описании используются следующие обозначения: Р, Р,,...,Р система попарно взаимно простых модулей, такая, что 2( ), ,, где q, - некоторое фиссированное натуральное число; М .Mj,.. о ,М множество элементов М-,М ,...,М VK - произвольное натуральное число); D(q,) ( -«-1,.. .,qP-l - диаоа зон изменения выходных чисел предлага емого умножителя комплексных чисеЛ, 1 - 3 fx 3 целая часть где р П р. , 1-1 действитёльного числа х. Cxl.ecAHCxl x-irxJ --, х,если , ; |Х1р - наименьший неотрицательный вычет, сравнимый с величиной х по модулю Р; joL цифра нормированного Модулярного кода целого действительного числа Л по основанию Р,- , гдеоС. |А)р -, Рр- . i 1,2,3; W J4W - точное знач ние некоторого поворачивающего множителя; и j - приближенное значение поворачивающего множите/, W гдечмг- j -ч( 4( ,.W - произвольные элемент множеств , vc/-J ; U) :|u).. ; LU.|Mi/|p. (.l; ; t л л I « р, , ,|tl|f|,,.b(.)|p,lp.. i СЬ1Д.з), где J(w) - интервальный индекс числа определяемый соотношением Э(х/) I« 1. V р ре N - число поворачивающих множителей; (х, Х2х) - k - разрядное двоичноечисло,(k -натуральное число). Устройство выполняет умножение целого комплексного числа А А +j А, действительная и мнимая части которого в модулярном коде с интервалов в один модульный такт через входные информационные шины устройства поступают во входные регистры 1. Комплексная . константа ( позорачиваюи1ий множитель ) в непозиционном коде хранится в блоках постоянной памяти k vt 5 по адресам, передаваемым в адресные регистры 8 и 9 соответственно по управляюи(им входным устройствам 1 и k2, Результатом умножения является целое комплексное число В в + jВ, действительная и мнимая части которого в модулярном коде формируются соответственно на выходах устройства в двух смежных модульных тактах в соответствии с соотношениями ё..21лЧ ; ). (3) где D(A W+A w) и D{/l vy+AVl интервальные индексы соответственно чисел AW + и AW Перед первым тактом работы модулярный код fctj.ot otj,ot|) числа А через входные шины передается в регйст(эы 1, а адрес, по которому в первом блоке 4 памяти записана информация о числе V/ , через первый управляющий вход 1 передается в адрес 1Й реrtгистр 8. и1015382 На первом такте работы из блока | памяти считыв.аетсй набор вычетов и/, (jj , ш , и, ш, , которые передаются в регистры 10; Цифры с выхода регистров 8 передаются в регистры 3, и кроме того, на первый и второй входы сумматоров 2. В результате на выходах сумматоров 2 соответственно сформируются вычеты ,

PI

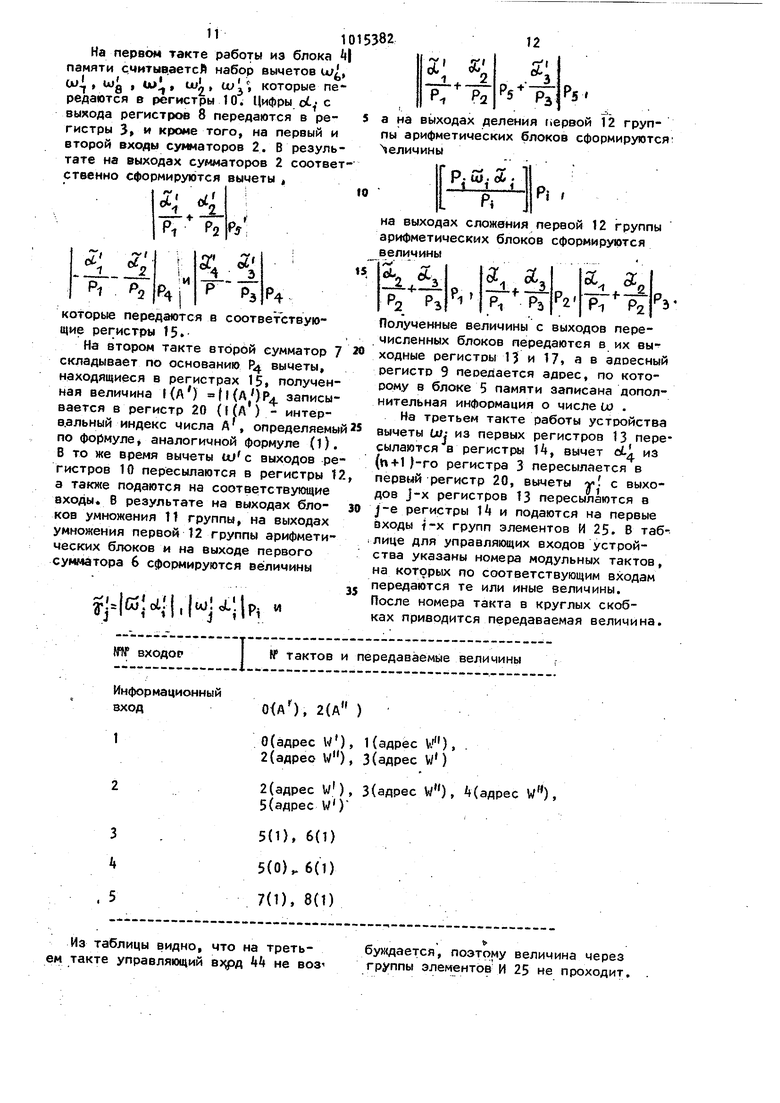

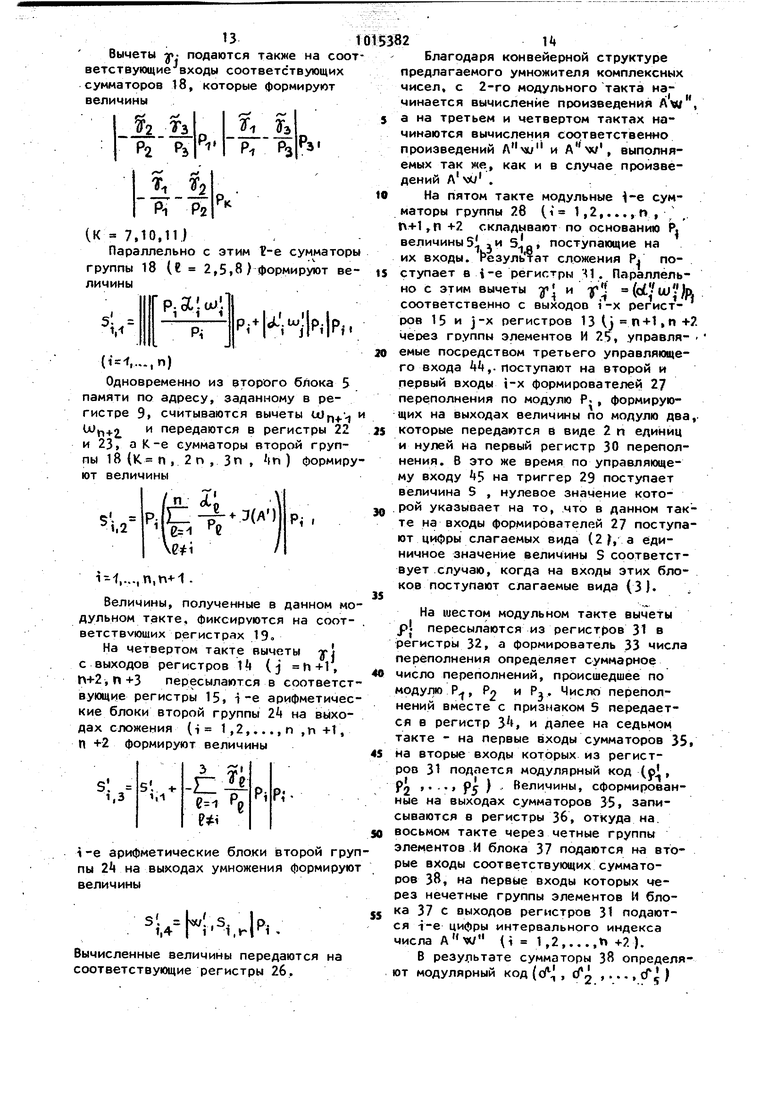

P4 которые передаются в соответствующие регистры 15. На втором такте второй сумматор 7 складывает по основанию р4 вычеты, находящиеся в регистрах 15 полученная величина 1{Л) (1()Р4 записывается в регистр 20 (1(А ) - интерв.альный индекс числа А , определяемы по формулеj аналогичной формуле (1). В то же время вычеты ш с выходов ре гистров 10 пересылаются в регистры 1 а также подаются на соответств ощие входы. В результате на выходах блоков умножения 11 группы, на выходах умножения первой 12 группы арифметических блоков и на выходе первого сумматора 6 сформируются величины , и

I

№ Тактов и передаваемые величины

№№ входор

), 2(А )

О (адрес W), 1 (адрес V.f), . 2(адрес W), 3(адрес W)

2(адрес W), 3(адрес W), (адрес w), 5(адрес W)

Из таблицы видно, что на третьем такте управляющий втфд k не воз а н пы вел

на выходах сложения первой 12 группы арифметических блоков сформируются величины

51Л

3Р-) Р2

буждается, поэтому величина через группы элементовИ 25 не проходит. а выходах деления (ервой 12 групарифметических блоков сформируются; ичины PI Полученные величины с выходов перечисленных блоков передаются в их выходные регистоы 13 и 17, а в адресный регистр 9 пеоеяается адоес, по которому в блоке 5 памяти записана дополнительная информация о числе и . На третьем такте работы устройства вычеты W; из первых регистров 13 пересылаются в регистры И, вычет oL из (n-fl )-го регистра 3 пересылается в первый регистр 20, вычеты vf с выходов J-X регистров 13 пересылаются в у-е регистры Н и подаются на первые входы t-x групп элементов И 25. В таблице для управляющих входов устройства указаны номера модульных тактов, на которых по соответствующим входам передаются те или иные величины. После номера такта в круглых скобках приводится передаваемая величина. Вычеты у- подаются также на COO ветствующие входы соответствующих сумматоров 18, которые формируют величины Р: -л ТГ Р| (К 7,10,11.), Параллельно с этим t-e сумматор группы 18 (Ч 2,5,8 ) формируют ве личины .; Pi1 i j|pt|pi (,..-,) Одновременно из второго блока 5 памяти по адресу, заданному в регистре 9, считываются вычеты и передаются в регистры 22 и 23, а К-е сумматоры второй группы 18 (К- П , 2 п , Зп , и ) формир ют величины Р/г: чЬ i-f,...,n,n+1 Величины, полученные в данном м дульном такте, фиксируются на соот ветствуюших регистрах 19о На четвертом такте вычеты yj с выходов регистров 1 ( j h +1, h+2,h+3 пересылаются в соответс вующие регистры 15, 1-е арифметиче кие блоки второй группы 2 на выхо дах сложения (1 1,2,..., п , ti +1, П +2 формируют величины э ; -С i-е арифметические блоки второй гр пы на выходах умножения формиру величины s. IP i,t- Вычисленные величины передаются на соответствующие регистры 26. 2U Благодаря конвейерной структуре предлагаемого умножителя комплексных чисел, с 2-го модульного такта начинается вычисление произведения а на третьем и четвертом тактах начинаются вычисления соответственно , выполняпроизведений и случае произвеемых так же, как и в дений А .. На пятом такте модульные i-e сумматоры группы 28 (t 1,2,...,г, ,n +2 складывают по основанию Р, величины 51 а и , поступающие на их входы. 1 езультат сложения Р. поступает в |-е регистры . Параллельно с этим вычеты у и -jplt (otyiu fe соответственно с выходов i-х регистров 15 и j-X регистров 13 (j ,п +. через группы элементов И 25, управля- емые посредством третьего управляющего входа 4,. поступают на второй и первый входы i-x формирователей 27 переполнения по модулю Р. , формирующих на выходах величины по модулю два, которые передаются в виде 2 п единиц и нулей на первый регистр 30 переполнения. В это же время по управляющему входу 45 на триггер 29 поступает величина S , нулевое значение которой указывает на то, что в данном такте на входы формирователей 27 поступают цифры слагаемых вида (2 а единичное значение величины S соответствует случаю, когда на входы этих блоков поступают слагаемые вида (3). На шестом модульном такте вычеты р1 пересылаются из регистров 31 в |эегистры 32, а формирователь 33 числа переполнения определяет суммарное число переполнений, происшедшее по и PJ. Число перепол 2 модулю с, г2 нений вместе с признаком 5 передается в регистр 3, и далее на седьмом такте - на первые входы сумматоров 35, на вторые входы которых из регистров 31 подается модулярный код (, Ро Р5 ) Величины, сформированные на выходах сумматоров 35 записываются в регистры 36, откуда на. восьмом такте через четные группы элементов .И блока 37 подаются на вторые входы соответствующих сумматоров 38, на первые входы которых через нечетные группы элементов И блока 37 с выходов регистров 31 подаются i-e цифры интервального индекса числа А W (,2n+.). В результате сумматоры 38 определяют модулярный код (Лт , cfg , .., сГ ) . 5П0153.8216 интервального индекса 3( x/-i vuЧ йз еденйя. На этом выполнение операкоторый записывается в регистрах 39. iliHM умножения комплексных чисел А и На девятом такте цифры сА| - )W заканчивается, a(l,2, )с выходов регистров 38 по- , Таким образом, введение в состав даются на первые входы сумматоров .«О, s устройства двенадцати групп вспомоа на вторые их входы с выхода (ги-2/-го гательных регистров, пяти групп сумрегистра 39 подается цифра (/ .8 рё- маторов, Двух блоков по 2п групп зультате на выходах сумматоров tO в ; соответствии с ( 2 Г сформируется МОДУ лярный код (р, р PJ рА ) дейст в полнения и числа переполнения, ревительной части В произведения Aw гистров переполнения и соответствуюв системе счисления в модулями Р,, щих связей, позволяет на данном устPj, РЗ k а на десятом модульном ройстве выполнять умножение комптакте в соответствии ; {3| будет по- лексных чисел в непозиционной систел учен модулярный код (ii 2 счисления, существенно повышая 4 ) мнимой части В искомого про- при этом скорость вычисления. элементов И, двух групп арифметических блоков, формирователей пере

Авторы

Даты

1983-04-30—Публикация

1981-12-14—Подача