1

Изобретение относится к вычисли-, тельной технике и предназначено для использования в арифметических устройствах с плавающей запятой, функци онирующих в йодулярной системе счисления.

Целью изобретения является повышение быстродействия устройства.

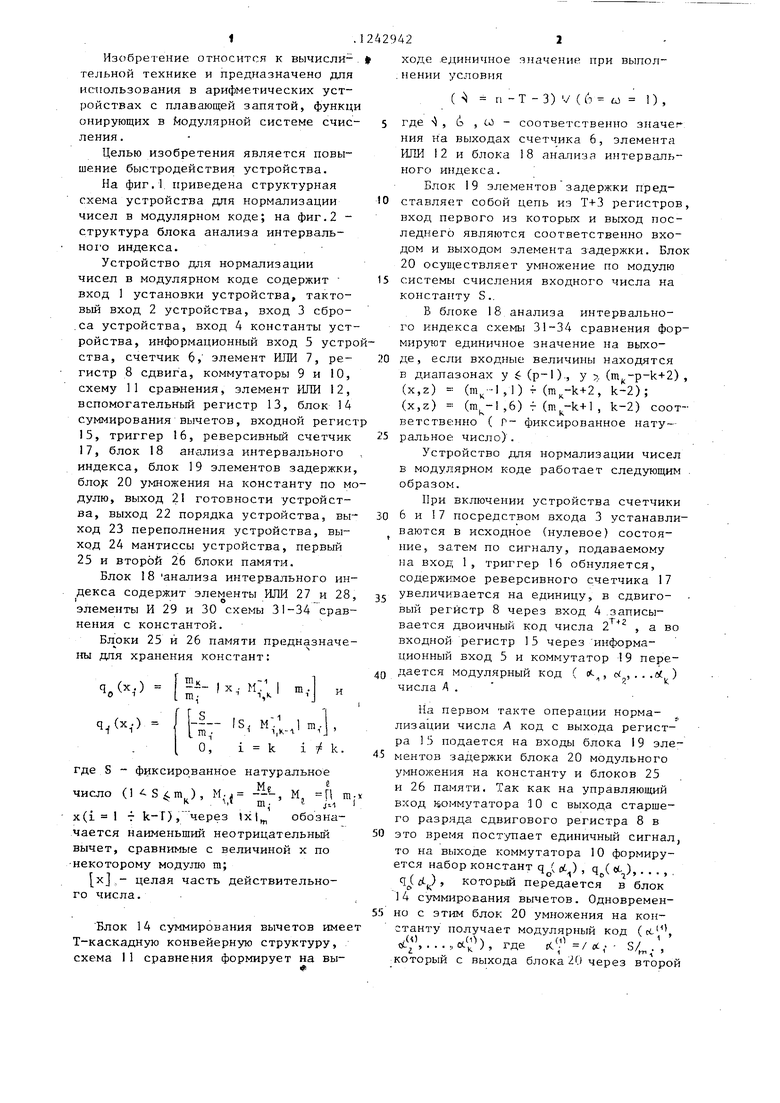

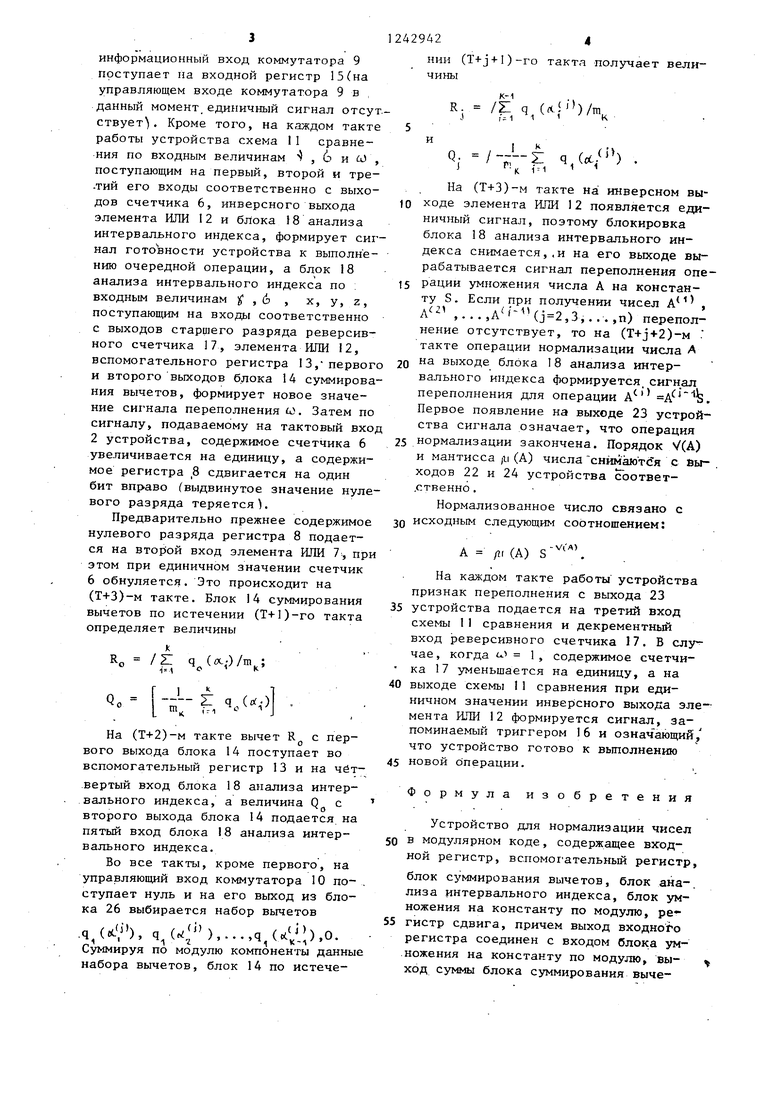

На фиг.1 приведена структурная схема устройства для нормализации чисел в модулярном коде; на фиг.2 - структура блока анализа интервального индекса.

Устройство для нормализации чисел в модулярном коде содержит вход 1 установки устройства, тактовый вход 2 устройства, вход 3 сбро- .са устройства, вход 4 константы устройства, информационный вход 5 устроства, счетчик 6, элемент ИЛИ 7, регистр 8 сдвига, коммутаторы 9 и 10, схему 11 срав-нения, элемент ИЛИ 12, вспомогательный регистр 13, блок 14 суммирования вычетов, входной регист 15, триггер 16, реверсивный счетчик 17, блок 18 анализа интервального индекса, блок 19 элементов задержки, 20 умножения на константу по модулю, выход 21 готовности устройства, выход 22 порядка устройства, выход 23 переполнения устройства, выход 24 мантиссы устройства, первый 25 и второй 26 блоки памяти.

Блок 18 анализа интервального индекса содержит элементы ИЛИ 27 и 28, элементы И 29 и 30 схемы 31-34 сравнения с константой.

Блоки 25 и 26 памяти предназначены для хранения констант:

q,(x.)

m

m

m.

---- s

0,

m.

i k

k,

где S - фиксиррванное натуральное число (), М. M, 4m;.

x(i 1 т k-Г), через Ixl обозна- .чается наименьший неотрицательный вычет, сравнимые с величиной х по некоторому модулю га;

к.- целая часть действительного числа. ,

Блок 14 суммирования вычетов имеет Т-каскадную конвейерную структуру, схема 11 сравнения формирует на вы42942

ходе .единичное значение при выпол- .нении условия

( п -Т -3) V (6 j 1) ,

5 где , i , J - соответственно значег ния на выходах счетчика 6, элемента ИЛИ 12 и блока 18 анапиза интервального индекса.

Блок 19 элементов задержки предtO ставляет собой цепь из Т+3 регистров, вход первого из которых и выход последнего являются соответственно входом и выходом элемента задержки. Блок 20 осуществляет умножение по модулю

15 системы счисления входного числа на константу S..

В блоке 18 анализа интервального индекса схемы 31-34 сравнения формируют единичное значение на выхо20 де, если входные величины находятся в диапазонах у (р-1)., у :, (m -p-k+2) , (x,z) (,1) (m -k+2 , k-2); (x,z) (,6) f (, k-2) соответственно ( P- фиксированное нату-

i 5 ральное число) .

Устройство для нормализации чисел в модулярном коде работает следующим . образом.

При включении устройства счетчики

30 6 и 17 посредством входа 3 устанавливаются в исходное (нулевое) состояние, затем по сигналу, подаваемому на вход 1, триггер 16 обнуляется, содержимое реверсивного счетчика 17

JJ увеличивается на единицу, в сдвиговый регистр 8 через вход 4 .записыТ -

вается двоичный код числа 2 , а во входной регистр 15 через информационный вход 5 и коммутатор 19 передо дается модулярный код ( Л, d., . . .ef.} числа Д .

На первом такте операции нормализации числа А код с выхода регистра 15 подается на входы блока 19 элементов задержки блока 20 модульного умножения на константу и блоков 25 и 26 памяти. Так как на управляющий вход коммутатора 10 с выхода старшего разряда сдвигового регистра 8 в

это время поступает единичный сигнал, то на выходе коммутатора 10 формируется набор констант q(ot),q(oi,) Ч( d) , которьш передается в блок 14 суммирования вычетов. Одновременно с 3TiiM блок 20 умножения на константу получает модулярный код (с., ,...,Ъ, где ,. , который с выхода блока 2() через второй

3

информационный вход коммутатора 9 поступает па входной регистр 15(на управляющем входе коммутатора 9 в данный момент.единичный сигнал отсутствует. Кроме того, на каждом такте работы устройства схема 11 сравнения по входным величинам 5 , о и 6J , поступающим на первый, второй и тре- -тий его входы соответственно с выходов счетчика 6, инверсного выхода элемента ИЛИ 12 и блока 18 анализа интервального индекса, формирует сигнал готовности устройства к выполнению очередной операции, а блок 18 анализа интервального индекса по ; входным величинам if , 6 , х, у, z, поступающим на входы соответственно с выходов старшего разряда реверсивного счетчика 17, элемента ИЛИ 12, вспомогательного регистра 13, первого и второго выходов блока 14 суммирования вычетов, формирует новое значение сигнала переполнения w. Затем по сигналу, подаваемому на тактовый вход 2 устройства, содержимое счетчика 6 увеличивается на единицу, а содержимое регистра ,8 сдвигается на один бит вправо (выдвинутое значение нулевого разряда теряетсяh

Предварительно прежнее содержимое нулевого разряда регистра 8 подается на второй вход элемента ИЛИ 7, при этом при единичном значении счетчик 6 обнуляется. Это происходит на (Т+3)-м такте. Блок 14 суммирования вычетов по истечении (Т+)-го такта определяет величины

о l;

0 (Т+2)-м такте вычет R с первого выхода блока 14 поступает во вспомогательный регистр 13 и на четвертый вход блока 18 апализа интервального индекса, а величина Q, с второго выхода блока 14 подается на пятый вход блока 18 анализа интервального индекса.

Во все такты, кроме первого, на управляющий вход коммутатора 10 по- ступает нуль и на его выход из блока 26 выбирается набор вычетов

.qJelV ), q(),...,q,().0. Суммируя по модулю компоненты данны набора вычетов, блок 14 по истече242942. 4

НИН (T+j+l)-ro такта получает величины

К-1

R. /Е q(P )/m,

i- -rVf, -.

На (Т+3)-м такте на инверсном выходе элемента ИЛИ 12 появляется единичный сигнал, поэтому блокировка блока 18 анализа интервального индекса снимается,,и на его выходе вырабатывается сигнал переполнения операции умножения числа А на константу S. Если при получении чисел , ,...,A - 4j 2,3, ...,п) переполнение отсутствует, то на (T+j+2)-M . такте операции нормализации числа А

на выходе блока 18 анализа интервального индекса формируется, сигнал переполнения для операции . Первое появление на выходе 23 устройства сигнала означает, что операция

нормализации закончена. Порядок V(A) и мантисса ju (А) числа снйм ают(Гя с выходов 22 и 24 устройства соответ- .ственно. Нормализованное число связано с

сходным следующим соотношением:

А /гг (А) S

-V( A)

На каждом такте работы устройства признак переполнения с выхода 23

устройства подается на третий вход схемы 11 сравнения и декрементный вход реверсивного счетчика 17. В слу чае, когда 1, содержимое счетчи- ка 17 уменьшается на единицу, а на

выходе схемы 11 сравнения при единичном значении инверсного выхода элемента ИЛИ 12 формируется сигнал, запоминаемый триггером 16 и означающий/ что устройство готово к выполнению

новой операции.

Формула изобретения

Устройство для нормализации чисел в модулярном коде, содержащее входной регистр, вспомогательный регистр,

блок суммирования вычетов, блок ана-. лиза интервального индекса, блок умножения на константу по модулю, ре гистр сдвига, причем выход входного регистра соединен с входом блок;а ум- ножения на константу по модулю, вы- ход суммы блока суммирования вычетов соединен с входом вспомогательного регистра, о тличающее- с я тем, что, с целью повышения быстродействияi оно содержит счет- чик, два элемента ИЛИ, реверсивный счетчик, два блока памяти, два коммутатора, блок элементов задержки, схему сравнения и триггер, а блок анализа интервального индекса содер- жит два элемента И, два элемента ИЛИ и четыре схемы сравнения с константой, причем вход установки устройства соединен с входом записи регистра сдвига, управляющим входом перво- го коммутатора, нулевым входом триггера и суммирующим входом реверсивного счетчика, тактовый вход устройства соединен с счетным входом счетчика и входом сдвига регистра сдвига информационный вход которого соединен с входом,константы устройства, вход сброса которого соединен с первым входом первого элемента ИЛИ устройства и входом сброса реверсивного счетчика, информационный вход устройства соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом блока умножения на константу по модулю, выход первого коммутатора соединен с входом входного регистра, выход которого соединен с входом блока элементов задержки и адресными входами первого и второго блоков памяти, выхода которых Соединены с соответствующими информационными входами второго коммутатора, управляющий вход и выход которого соединены соответственно с выходом старшего разряда регистра сдвига и входом блока суммирования вычетов, выходы, кроме младшего, разрядов регистра сдвига соединены соответственно с входами второго эле мента ИЛИ устройства, выход счетчика является выходом порядка устройства и соединен с первым входом схемы сравнения, выход которой соединен с единичным входом триггера.

выход которого является выходом готовности устройства, второй И третий входы схемы сравнения соединены соответственно с инверсным выходом второго элемента ИЛИ устройства и вычитающим ВХОДОМ реверсивного счетчика,- выход младшего разряда регистра сдвига соединен с вторым входом первого элемента ИЛИ устройства, выход которого соединен с входом сброса счетчика, выход суммы блока суммирования вычетов соединен с входами первой и второй схем сравнения с константой блока анализа интервального индекса, вы ход вспомогательного регистра и выход числа переполнений блока суммирования вычетов соединены соответственно с первым и вторым входами третьей и четвертой схем сравнения с константой блока анализа интервального индекса:, выход старшего разряда реверсивного счетчика и инверсный: выход второго элемента ИЛИ устройства соединены соответственно с первым и вторым входами первого элемента ИЛИ блока анализа интервального индекса, инверсный выход второго элемента ИЛК1 которого соединен с вычитающим входом реверсивного счетчика и является выходом переполнения устройства, выход мантиссы которого соединен с выходом блока элементов задержки, в блоке анализа интервального индекса выходы первой и третьей схем сравнения с константой соединены соответственно с первым и вторым входами первого элемента И, выход которого соединен с первым входом вто второго элемента ИЛИ, блока анализа интервального индекса, второй и третий входы которого соединены соответственно с инверсным выходом первого элемента ИЛИ, блока анализа интервального индекса, и выходом второго элемента И, первый и второй входы которого соединены соответственно с выходами второй и четвертой схем сравнения с константой.

Фиг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах. с плавающей запятой, функционирующих в модулярной системе счисления. Цель изобретения - повышение быстро- .действия устройства. Цель достигается за счет реализации процедуры умножения числа в интервально-модулярном коде на некоторую константу. 2 ил. ю 4 to СО i4 ю

| Устройство для сложения чисел в системе остаточных классов | 1980 |

|

SU930317A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1975 |

|

SU601689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-09-28—Подача