Изобретение относится к вычислительной технике и предназначено для использования в арифметических .устройствах с плавающей запятой, функционирующих в модулярной системе счисления-.

Цель изобретения - расширение области применения Sa счет работы в модулярной системе счисления. 1

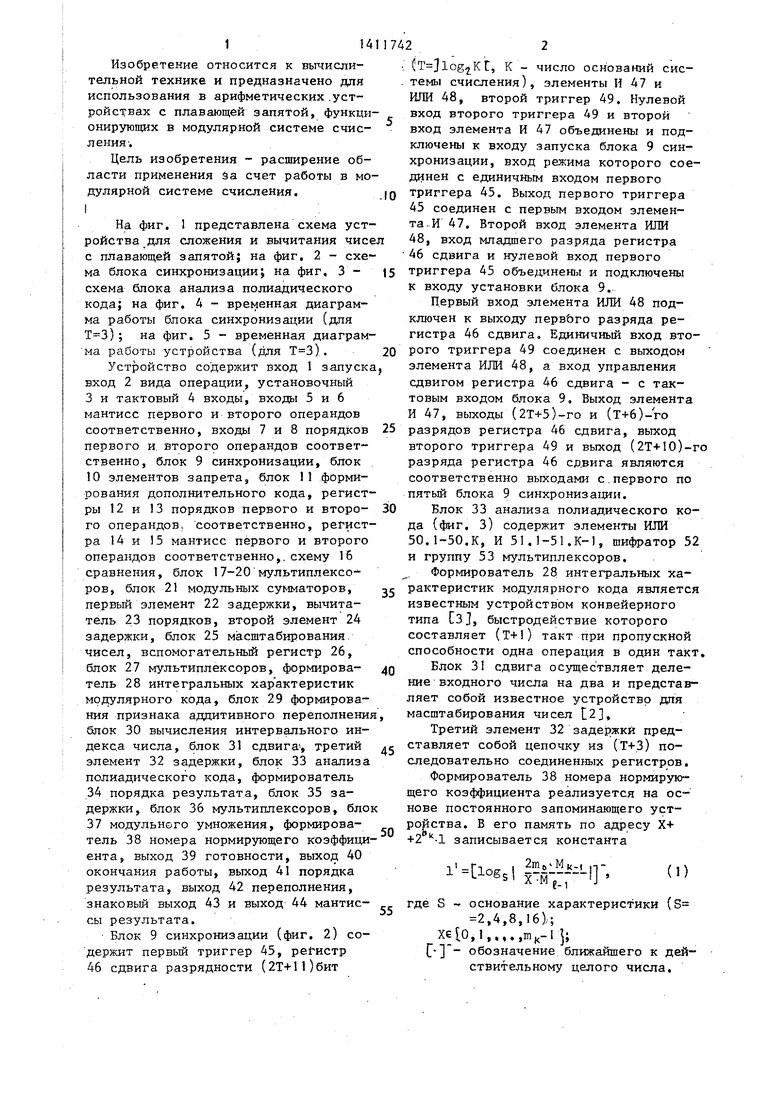

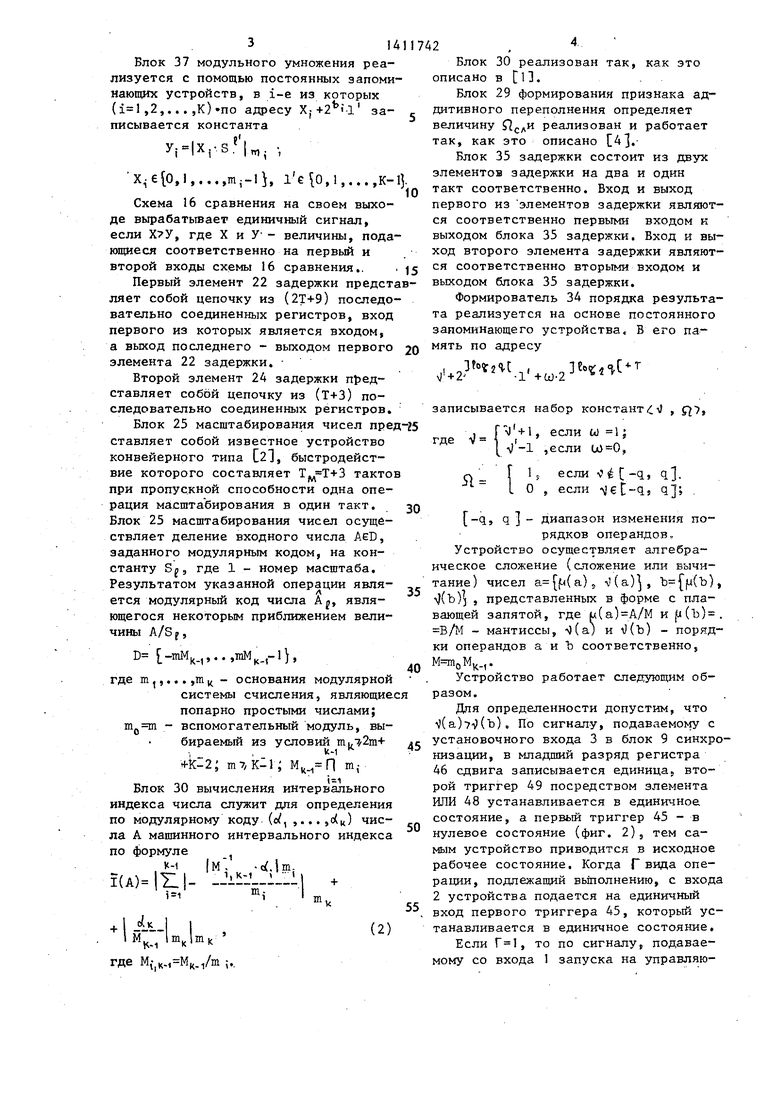

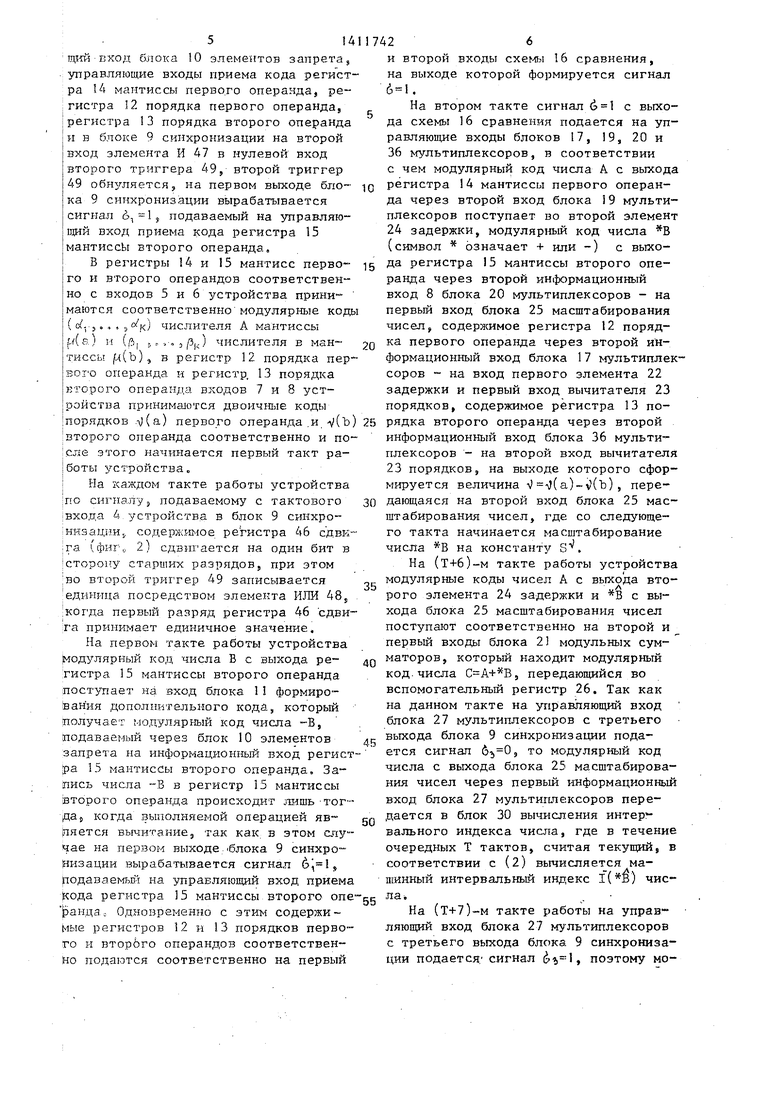

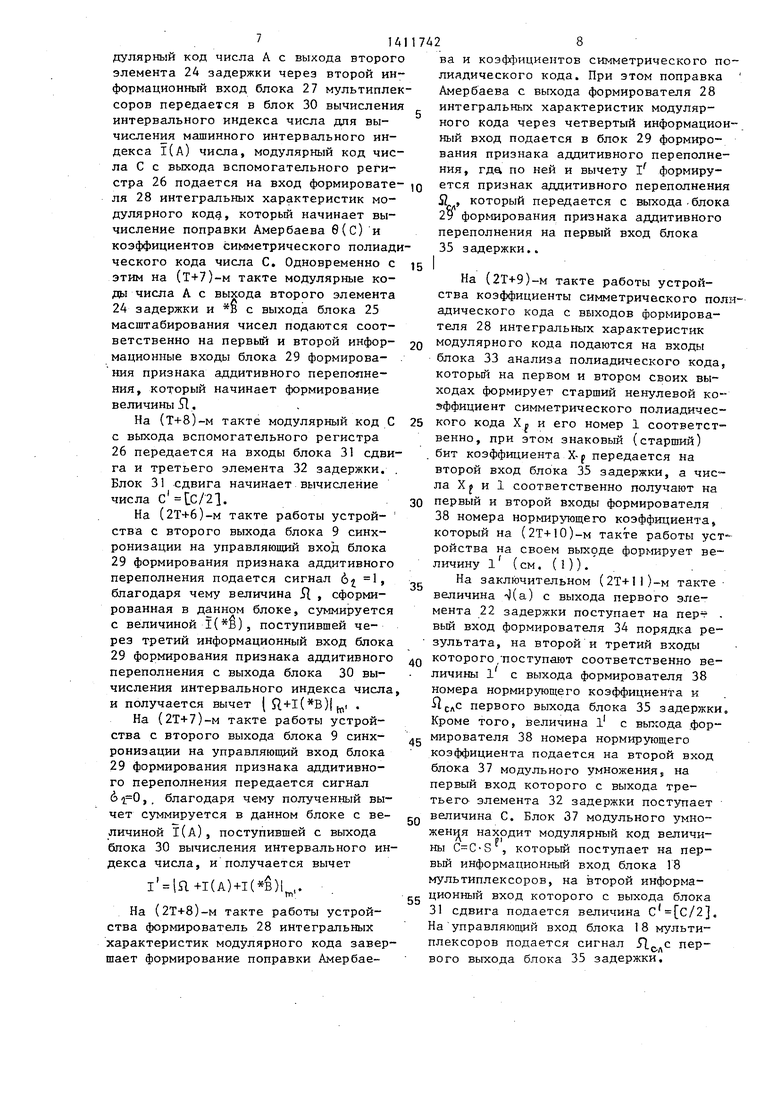

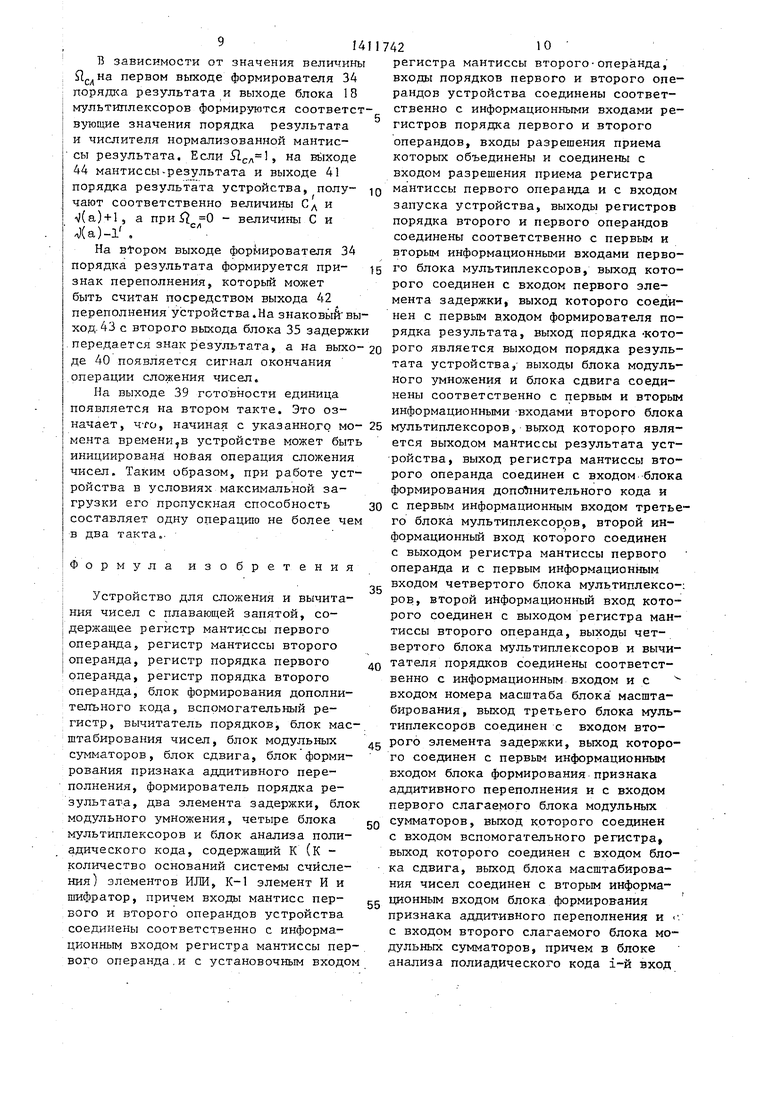

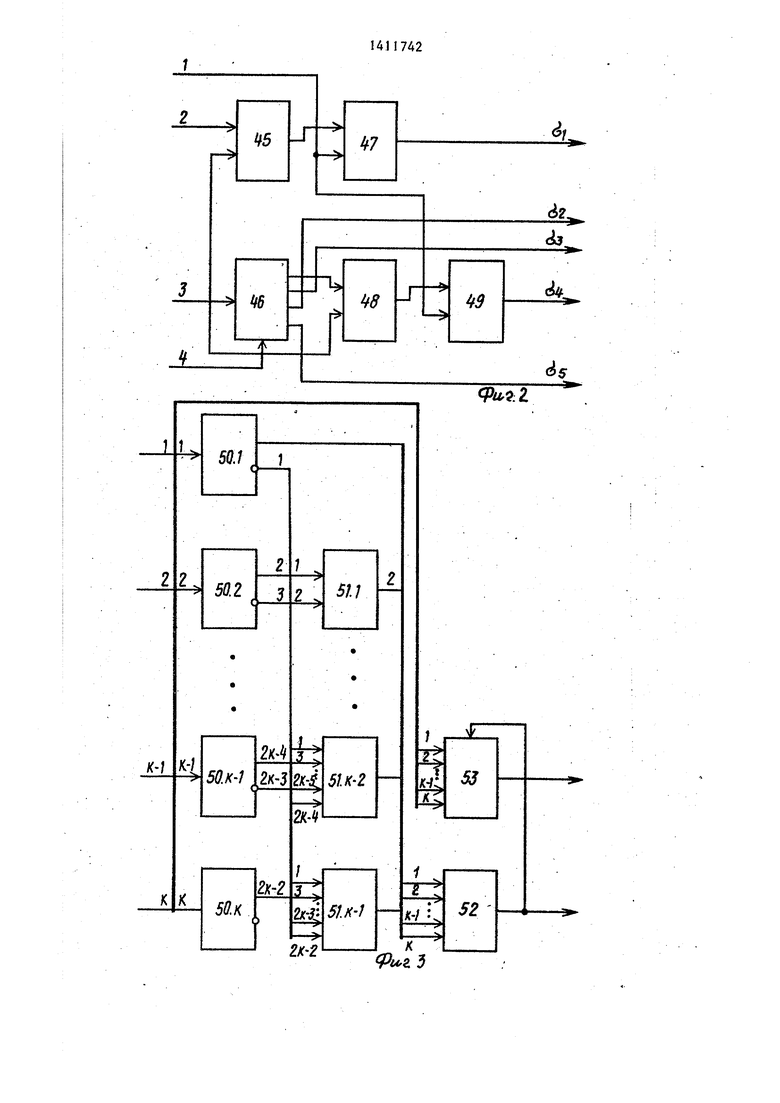

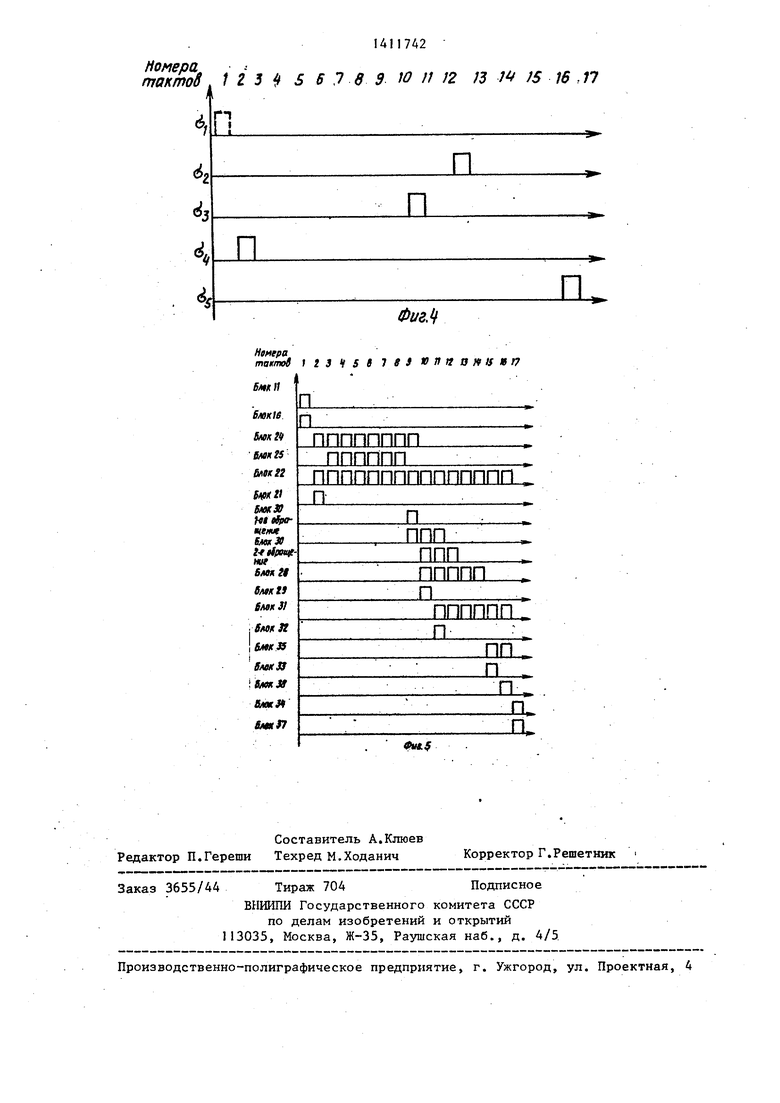

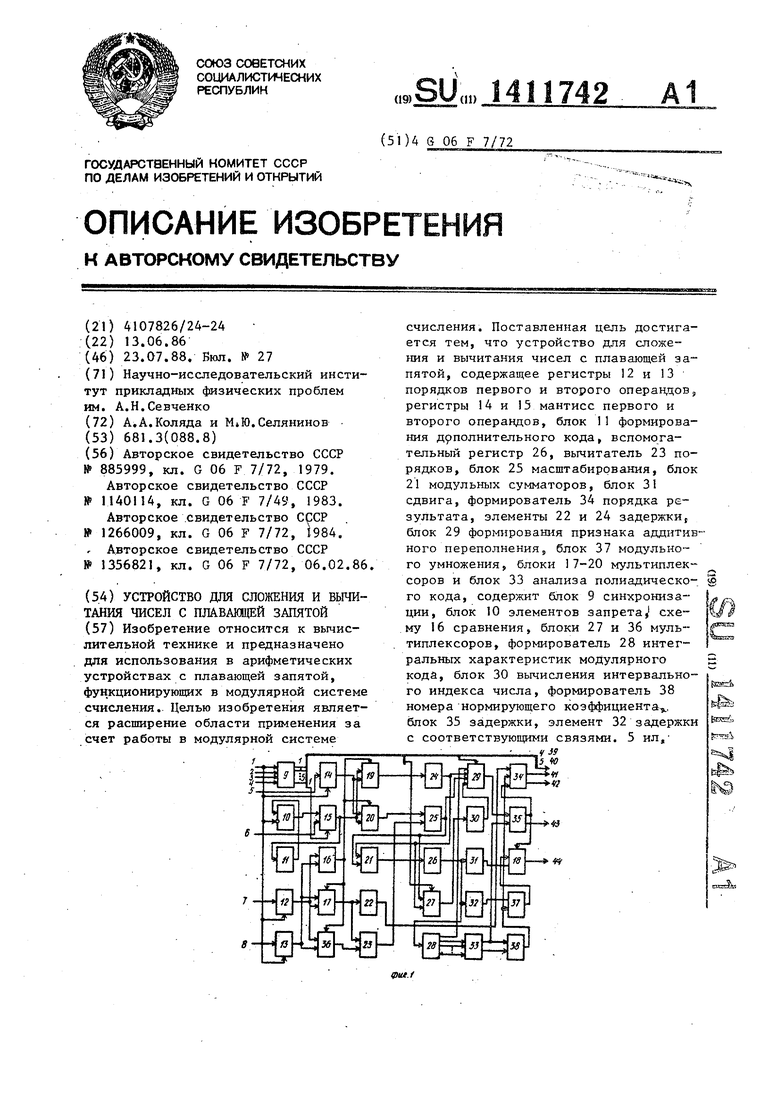

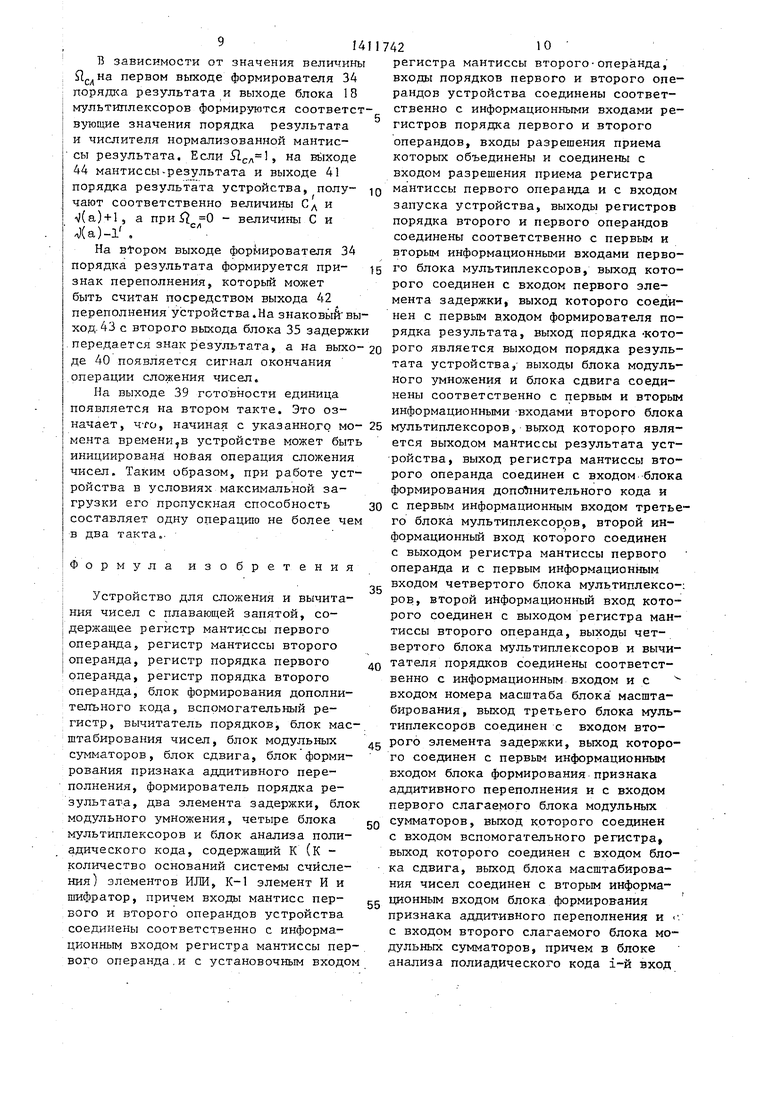

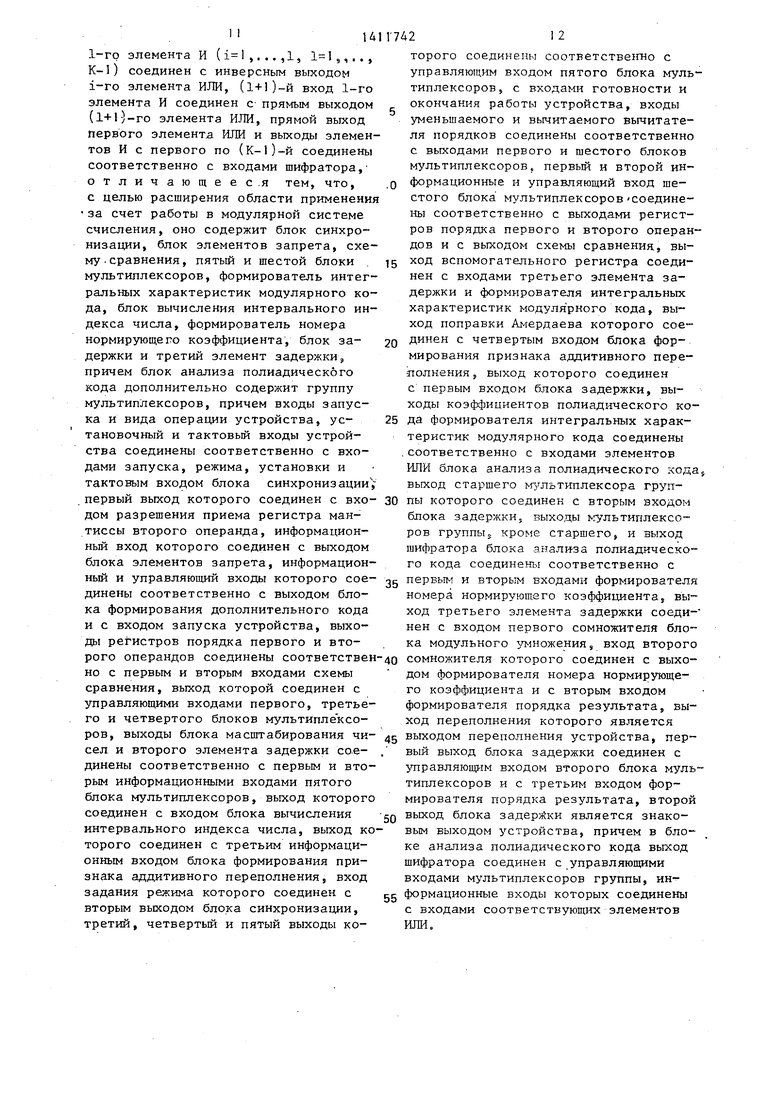

На фиг. 1 представлена схема устройства для сложения и вычитания чисе с плавающей запятой; на фиг, 2 - схема блока синхронизации; на фиг. 3 - схема блока анализа полиадического кода; на фиг. 4 - временная диаграмма работы блока синхронизации (для ); на фиг. 5 - временная диаграм- ма работы устройства (для ),.

Устройство содержит вход 1 запуска вход 2 вида операции, установочный 3 и тактовый 4 входы, входы 5 и 6 мантисс первого и второго операндов соответственно, входы 7 и 8 порядков первого и второго операндов соответственно, блок 9 синхронизации, блок 10 элементов запрета, блок 11 формирования дополнительного кода, регистры 12 и 13 порядков первого и второ- го операндов, соответственно, регистра 14 и 5 мантисс первого и второго операндов соответственно,, схему 16 сравнения, блок 17-20 мультиплексоров, блок 21 модульнь х сумматоров, первый элемент 22 задержки, вычита- тель 23 порядков, второй элемент 24 задержки, блок 25 масштабирования, чисел, вспомогательньй регистр 26, блок 27 мультиплексоров, формирова- тель 28 интегральных хар актеристик модулярного кода, блок 29 формирования признака аддитивного переполнени блок 30 вычисления интервального ин- декс.а числа, блок 31 сдвига, третий элемент 32 задержки, блок 33 анализа полиадического кода, формирователь 34 порядка результата, блок 35 задержки, блок 36 мультиплексоров, бло 37 модульного умножения, формирователь 38 номера нормирующего коэффициента, выход 39 готовности, выход 40 окончания работы, выход 41 порядка результата, выход 42 переполнения, знаковый выход 43 и выход 44 мантис- сы результата.

Блок 9 синхронизации (фиг. 2) со- держит первьш триггер 45, регистр 46 сдвига разрядности (2Т+1 Обит

Q

5 0

5 0 5 0 g

(, к - число оснований системы счисления), элементы И 47 и ИЛИ 48, второй триггер 49. Нулевой вход второго триггера 49 и второй вход элемента И 47 объединены и подключены к входу запуска блока 9 синхронизации, вход режима которого соединен с единичным входом первого триггера 45. Выход первого триггера

45соединен с первым входом элемента. И 47. Второй вход элемента ИЛИ 48, вход младщего разряда регистра

46сдвига и нулевой вход первого триггера 45 объединен, и подключены к входу установки блока 9.

Первый вход элемента ИЛИ 48 подключен к выходу первЪго разряда регистра 46 сдвига. Единичный вход второго триггера 49 соединен с выходом элемента ИЛИ 48, а вход управления сдвигом регистра 46 сдвига - с тактовым входом блока 9, Выход элемента И 47, выходы (2Т+5)-го и (Т+6)-го разрядов регистра 46 сдвига, выход второго триггера 49 и выход (2Т+10)-го разряда регистра 46 сдвига являются соответственно выходами с.первого по пятьй блока 9 синхронизации.

Блок 33 анализа полиадического кода (фиг. 3) содержит элементы ИЛИ 50.1-50.К, И 51.1-51.К-1, шифратор 52 и группу 53 мультиплексоров.

Формирователь 28 интегральных характеристик модулярного кода является известным устройством конвейерного типа .3J, быстродействие которого составляет (Т+) такт при пропускной способности одна операция в один такт.

Блок 31 сдвига осуществляет деление входного числа на два и представляет собой известное устройство дня масщтабирования чисел t2,

Третий элемент 32 заде р;жкй представляет собой цепочку из (Т+З) последовательно соединенных регистров.

Формирователь 38 номера нормирующего коэффициента реализуется на основе постоянного запоминающего устройства. В его память по адресу Х+

0 1п&,

+2 записывается константа

-i:.-J5zLn М)

-L LJ-ogsl X

где S - основание характеристики (S

-2,4,8,16).; XelO,l,.,.,

обозначение ближайщего к действительному целого числа.

3

Блок 37 модульного умлизуется с помощью постонающих устройств, в 1-е ( ,2,.. . ,К)«по адресу писывается константа

У|Нх,-5. 1

),

x.,l,...,nii-li, ,i,...,K

Схема 16 сравнения на своем выходе вырабатывает единичный сигнал, если Х7У, где X и У- - величины, подающиеся соответственно на первый и второй входы схемы 16 сравнения,.

Первый элемент 22 задержки предстляет собой цепочку из (2Т+9) последовательно соединенных регистров, вход первого из которых является входом, а вькод последнего - выходом первого элемента 22 задержки.

Второй элемент 24 задержки представляет собой цепочку из (Т+3) последовательно соединенных регистров.

Блок 25 масштабирования чисел пре ставляет собой известное устройство конвейерного типа 2, быстродействие которого составляет такто при пропускной способности одна операция масштабирования в один такт. Блок 25 масштабирования чисел осуществляет деление входного числа AeD, заданного модулярным кодом, на константу Sjj где 1 - номер масштаба. Результатом указанной операции является модулярный код числа Aj, являющегося некоторым приближением величины A/S р,

D -тМ|,.,,..,1пМ.,-1),

где m р...,m - основания модулярной

системы счисления, являющие попарно простыми числами; - вспомогательный модуль, выбираемый из условий mi.7/2m+

1 , f-i К:-2; m7, К-1 т,

Блок 30 вычисления интервального индекса числа служит для определения по модулярному коду (с/, ,... ,о(ц) числа А машинного интервального индекса по формуле

к-1 (м. -of.imiuHri- ;

(2)

tт..

,.тк где ..Ут ;.

Блок 30 реализован так, как это описано в t П,.

Блок 29 формирования признака аддитивного переполнения определяет величину реализован и работает так, как это описано 4.Блок 35 задержки состоит из двух элементов задержки на два и один такт соответственно. Вход и выход первого из элементов задержки являются соответственно первыми входом к выходом блока 35 задержки. Вход и выход второго элемента задержки являются соответственно вторыми входом и выходом блока 35 задержки.

Формирователь 34 порядка результата реализуется на основе постоянного запоминающего устройства. В его память по адресу

.l4c..

записывается набор констант i f , Q7,

.-ii где V

если О) 1; если U)0,

v -i ,

- г 1 J если -fi -q, il.

to, если

-д зо

ся

{-4i 1 - диапазон изменения порядков операндов.

Устройство осуществляет алгебраическое сложение (сложение или вычитание) чисел (a)s v{a), (Ъ), kj(b) j представленных в форме с плавающей запятой, где и(а)А/М (Ъ). ВА1 - мантиссы, (а) и ){Ъ) - порядки операндов а и Ъ соответственно, 40 .,.

, Устройство работает следующим образом.

Для определенности допустим, что (а.}т(ъ , По сигналу, подаваемому с установочного входа 3 в блок 9 синхронизации, в младший разряд регистра 46 сдвига записывается единица второй триггер 49 посредством злемента ИЛИ 48 устанавливается в единичное состояние, а первый триггер 45 - в нулевое состояние (фиг. 2)з тем самым устройство приводится в исходное рабочее состояние. Когда Г вида операции, подлежаш 1й вьшолнению, с входа 2 устройства подается на единичный вход первого триггера 45, который ус- танавливается в единичное состояние.

Если , то по сигналу, подаваемому со входа 1 запуска на управляю45

50

55

5lA

щкй вход блока 10 элементов запрета; управляющие входы приема кода регистра 14 мантиссы первого операнда, регистра 12 порядка первого операнр,а, регистра 13 порядка второго операнда и в блоке 9 синхронизац 1И на второй вход элемента И 47 в нулевой вход второго триггера 49, второй триггер 49 обнуляется, на первом выходе бхю- ка 9 синхронизации вырабатывается сигнал 6,lj подаваемый на управляющий вход приема кода регистра 15 мантиссЬ второго операнда,

В регистры 14 и 15 мантисс первого и второго операндов соответственно с входов 5 и 6 устройства прини- маются соответственно модулярные коды (с/. J,, , з .к) числителя А У антиссы .( а) н (ft. 5.з/Э(,.) числителя в мантиссы ({Ъ), в регистр 12 порядка первого операнда и регистр. 13 порядка }зторого операнда входов 7 и 8 устройства принима отся двоич1а е коды порядков --j(a) первого операнда .и, v(b второго операнда соответственно и после этого начинается первый такт работы устройства.

На каждом такте работы устройства по сигналуэ подаваемому с тактового входа 4 устройства в блок 9 синхронизации ,. содерждаюе регистра 46 сдвига (фигс, 2) сдзиг ается на один бит в (сторону старших разрядов, при этом :во второй триггер 49 записывается единипй посредством элемента ИЛИ 48s когда первый разряд регистра 46 сдви- т а принимает единичное значение.

На первом такте работы устройства модулярный код числа Б с выхода регистра 15 мантиссы второго операнда постзттает на. вход блока 1 1 формирования дополнительного кода, который получает модулярный код числа -В, подаваемый через блок 10 элементов запрета на информационный вход регистра 15 мантиссы второго операнда. Запись числа -В в регистр 15 мантиссы второго операнда происходит лишь -тог- да когда вьшолняемой операцией яв ряется вычитание, так как в этом случае на первом выходе. блока 9 синхронизации вырабатывается сигнал Гтодаваемьш на управляющий вход приема {кода регистра 15 мантиссы второго one анда; Одновременно с этим содержи- Иые регистров 1.2 и 13 порядков первого н второго операндов соответственно подаются соответственно на первый

7426

и второй входы cxet-fci 16 сравнения, на выходе которой формируется сигнал 6 1.

На втором такте сигнал ( 1 с выхода схемы 16 сравнения подается на управляющие входы блоков 17, 19, 20 и 36 мультиплексоров, в соответствии с чем модулярный код числа А с выхода

регистра 14 мантиссы первого операнда через второй вход блока 9 мультиплексоров поступает во второй элемент 24 задержки, модулярный код числа В (символ означает + или -) с выхо5 да регистра 15 мантиссы второго операнда через второй ин1|)ормационный вход 8 блока 20 мультиплексоров - на первый вход блока 25 масштабирования чисел, содержимое регистра 12 порядQ ка первого операнда через второй информационный вход блока 17 мультиплексоров - на вход первого элемента 22 задержки и первый вход вычитателя 23 порядков, содержимое регистра 13 по5 рядка второго операнда через второй информационный вход блока 36 мультиплексоров - на второй вход вычитателя 23 порядков, на выходе которого сформируется величина V л(а)-v4 b) , пере0 дающаяся на второй вход блока 25 масштабирования чисел, где со следующего такта начинается масщтабирование числа В на константу S.

На (Т+б)-м такте работы устройства

j.. модулярные коды чисел А с выхода второго элемента 24 задержки и В с выхода блока 25 масштабирования чисел поступают соответственно на второй и первый входы блока 2I модульных сумп маторов, который находит модулярный код.числа , передающийся во вспомогательный регистр 26, Так как на данном такте на управляющий вход блока 27 мультиплексоров с третьего выхода блока 9 синхронизации подается сигнал (), то модулярньш код числа с выхода блока 25 масштабирования чисел через первый информационный вход блока 27 мультиплексоров передается в блок 30 вычисления интер - вального индекса числа, где в течение очередных Т тактов, считая текущий, в соответствии с (2) вычисляется машинный интервальный индекс l ( В) числа .

На (Т+7)-м такте работы на управляющий вход блока 27 мультиплексоров с третьего выхода блока 9 синхронизации подается/ сигнал , 1, поэтому мо5

0

5

114

дулярный код числа А с выхода второго элемента 24 задержки через второй информационный вход блока 27 мультиплексоров передается в блок 30 вычисления интервального индекса числа для вычисления машинного интервального индекса Т(А) числа, модулярный код числа С с выхода вспомогательного регистра 26 подается на вход формирователя 28 интегральных характеристик модулярного КОД4, который начинает вычисление поправки Амербаева б(С) и коэффициентов симметрического полиадического кода числа С. Одновременно с этим на (Т+7)-м такте модулярные коды числа А с выхода второго элемента 24 задержки и В с выхода блока 25 масштабирования чисел подаются соответственно на первый и второй информационные входы блока 29 формирова- ния признака аддитивного переполнения, который начинает формирование величины 51.

На (Т+8)-м такте модулярный код С с выхода вспомогательного регистра 26 передается на входы блока 31 сдвига и третьего элемента 32 задержки. . Блок 31 сдвига начинает вычисление числа с 1с/21.

На (2Т+6)-м такте работы устрой- ства с второго выхода блока 9 синхронизации на управляющий вход блока 29 формирования признака аддитивного переполнения подается сигнал 6j 1, благодаря чему величина Я сформированная в данном блоке, суммируется с величиной l( в) , поступившей через третий информационный вход блока 29 формирования признака аддитивного переполнения с выхода блока 30 вычисления интервального индекса числа и получается вычет Я+1(В) .

На (2Т+7)-м такте работы устройства с второго выхода блока 9 синхронизации на управляющий вход блока 29 формирования признака аддитивного переполнения передается сигнал ,, благодаря чему полученный вычет суммируется в данном блоке с величиной 1(Л), поступившей с выхода блока 30 вычисления интервального индекса числа, и получается вычет

1 1Л+1(А)+1(В)|,.

На (2Т+8)-м такте работы устройства формирователь 28 интегральных характеристик модулярного кода завершает формирование поправки Амербае1742

ва и коэффициентов симметрического полиадического кода. При этом поправка Амербаева с выхода формирователя 28 интегральных характеристик модулярного кода через четвертый информационный вход подается в блок 29 формирования признака аддитивного переполнения, гд по ней и вычету l формируется признак аддитивного переполнения fl , который передается с выхода.блока 29 формирования признака аддитивного переполнения на первый вход блока 35 задержки..

5

0

5

0

5

На (2Т+9)-м такте работы устройства коэффициенты симметрического полиадического кода с выходов формирователя 28 интегральных характеристик модулярного кода подаются на входы блока 33 анализа полиадического кода, KOTopbrfi на первом и втором своих выходах формирует старший ненулевой коэффициент симметрического полиадического кода Х| и его номер 1 соответственно, при этом знаковый (старший) бит коэффициента Х-р передается на второй вход блока 35 задержки, а чис ла Xр и 1 соответственно получают на первый и второй входы формирователя 38 номера нормирующего коэффициента, который на (2Т+10)-м такте работы устройства на своем выходе формирует величину l (см. (1)).

На заключительном (2Т+11)-м такте величина )(а) с выхода первого элемента 22 задержки поступает на перг . вый вход формирователя 34 порядка ре- зультата, на второй и третий входы

Q которого/поступают соответственно величины 1 с выхода формирователя 38 номера нормирующего коэффициента и ЯслС первого выхода блока 35 задержки. Кроме того, величина l с вьпсода форg мирователя 38 номера нормирующего коэффициента подается на второй вход блока 37 модульного умножения, на первый вход которого с выхода тре- тьега элемента 32 задержки поступает

Q величина С. Блок 37 модульного умножения находит модулярный код величиЛ р1

ны , который поступает на первый информационный вход блока 18 мультиплексоров, на 1второй информа- g ционный вход которого с выхода блока 31 сдвига подается величина С с/2. На управляющий вход блока 18 мультиплексоров подается сигнал Л.с,дС первого выхода блока 35 задержки.

В зависимости от значения величины SI., на первом выходе формирователя 34

ил

лорядаа результата и выходе блока 18 мультиплексоров формируются соответствующие значения порядка результата и числителя нормализованной мантиссы результата, Еспи , на вь1ходе 44 мантиссы-результата и выходе 41 порядка результата устройства, полу- чают соответственно величины Сд и л)(а) + 1, а при 0 - величины С и Да)-1 , ,

На BtopOM выходе формирователя 34 порядка результата формируется при- знак переполнения, который может быть считан посредством выхода 42 переполнения устройства.На знаковый выход. 43 с второго выхода блока 35 задержк

.передается знак результата, а на выкода 40 появляется сигнал окончания

.операции сложения чисел.

На выходе 39 гото вности единица появляется на втором такте. Это озрегистра мантиссы второго-операнда, входы порядков первого и второго операндов устройства соединены соответственно с информационными входами регистров порядка первого и второго операндов, входы разрешения приема которых объединены и соединены с входом разрешения приема регистра мантиссы первого операнда и с входом запуска устройства, выходы регистров порядка второго и первого операндов соединены соответственно с первым и вторым информационными входами первого блока мультиплексоров, выход которого соединен с входом первого элемента задержки, выход которого соединен с первым входом формирователя порядка результата, выход порядка -которого является выходом порядка результата устройства,- выходы блока модульного умножения и блока сдвига соединены соответственно с первым и вторым информационными -входами второго блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| УСТРОЙСТВО ДЛЯ МАСШТАБИРОВАНИЯ ЧИСЛА В МОДУЛЯРНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 2002 |

|

RU2246753C2 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

Изобретение относится к вычислительной технике и предназначено для использования в арифметических устройствах с плавающей запятой, функционирующих в модулярной системе счисления.. Целью изобретения является расширение области применения за счет работы в модулярной системе счисления. Поставленная цель достигается тем, что устройство для сложения и вычитания чисел с плавающей запятой, содержащее регистры 12 и 13 порядков первого и второго операндов, регистры 14 и 15 мантисс первого и второго операндов, блок 11 формирования Д9полнительного кода, вспомогательный регистр 26, вычитатель 23 порядков, блок 25 масштабирования, блок 21 модульных сумматоров, блок 31 сдвига, формирователь 34 порядка результата, элементы 22 и 24 задержкиj блок 29 форшгрования признака аддитивного переполненияJ блок 37 модульного умножения, блоки 17-20 мультиплексоров и блок 33 анализа полиадического кода, содержит блок 9 синхронизации, блок 10 элементов запрета схему 16 сравнения, блоки 27 и 36 мультиплексоров, формирователь 28 интегральных характеристик модулярного кода, блок 30 вычисления интервального индекса числа, формирователь 38 номера нормирующего коэффициента, блок 35 задержки, элемент 32 задержки с соответствующими связями. 5 ил, ,„- „vJf 5 W « tasGib , HsJ, CICrCAW

начает, ч-го, начиная с указанного мо- 25 мультиплексоров, вьгкод которого являмента времени,в устройстве может быть инициирована; новая операция сложения чисел. Таким образом, при работе устройства в условиях максимальной загрузки его пропускная способность составляет одну операцию не более чем в два такта,.

Формула изобретения

Устройство для сложения и вычитания чисел с плавающей запятой, содержащее регистр мантиссы первого операнда, регистр мантиссы второго операнда, регистр порядка первого операнда, регистр порядка второго операнда, блок формирования дополнительного кода, вспомогательный регистр, вычитатель порядков, блок масштабирования чисел, блок модульных сумматоров, блок сдвига, блок формирования признака аддитивного переполнения, формирователь порядка результата, два элемента задержки, блок модульного умножения, четыре блока мультиплексоров и блок анализа полиадического кода, содержащий К (К - количество оснований системы счисления) элементов ИЛИ, К-1 элемент И и шифратор, причем входы мантисс первого и второго операндов устройства соединены соответственно с информационным входом регистра мантиссы первого операнда,и с установочным входом

0

5

0

ется выходом мантиссы результата устройства, выход регистра мантиссы второго операнда соединен с входом блока формирования дополнительного кода и с первым информационным входом третье™ го блока мультиплексоров, второй информационный вход которого соединен с выходом регистра мантиссы первого операнда и с первым информационным входом четвертого блока мультиплексо-: ров, второй информационный вход которого соединен с выходом регистра мантиссы второго операнда, выходы четвертого блока мультиплексоров и вычи- тателя порядков соединены соответственно с информационным входом и с входом номера масштаба блока масштабирования, выход третьего блока мультиплексоров соединен с входом вто-

g рого элемента задержки, выход которого соединен с первым информационным входом блока формирования признака аддитивного переполнения и с входом первого слагаемого блока модульных

Q сумматоров, выход которого соединен с входом вспомогательного регистра выход которого соединен с входом бло- ка сдвига, выход блока масштабирования чисел соединен с вторым информаg ционным входом блока формирования

признака аддитивного переполнения и . с входом второго слагаемого блока модульных сумматоров, причем в блоке анализа полиадического кода 1-й вход

U

1-гр элемента И (,...,l, ,,.., К-1) соединен с инверсным выходом i-ro элемента ИЛИ, (1+1)-й вход 1-го элемента И соединен с прямым выходом ()-го элемента ИЛИ, прямой выход первого элемента ИЛИ и выходы элементов И с первого по (К-1)-й соединены соответственно с входами шифратора,- отличающеес.я тем, что, с целью расширения области применения за счет работы в модулярной системе счисления, оно содержит блок синхронизации, блок элементов запрета, схему сравнения, пятый и шестой блоки мультиплексоров, формирователь интегральных характеристик модулярного кода, блок вычисления интервального индекса числа. Формирователь номера нормирующего коэффициента, блок задержки и третий элемент задержки, причем блок анализа полиадического кода дополнительно содержит группу мультиплексоров, причем входы запуска и вида операции устройства, установочный и тактовый входы устройства соединены соответственно с входами запуска, режима, установки и тактовым входом блока синхронизации первый вьгход которого соединен с входом разрешения приема регистра мантиссы второго операнда, информационный вход которого соединен с выходом блока элементов запрета, информационный и управляющий входы которого соединены соответственно с выходом блока формирования дополнительного кода и с входом запуска устройства, выходы регистров порядка первого и второго операндов соединены соответственно с первым и вторым входами схемы сравнения, вьгход которой соединен с управляющими входами первого, третьего и четвертого блоков мультипле ксо- ров, выходы блока масштабирования чисел и второго элемента задержки со.е- динены соответственно с первым и вторым информационными входами пятого блока мультиплексоров, выход которого соединен с входом блока вычисления интервального индекса числа, выход которого соединен с третьим информационным входом блока формирования признака аддитивного переполнения, вход задания режима которого соединен с вторым выходом блока синхронизации, третий, четвертый и пятый выходы ко21 2

торого соединены соответственно с управляющим входом пятого блока мультиплексоров, с входами готовности и окончания работы устройства, входы уменьшаемого и вычитаемого вычитате- ля порядков соединены соответственно с выходами первого и шестого блоков мультиплексоров, первый и второй информационные и управляющий вход шестого блока мультиплексоров Соединены соответственно с выходами регистров порядка первого и второго операндов и с выходом схемы сравнения, выход вспомогательного регистра соединен с входами третьего элемента задержки и формирователя интегральных характеристик модулярного кода, выход поправки Амердаева которого сое-

динен с четвертым входом блока формирования признака аддитивного переполнения, выход которого соединен с первым входом блока задержки, выходы коэффициентов полиадического кода формирователя интегральных характеристик модулярного кода соединены соответственно с входами элементов ИЛИ блока анализа полиадического кода; вьгход старшего r,шьтиплeкcopa группы которого соединен с вторым входом блока задержки, выходы гультиплексо-- ров группыS кроме старшего, и выход шифратора блока анализа полиадического кода соединены соответственно с

первьш и вторым входами формирователя номера нормирующего коэффициента, выход третьего элемента задержки соеди- нен с входом первого сомножителя блока модульного умножения, вход второго

сомножителя которого соединен с выходом формирователя номера нормирующего коэффициента и с вторым входом формирователя порядка результата, выход переполнения которого является

выходом переполнения устройства, первый выход блока задержки соединен с управляюш -1м входом второго блока мультиплексоров и с третьим входом формирователя порядка результата, второй

выход блока задерзйки является знаковым выходом устройства, причем в блоке анализа полиадического кода выход шифратора соединен с управляюш ми входами мультиплексоров группы, информационные входы которых соединены с входами соответствующих элементов ИЛИ.

Ри,2.Ъ

1411742

Номера.

тактоб 1 2 3 S 6 1 8 Э Ю п 12 J3 J 5 16 ,17

Авторы

Даты

1988-07-23—Публикация

1986-06-13—Подача