2. Модущ. по п. 1, о т п и ч а ю щи и с я тем, что каждый продессор ный блок содерокит две группы элементов ассвяшативной памяти, сумматор, триггер переноса, три элемента И и элемент ИЛИ, выход которого соединен с входами разрешения золиси элементов ассоциативной памяти Первой и второй

групп. Екрды разрешения чтения которых подключены к выходу пербого элемента И, входы опроса и зеотиси элементов ассоциативной памяти первой и второй ГРЭТ1П соединены с соответствующими входами опроса и записи блока, выходы элементов ассоциативной памяти перВбя и второй группподключены к первому и второму входам сумматора, третий

вход которого соединен с выходом триггера переноса, прямой и инверсный выходы переноса сумматора подключены к входам установки и сброса триггера переноса, выход прямой суммы сумматора соединен с первыми входами Первого и второго элементов И, а инверсной .суммзи сумматора подключен к первому входу третьего элемента И, вторые входы пе рвого и третьего элементов И соединены соответственно с входом чтения, вкодом прямой записи и вводом инверсной записи блока, при этом первый и второй входы элемента ИЛИ подключены к выходам соответственно второго и третьего элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Система коммутации | 1985 |

|

SU1317449A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативный процессорный элемент | 1980 |

|

SU879593A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для вычисления свертки | 1990 |

|

SU1709342A1 |

| Устройство для выделения среднего из нечетного количества чисел | 1988 |

|

SU1647554A1 |

| Устройство для считывания информации из ассоциативной памяти большого объема | 1988 |

|

SU1631607A1 |

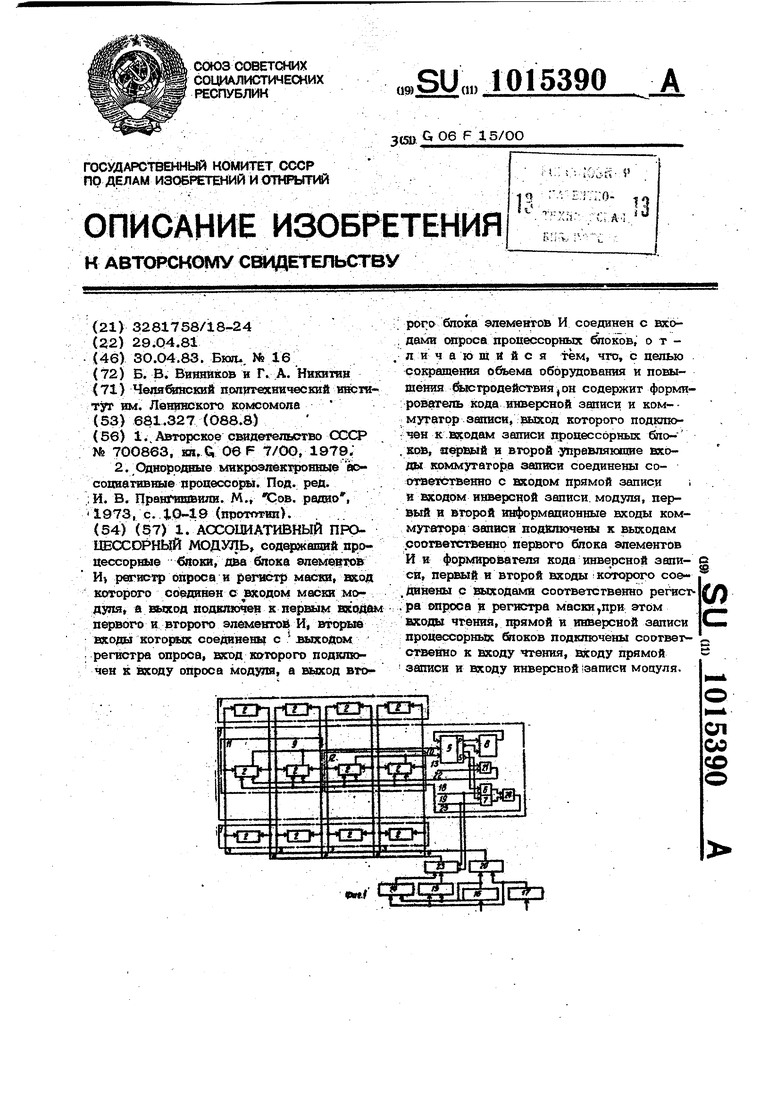

1. АССОЦИАТИВНЫЙ ПРОгШССОРНЬШ МОДУЛЬ еодаржапшй процессорные бйоки,Д1ва блока эпемевтозв И регисмр опроса и регистр масхи, вкод EOfToporo соединен счюсодом маски модуля а выход подвяктв к первым первого и второго эпеметп в И, входы которых соединены с выходом регистра опроса, вход которого подкшочен к восоду опроса модзтю, а выход вто; рога блока элементов И соединен с вхЬ. дами (шроса процессорных йтоков, о т , л и ч а ю щ и и с я тем, чго, с со1фашения объема оббруцования и повышения & стродействия, он содержит формирователь кода инверсной записи и коммутатрр записи, выход которого подклюг н к вкодам записи процессорных uto, ков, первый и второй управляющие ввсоДЫ коммутатора зешиси соединены соответственно с входом прямой записи ; и входом инверсной записи, модуля, первый и второй информвдионные входы коммутатора аапж;н подключены к выходам соответственно первого блока элементов И и формирователя кода инверсной запи- о си, первый и второй входы i которого со&- (Л ,динены с выходами соответственно регбист. ра опроса и регистра маски при этом вкоди чтения, и инверсной записи процессорных блоков подключены соответственно к входу чтения, входу прямой записи и ЕКОДУ инверсной записи модуля ел 00 со

- - . ;,;.

Изобретеш{е относится к вычислительной технике в может быть использовано при построении параллельных процессоров и о анородных выткшительных систем, предназначенных для групповой обработки информации ассоциативным способом.

Известен ассоциативный процессорный модуль, содержащий процессорные блоки, состоящие из двух групп еаементов ассоциативной памяти с воа ожностью записи прямого и инверснога кода fll

Наиболее близким к предлагаемому по технической сущности является ассоциативный процессорный модупь, представ ляюший собой совокупность процессорных блоков,построенных на однс азрядных элементах асссЯ1иаФквной яамяти. При этом информационные входы сароса и записи элементов одноименных объединены о&шмй шинами опроса и записи, подключенныии к входному устройству, сосгтояшему, например, из регистров опроса и маски формиррватепя кодов опроса И записи 23 .

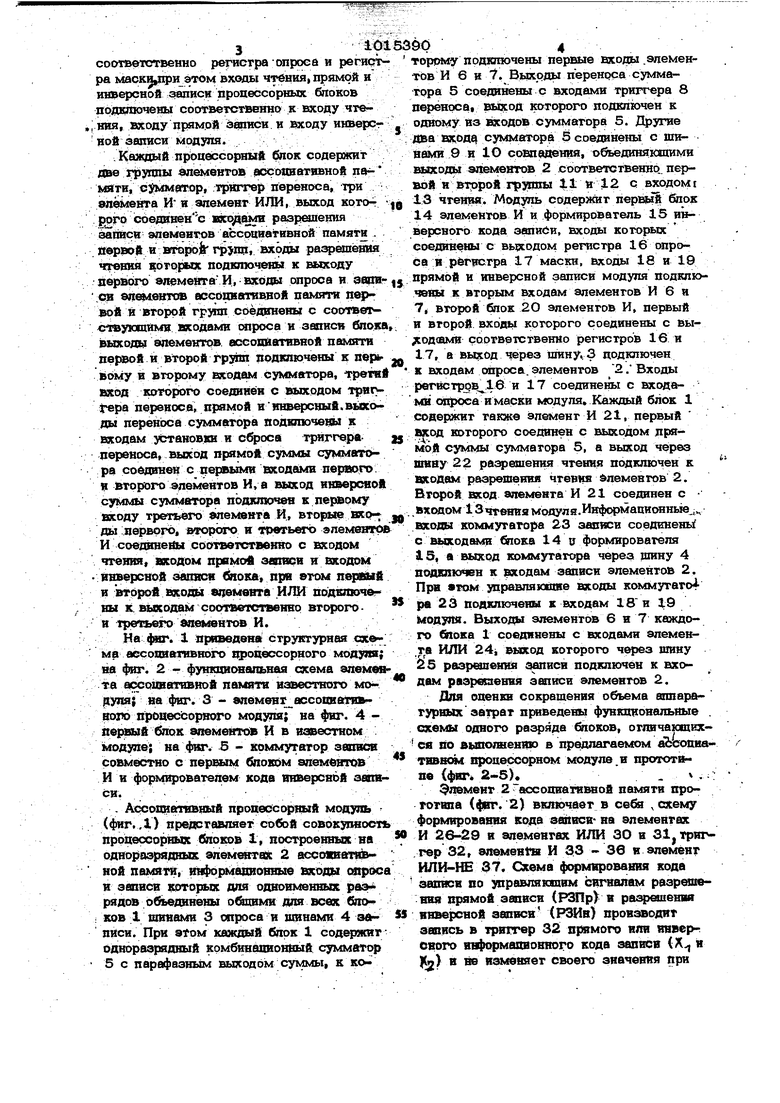

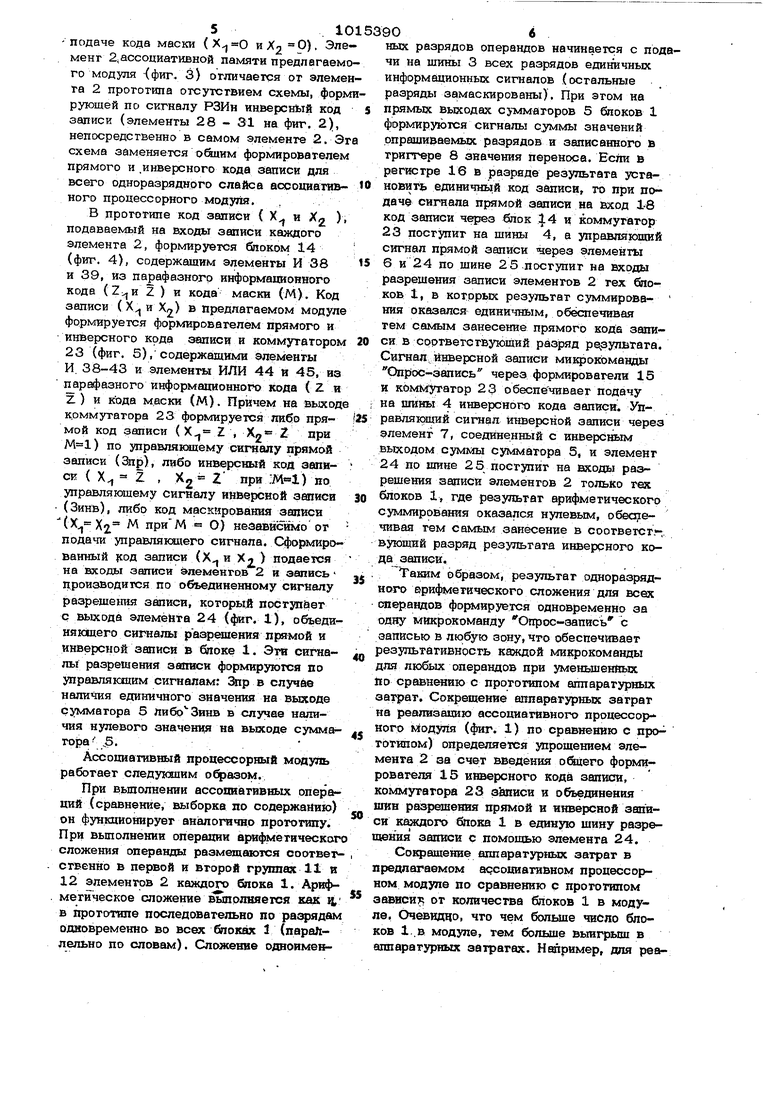

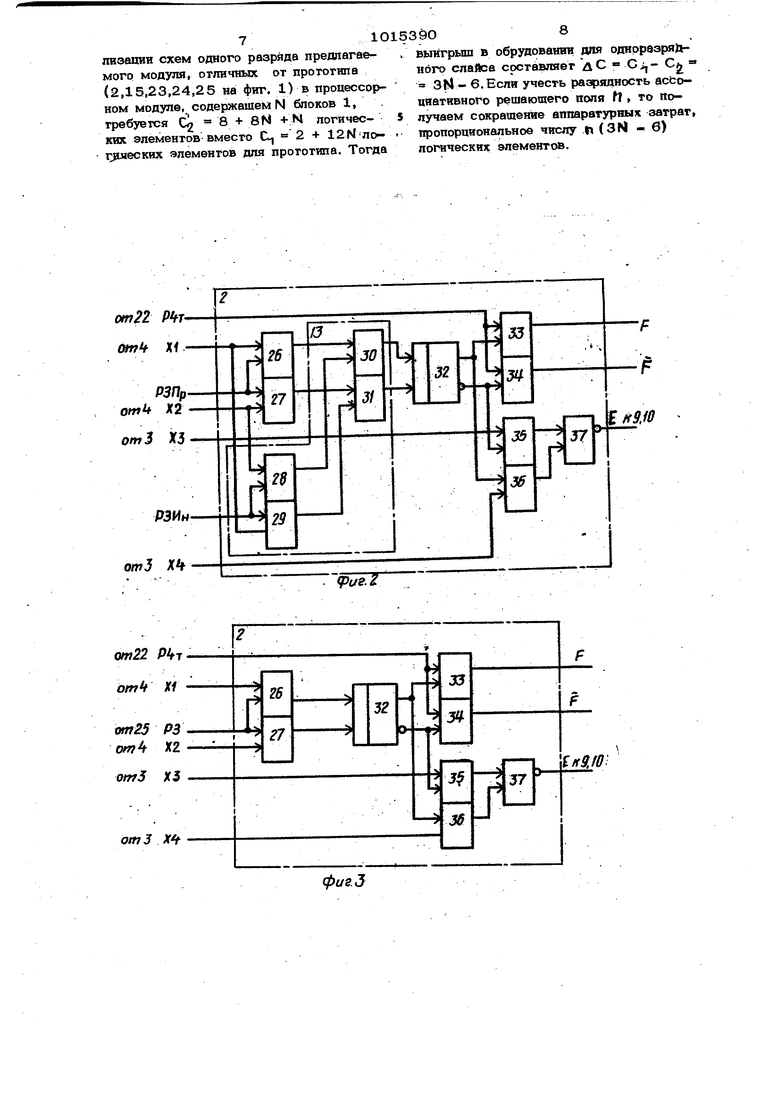

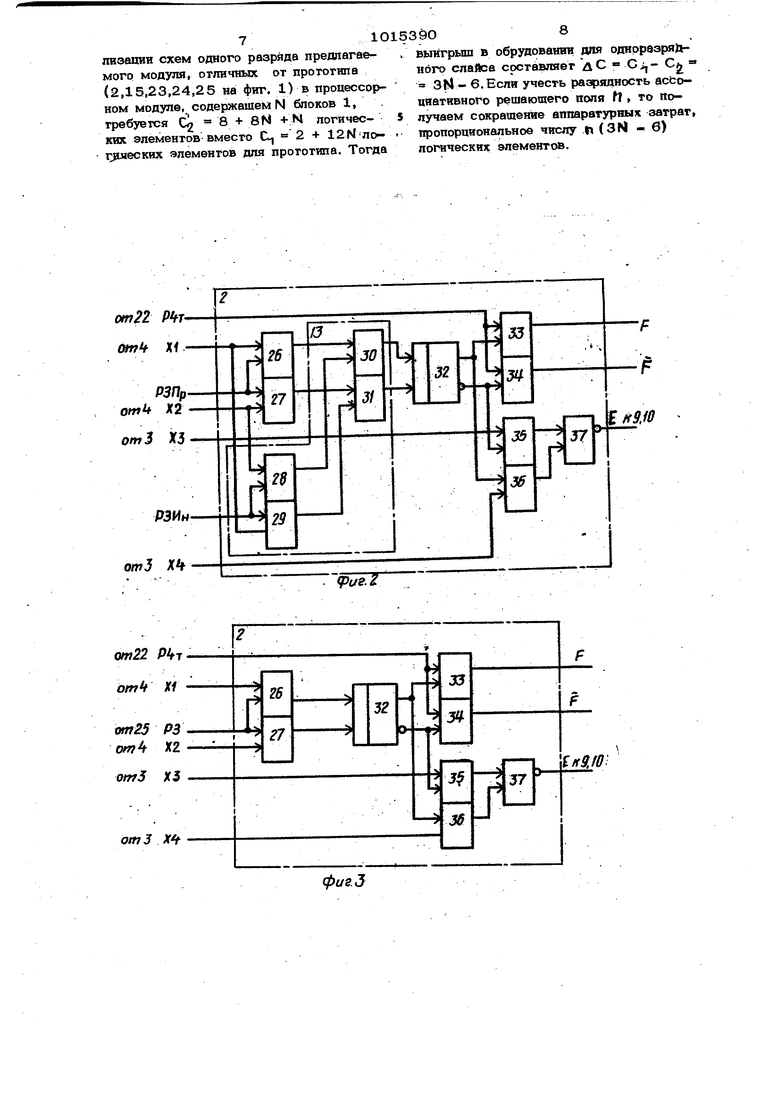

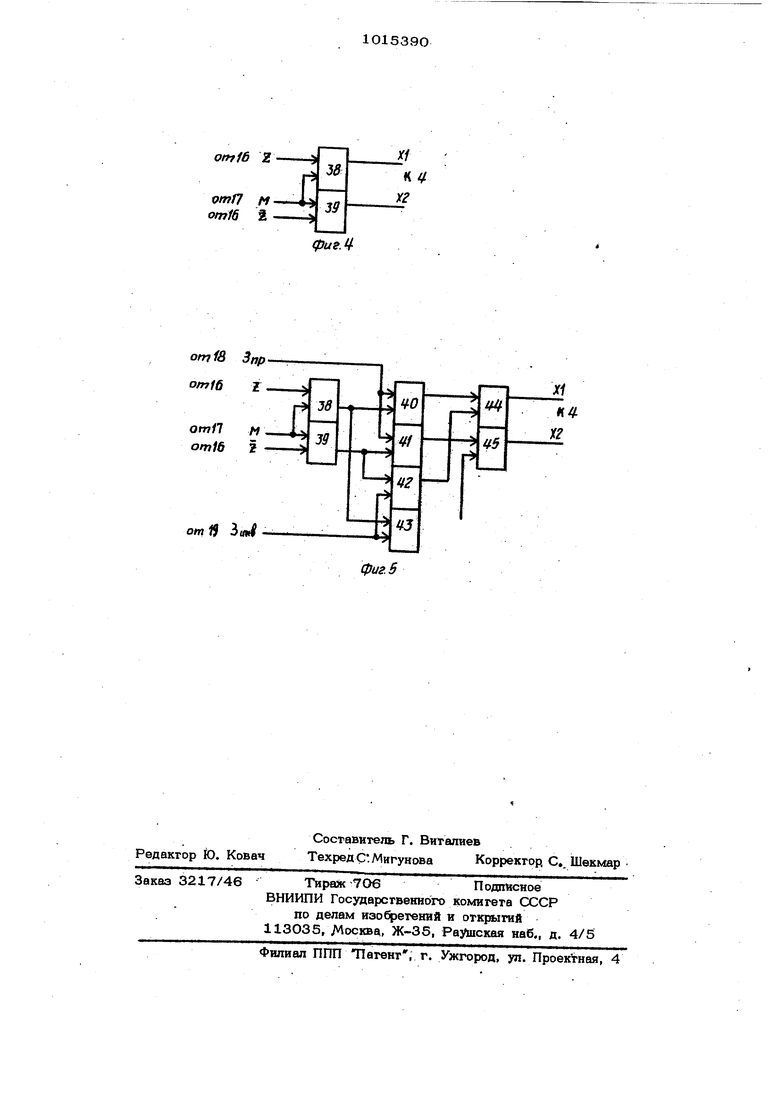

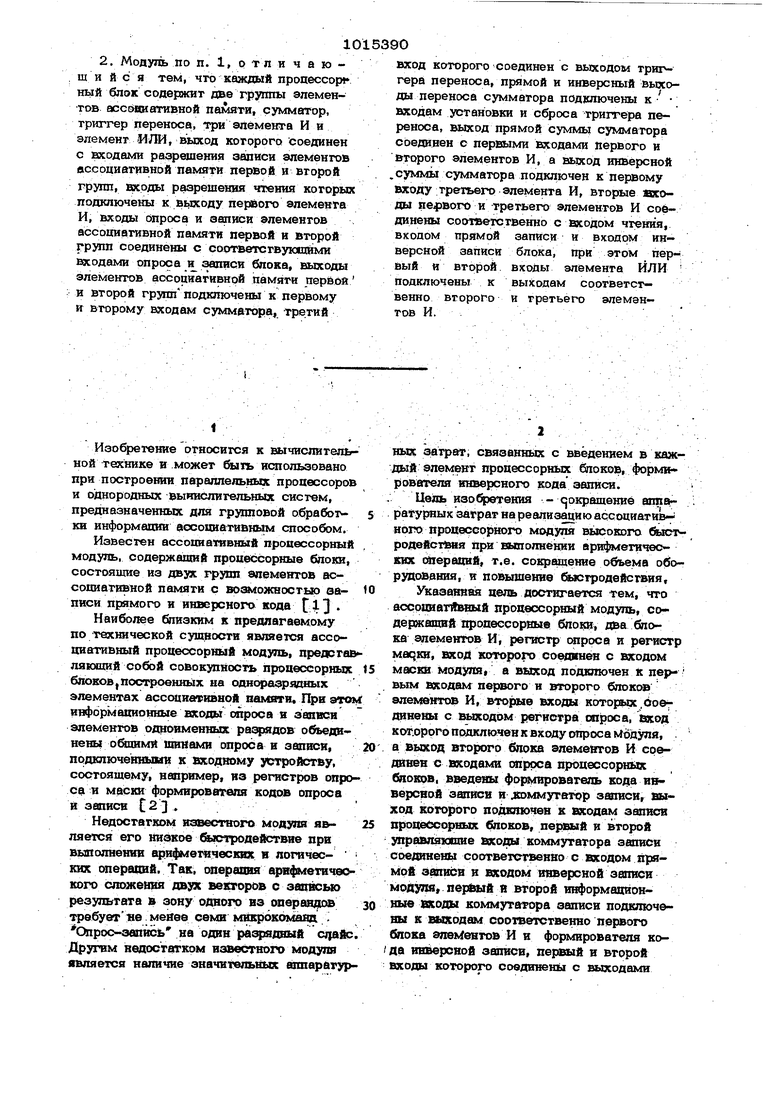

Недостатком известного модуля является его низкое СЬстродействие про выполнении арифметических в логических оперЕЦшй. Так, операция арнфметичео кого сложетга двух вектор&в с заявсыо результата в зону ощюго на операндов требует яе мейае семи михрокомаяя . Опрос-запись на одвв ра фядяый Другим недостатком известного модуля шляется наличие значительных аппаратурых затрат, связанных с введением в кажый элемент процессорных блоков, формирователя инверсного кода записи. Цель изобретения - с окрашениё аплвратурных затрат на реализацию ассоциативт ного процессо{ ногт) модуля вьюокого быстродейст1айя при выполнении арифмети юских смерапий, т.е. сокреоцение объема оборудования, и повышение быстродействия. Указанная цель достигается тем, что ассоциативный процессорный модущ, содержашвй пропессорвые блоки, дваблока алемевтов И, регистр сшроса и регистр мацки, вход которого соединен с входом маски модупяг а выход подключен к первым ксодам первого и второго блоксв элементов И, вторые входы которьк.бое-динены с шходом регистра опроса, еасод кот.орого подключен к входу опроса Модуля, а выход второго блока элементов И соединен с входами опррса процессорных блоков, введены фо|п лфоватепь кода вяверсиой записи и коммутатор запвсиг выход которого подкшочев к входам записи процессорных блоков, и второй упршпякягае входы коммутатора заш1Си соединены соответстввиио с входом прямой записи и входом ииверсной записи модуля, первый и второй информацйоииые входы коммутатора записи подключены к выходам соответственио первого блока эяемГевтов И и формирователя кода ииверсиой записи, первый и второй входы которого соединены с выходами соотввгтственно регистра-опроса и региот pai маски пфи этом входы чтения, npsiMOJt и инверсной гэаписи процессорных блоков 11рдкто1чены соответственно к входу чте, НИИ, входу прямой записи и «ходу инверсг ной записи модуля. . Каждый процессорный блок содержит дае группы апементов ассоинатнвной па мяти, сумматор, триггер переноса, три апёмевта И и элемент ИЛИ, выход кото4 рого сЬе|Шнен:с псодшии разршхення записи эпэментовассрцивтивной памяти . Яврвой и Btapbir .пц, входы разрешёйм чтония которых подклю чеиы к выходу первого влемента.И.входы опроса и эеряг CSB длолентся ассопкативной памяти первой иВторой групп соедвпнены с соотввт- ствукхцйми ввсодами raipoca и зяхисн блока выхофа впемвктов. ассошепивной памтги первой и второй Групп подключены к перьВому и второму входам сумматора, третей вход которого соединен с ВЕЫХОДОМ тригГера переноса, прямой иинверсный.выходы п енЬса сумматора подвлючещл к входам установки и сброса триггер1апереноса, выход прямой суммы сумматора со шгаен с первыми вкодами перяюго ц второго элементов И, а выход инверсной суммы сумматора подключен к первому Екоду третьего «темента И, вторые вко-г ды: первого, втсрого w третьего элемещч И сое/шнейы соотве1«твекно с входом чтения f вкоДом прамой зшяси и входом «таверсной aaiiBCH блока, прв этом и второй коды аоемвнта ИЛИ поДшкхче иы к выходам соогтввггсггаенво второго и третьего Mei «BHToB И. На 4я1Г 1 приведена; структурная схема ассопяативного щзоцессорного модуяя| на фиг. 2 - функцнонсшьная схема злемен та а(Х 01Швтавной памяти нз1вестного мо дупя; на фиг. 3 - алемент ассоцввтвв ного процессорного на фиг, 4 (ок вавыеапл И в известном модуле; на фиг. 5 - коммутатор задавай совместно с первым блоком элементов И и формирователем кода тшерснбй зеггаСИ. /;-..: - . Асхгоциагтивный процессорщлй модуль (фиг.,},) представляет собой совокупность процессорных блоков 1, построенных на одно| Е13рядяых элементах 2 ассохвтчФной памяти, инфо|(ацвовные вкоды олроса к запвсн к тор1ЫХ для одноименных рагн рядов о(/шнены общими для всех блснков 1 шинами 3 опроса и шинами 4 писи. При этом кажлый блок 1 одноразрядный комбин шноншй сумматор 5 с парафазным выходом суммы, к коTopf «iy подключены первые входы .апементов И 6 и . Выходы переноса сумматора 5 соединены с входами триггера 8 переноса, вьщод которого подключен к одному из входов сумматора 5. Другие два входе сумматора 5 соединены с шинами 9 и 1О сошаяения, обьединяхсшими выходы элементов 2 соответственно., п }вой н второй грэяпы 11 н 12 с входом I 13чтения. Модуль содержит блок 14эяемеНтгов И и формирователь 15 инверсного кода запиСн, входы которых соедине11ы с вьрсодом регистра 16 опро са 11:р6г|1стра 17 маски, Входы 18 и 19 прямой и инверсной записи модуля подкл чены к вторым входам элементов И 6 и 7« второй блок 20 элементов И, первый и второй входы которого соединены с выдодвмн соответственно регистров 16 и а выход через йшну.,3 подключен к входам (шроса. элементов 2. Входы регйстррв 16 и 17 соединены с входамй 01фОса имаски модуля. Каждый блок 1 содержит также элемент И 21, первый вход которого соединен с шдходом лрямой суммы сумматора 5, а выход через швву 22 разрешения чтения подключен к входам разрешения чтения элементов 2. Второй вход алемента И 21 соединен с .входом 13чтения модуля.Информационные,, входы коммутатора 23 записи соединены с выходЕ «и Спока 14 и формирователя 3.5, а выход коммутатора через шнну 4 подключен к ркодам записи элементов 2. При атом управляющие входы коммутаторра 23 подключены к входам 19 модуля. Выходы элементов 6 н 7 каждого блока 1 соединены с входами элемен, ИЛИ 24i выход которого шину 25 разрешения записи подключен к входам раарегаения зшиюи элементов 2. Для опенки сокращения объема аппаратурных затрат п(1ведены функционсшьные . схемы одного разряда блоков, отличаюшвхсе По выпслвению в предлагаемом аЬсоцнатввшяд процессорном модуле,и праготян пе (фиг 2-5),- VЭлемент 2 ассоциативной памяти прототипа (4вг. 2) включает в себя .схему формирования кода заввсн-на элементах И 2в-:29 и алементах ИЛИ 30 и 31, триггер 32, элемента И 33 - Зв и элемент ИЛИ-1Ш 37. Схема формяроваввя кода записи по упршзляюшим С11гналам разрвиевия прямой записи ( в разрешенвя ннве|х:ной ааписв (РЗИв) пронзводят запись в триггер 32 или янверового вв|кфма1шонвого кода записв (Х и Tfn) в не лэмваяет своего значения при 10 -подаче кода маски ( ). Эпеменг 2iассоциативной памяти предлагаемо го модуля фиг. 3) огличаегся ог эпемен га 2 прогогшта отсутствием схемы, форм рующей по сигналу РЗИн инверсный код записи (элементы 28 - 31 на фиг. 2), непосредственно в самом элементе 2. Эт схема заменяется о&цим формирователем прямого и .инверсного кода записи для всего одноразрядного слайсв ассоциативно го процессорного мод утЛя. .. В прототипе код записи ( Х и Х2 ) подаваемый на входы записи каждого элемента 2, формируется блоком 14 (фиг. 4), содержащим элементы И 38 и 39, Из парафазного информащюнного кода ( Z) и кода маски (М). Код записи ( Х и Хя) в предлагаемом модуле формируется формирователем прямого и инверсного кода записи и коммутатором 23 (фиг. 5), содержащими элементы И. 38-43 и элеменил ИЛИ 44 и 45, из парафазного информационного кода ( Z и Z) и кода маски (М). Причем на выходе коммутатора 23 формируется либо прямой код записи ( Х Z , Х2 2 при ) по управляющему сигналу прямой записи (Зпр), либо инверсный код аеаяск ( Х Z , Х2 2 при ) по управляющему сигналу Ийверсной записи (Зинв), либо код маскирования записи ( М прнМ « О) HeaaBHcifiMo ог подачи управляющего сигнала. Сформированный код записи (Х и Xj ) подается на входы записи элементов 2 и запись производится по объединенному сигналу разреше1гая записи, который поступает с выхода элемента 24 (фиг. 1), обьединякшего сигналы разрешения прямой и инверсной записи в 1. Эти сигналы разрешения заггаси формируются по управляющим сигналам: Sip в случав единичного значения на выходе сумматора 5 ли& 3инв в случае наличия нулевого значен11я на вьосода сумматора j5. Ассоциативный процессорный мсздутш работает следукяиим образом. При вьшолнении ассоциативных операций (сравнение, выборка по содержанию) он функционирует ан)алоп1чнр прототипу. При выполнении операции арифметическог сложения операнды размешаются соответ. cfBeHHo в первой и второй группах 11 и 12 элементов 2 каждого блока 1. Ариф. метйческое сложение выполняется как it в прототипе последовательно по разрядам одновременно во всех блоках 3 (параллельно по словам). Сложение однонмевн 0 ных разрядов операндов начинается с подачи на шины 3 всех разрядов единичных информационных сигналов (остальные разряды замаскированы). При этом на прямых выходах сумматоров 5 блоков 1 формируются сигналы суммы значений рпрашиваемьвс разрядов и записанного в триггере 8 значения переноса. Если в регистре 16 в разряде результата установить единичный код записи, то при подаче сигнала прямой записи на вход 1-8 код записи через блок 14 и коммутатор 23поступит на шины 4, а управляющий сигнал прямой записи через элементы 6 и 24 по шине 25 поступит на входы разрешения записи элементов 2 тех блоков 1, в котррьк результат суммирования оказался единичным, обеспечивая тем самым занесение прямого кода записи в соответствующий разряд ре зутштата. Сигнал, инверсной записи микрокоманды Опргос-запись через формирователи 15 и комкгутатор 23 обеспечивает подачу на шины 4 И1шерсного кода записи. Управляющий сигнал инверсной записи через элемент 7, соединенный с инверсным выходом суммы сумматора 5, и элемент 24по шине 2 5 поступит на входы разрешения записи элементов 2 только тех. блоков 1, где результат арифметического суммирования оказался нулевым, обесз ечивая там самым занесение в соответст.-, вуюший разряд рез 71ьтата инверсного кода записи. Таким образом, результат одноразрядного врифметического сложения для всех (Я1ерандов формируется одновременно за одну микрокоманду Опрос-запись с записью в любую зону, что обеспечивает результативность каждой микроном авды для любых операндов при уменьшенньа iio сравнению с прототипом аппаратурных затрат. Сокрешение аппаратурных затрат на реализацию ассоциативного процессорного модуля (фиг. 1) по сравнению с прототипом) определяется укрощением элемента 2 за счет введения общего формирователя 15 инверсного кода записи, коммутатора 23 записи и объединения шин разрешения прямой и инверсной записи кюкдого блока 1 в единую шину разрепшния записи с помощью элемента 24. Со1фашение аппаратурных затрат в предлагаемом ассоциативном процессорном мояупв по сравнению с прототипом завнсит от количества блоков 1 в модуле, Очевидно, что чем больше число блоков 1 .в модуле, тем больше вьшгрьши в аппаратурных затратах. Назпример, для peaлвзапив схем одного разряда предлагаемого модуля, отличных от прототипа (2,15,23,24,25 на фиг. 1) в процессорном модуле, содержащем N блоков 1, требуется Q + 8N +N логических элементов вместо СЦ 2 + 12lJ-nc грнеских элементов для прототипа. Тогда

фиг.З

выигрыш в обрудованив дпя однррвзря)нбго слайса составляет дС Cg - 6. Если учесть разрядность ассоциативного решающего поля f1 , то получаем сокращение аппаратурных затрат, пропорциональное числу .| (ЗМ - б) логических элементов.

рие

от 16 Z

ОЛ7/7

Af--4-j

omf6 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Однородеоле микроэлек фонвые аосоднативные процессоры | |||

| Под | |||

| ред | |||

| ;И | |||

| В | |||

| ПрвнГшц&ияв | |||

| М., Сов | |||

| радар, 1973, с | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1983-04-30—Публикация

1981-04-29—Подача