Изобретение относится к вычислительной технике и (Оюжет быть использовано для цифровой обработки двумерных массивов, данных в реальном масштабе времени, в частности растровых изображений.

Наиболее близким к предлагаемому является устройство для цифровой двумерной свертки, предназначенное для вычисления рекурсивнойдвумерной свертки, содержащее блоки памяти коэффициентпо

Однако в этом устройстве смена коэффициентов не может быть выполнена в реальном времени, в результате чего невозможна оперативная смена формы ядра свертки непосредственно в процессе работы.

Цель изобретения - расширение функциональных возможностей за счет формирования массива коэффициентов различной пространственной конфигурации, в реальном масштабе временив

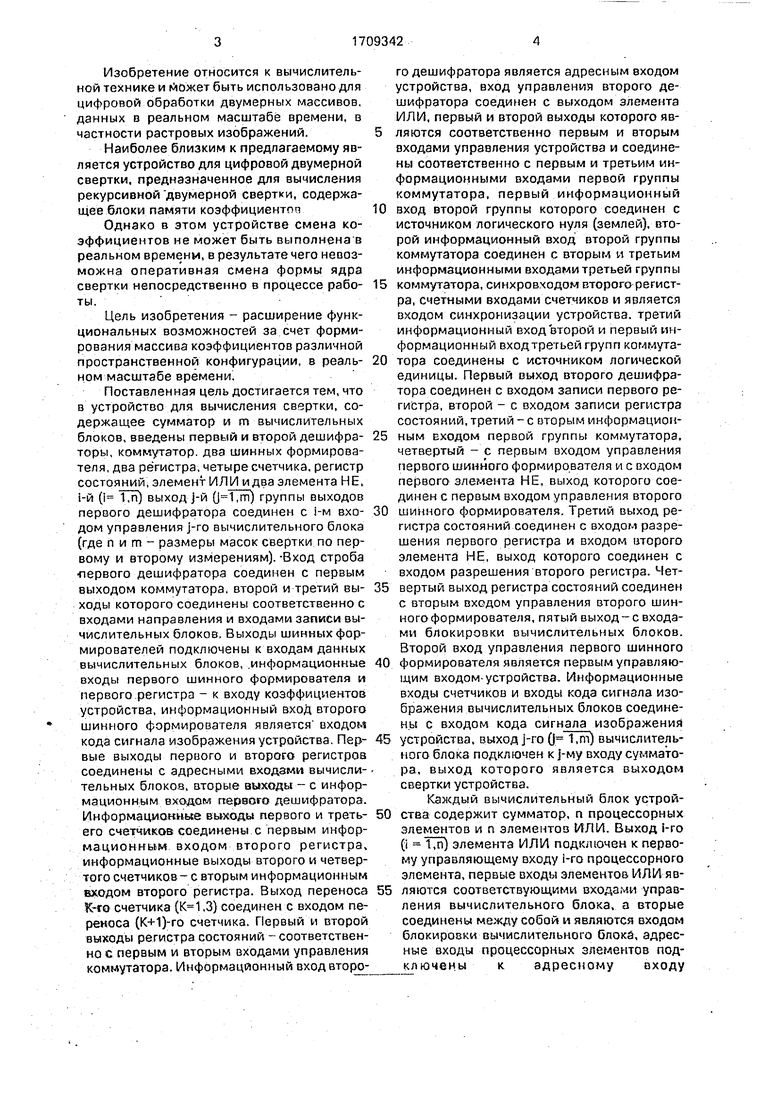

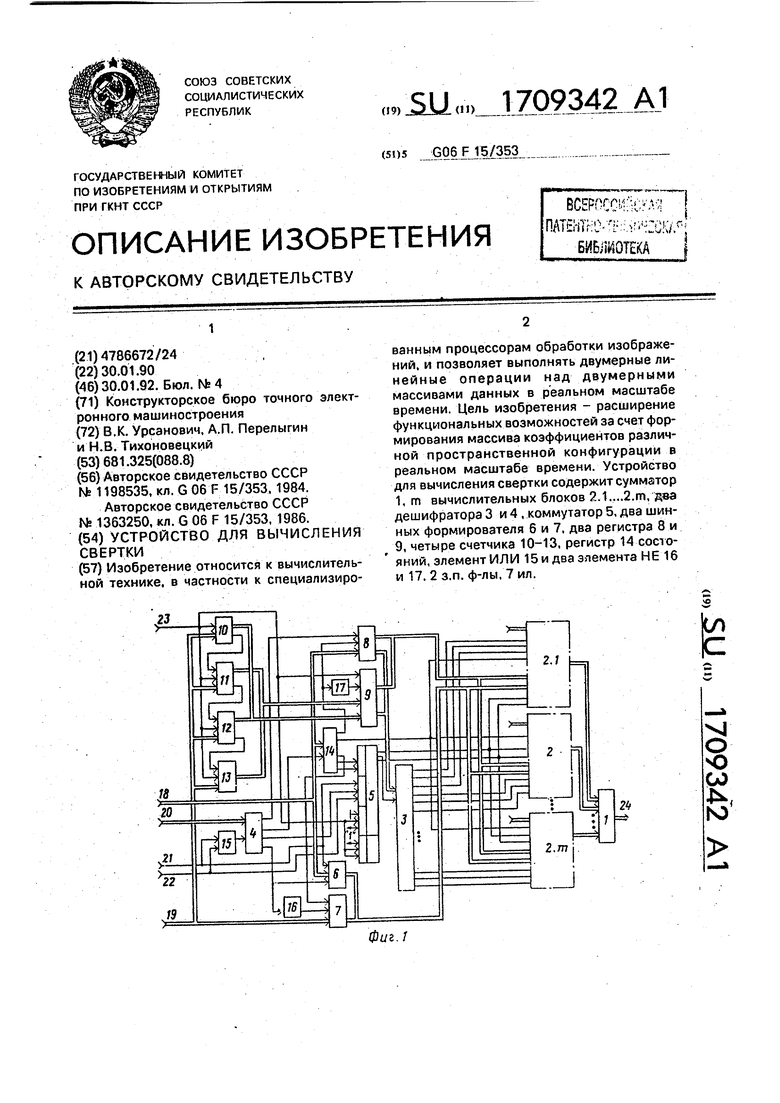

Поставленная цель достигается тем, что в устройство для вычисления свертки, содержащее сумматор и m вычислительных блоков, введены первь1й и второй дешифраторы, коммутатор, два шинных формирователя, два регистра, четыре счетчика, регистр состояний, элемент ИЛ И и два элемента НЕ, i-й (i ТТп) выход j-й ,пп) группы выходов первого дешифратора соединен с i-м входом управления -го вычислительного блока (где пит- размеры масок свертки по первому и второму измерениям). -Вход строба первого дешифратора соединен с первым выходом коммутатора, второй и третий выходы которого соединены соответственно с входами направления и входами записи вычислительных блоков. Выходы шинных формирователей подключены к входам данных вычислительных блоков, .информационные входы первого шинного формирователя и первого регистра - к входу коэффициентов устройства, информационный вход второго шинного формирователя является входом кода сигнала изображения устройства. Первые выходы первого и второго регистров соединены с адресными входами вычислительных блоков, аторые выходы - с информационным входом первого дешифратора. Информационные выходы первого и третьего счетчиков соединены с первым информационным входом второго регистра, информационные выходы второго и четвертого счетчиков- с вторым информационным входом второго регистра. Выход переноса К-го счетчика (,3) соединен с входом переноса {К+1)-го счетчика. Первый и второй выходы регистра состояний - соответственно с первым и вторым входами управления коммутатора. Информационный вход второго дешифратора является адресным входом устройства, вход управления второго дешифратора соединен с выходом элемента ИЛИ, первый и второй выходы которого являются соответственно первым и вторым входами управления устройства и соединены соответственно с первым и третьим информационными входами первой группы коммутатора, первый информационный

0 вход второй группы которого соединен с источником логического нуля (землей), второй информационный вход второй группы коммутатора соединен с вторым и третьим информационными входами третьей группы

5 коммутатора, синхровходом второго регистра, счетными входами счетчиков и является входом синхронизации устройства, третий информационный входвторой и первый информационный вход третьей групп коммутатора соединены с источником логической единицы. Первый выход второго дешифратора соединен с входом записи первого регистра, второй - с входом записи регистра состояний, третий - с вторым информационным входом первой группы коммутатора, четвертый - с первым входом управления первого шинного формирователя и с сходом первого НЕ, выход которого соединен с первым входом управления второго

0 шинного формирователя. Третий выход регистра состояний соединен с входом разрешения первого регистра и входом второго элемента НЕ, выход которого соединен с входом разрешения второго регистра. Четвертый выход регистра состояний соединен с вторым входом управления второго шинного формирователя, пятый выход - с входами блокировки вычислительных блоков. Второй вход управления первого шинного

0 формирователя является первым управляющим входом-устройства. Информационные входы счетчиков и входы кода сигнала изображения вычислительных блоков соединены с входом кода сигнала изображения

5 устройства, выход j-ro ) вычислительного блока подключен к j-му входу сумматора, выход которого является выходом свертки устройства.

Каждый вычислительный блок устройства содержит сумматор, п процессорных элементов и п элементов ИЛИ. Выход i-ro (i Tji) элемента ИЛИ подключен к первому управляющему входу i-ro процессорного элемента, первые входы элементов ИЛИ являются соответствующими входами управления вычислительного блока, а вторые соединены между собой и являются входом блокировки вычислительного блока, адресные входы процессорных элементов подключены к адресному входу

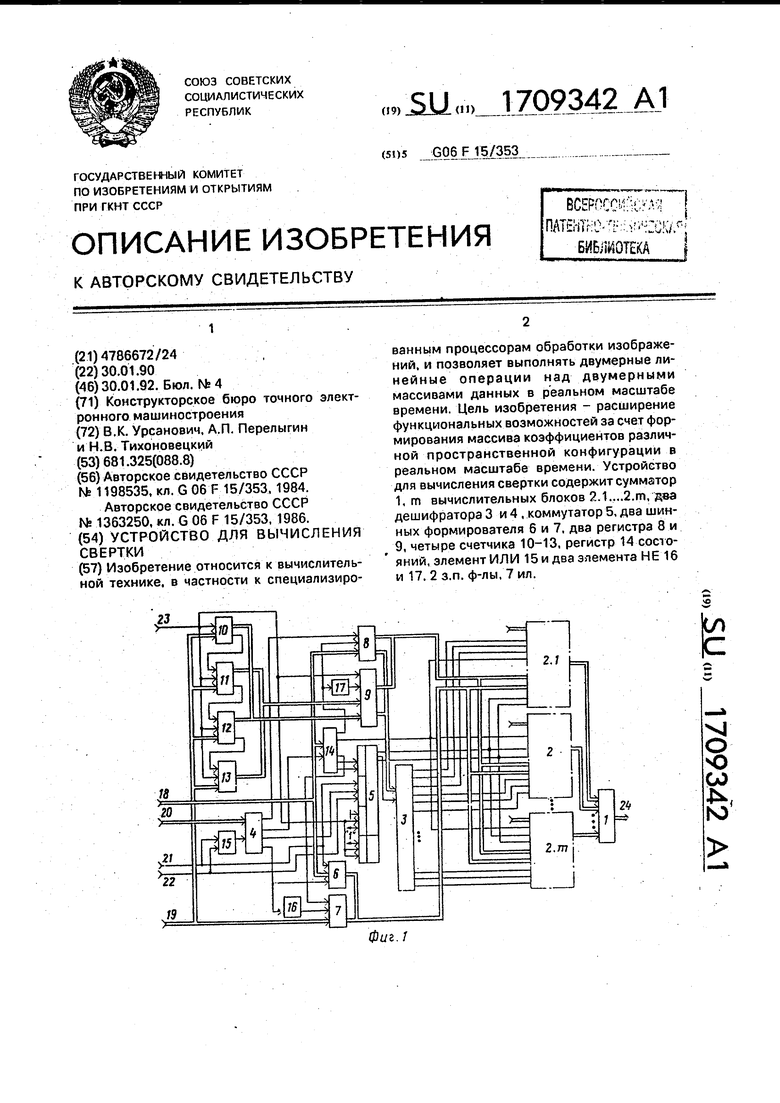

союз СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

SU,n, 1709342 А

(19)

ГОСУДАРСТВЕ ЖЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1

(21) 4786672/24

(22)30.01.90

(46) 30.01.92. Бюл. N54

(71)Конструкторское бюро точного электронного машиностроения

(72)В.К. Урсанович, А.П. Перелыгин и Н.В. Тихоновецкий (53)681.325(088.8)

(56)Авторское свидетельство СССР ГФ 1198535. кл. G 06 F 15/353, 1984.

Авторское свидетельство СССР Мг 1363250, кл. G 06 F 15/353, 1986. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СВЕРТКИ

(57)Изобретение относится к вычислительной технике, в частности к специализировсЕРосси;1 дя

r HTKO-- :i.vr:C w.

ванным процессорам обработки изображений, и позволяет выполнять двумерные линейные операции над двумерными массивами данных в реальном масштабе времени. Цель изобретения - расширение функциональных возможностей за счет формирования массива коэффициентов различной пространственной конфигурации в реальном масштабе времени. Устройство для вычисления свертки содержит сумматор 1, m вычислительных блоков 2.1....2.m, два дешифратора 3 и 4 , коммутатор 5, два шинных формирователя 6 и 7, два регистра 8 и 9, четыре счетчика 10-13, регистр 14 сосюяний, элемент ИЛ И 15 и два элемента НЕ 16 и 17. 2 з.п. ф-лы, 7 ил.

мента НЕ 16, выход которого соединен с первым входом управления второго шинного формирователя 7. Третий выход регистра 14 состояний соединен с входом разрешения первого регистра 8 и входом второго элемента НЕ 17, выход которого соединен с входом разрешения второго регистра 9. Четвертый выход регистра 14 состояний соединен с вторым входом управления второго шинного формирователя 7, пятый - с входами 27 блокировки вычислительных блоков 2.1...2.т. Второй вход управления первого шинного формирователя б является первым управляющим входом 21 устройства. Информационные входы счетчиков 1013 и входы кода сигнала изображения вычислительных блоков 2.1...2.т соединены с входом 19 кода сигнала изображения устройства. выходы вычислительного блока 2J (j 1,m) подключены к J-му входу сумматора. выход которого является выходом 24 свертки устройства.

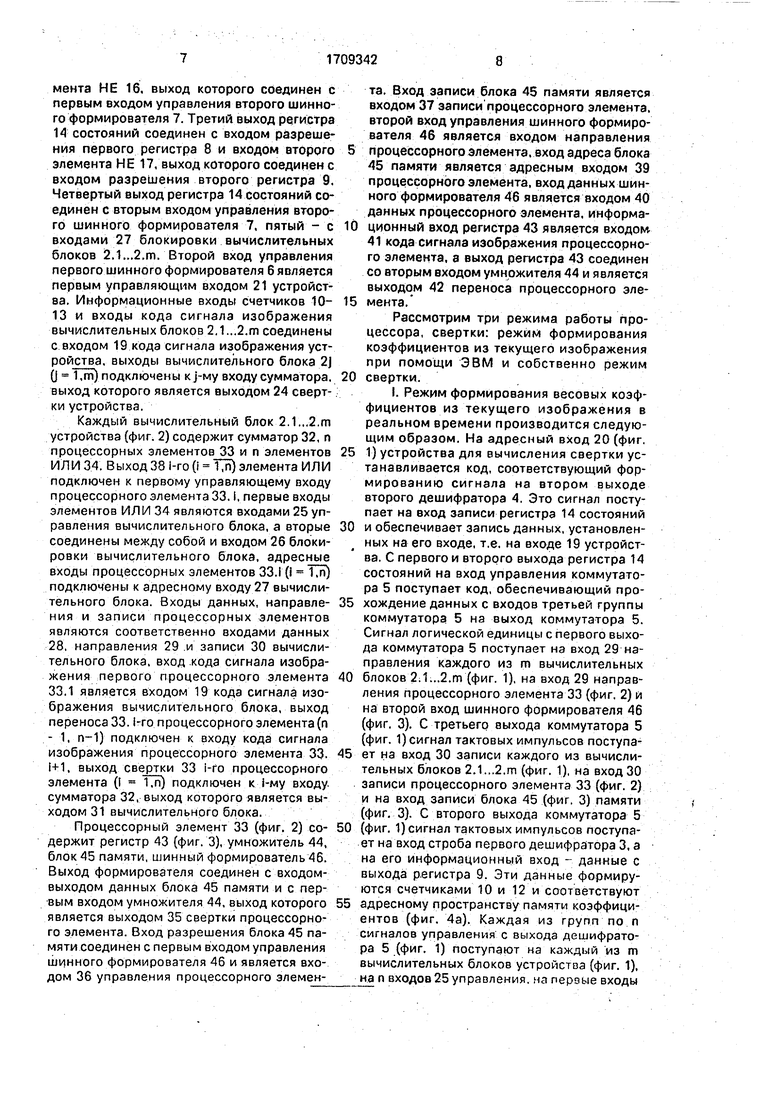

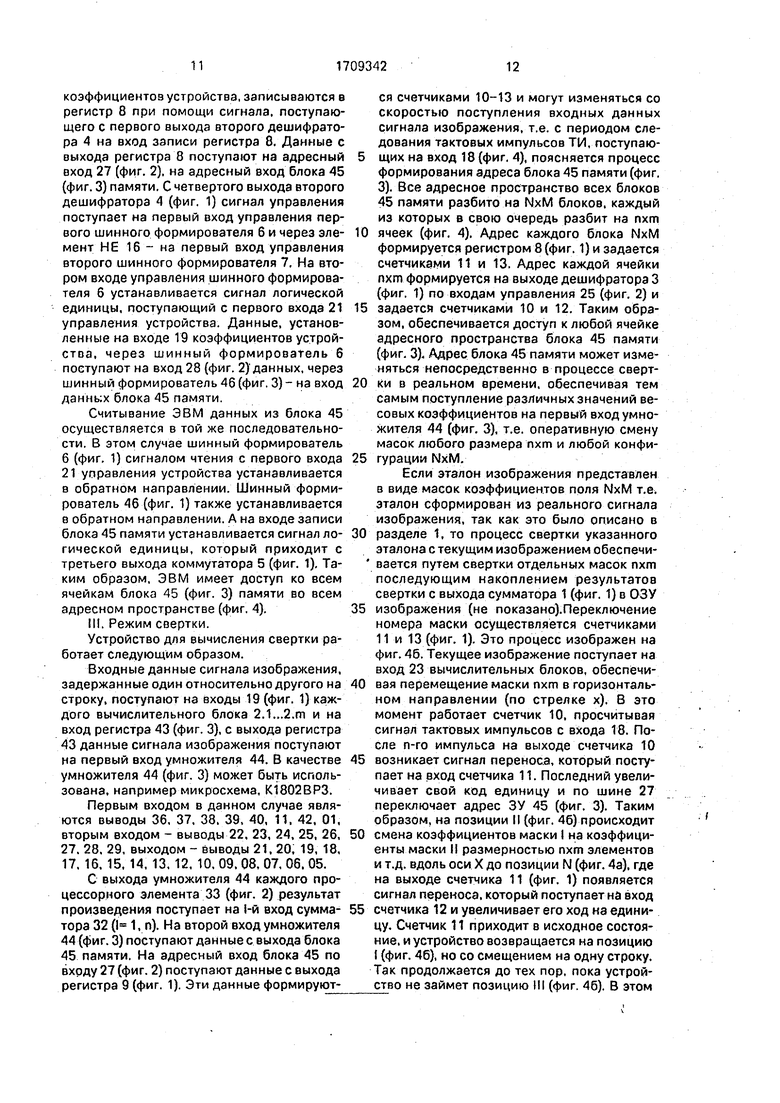

Каждый вычислительный блок 2.1...2.m устройства (фиг. 2) содержит сумматор 32, п процессорных элементов 33 и п элементов ИЛИ 34. Выход 38 1-го О iTn) элемента ИЛИ подключен к первому управляющему входу процессорного элемента 33.1, первые входы элементов ИЛИ 34 являются входами 25 управления вычислительного блока, а вторые соединены между собой и входом 26 блокировки вычислительного блока, адресные входы процессорных элементов 33.1 (i ТТп) подключены к адресному входу 27 вычислительного блока. Входы данных, направления и записи процессорных элементов являются соответственно входами данных 28. направления 29 .и записи 30 вычислительного блока, вход .кода сигнала изображения первого процессорного элемента 33.1 является входом 19 кода сигнала изображения вычислительного блока, выход переноса 33.1-го процессорного элемента (п - 1, п-1) подключен к входу кода сигнала изображения процессорного элемента 33. 1+1, выход свертки 33 i-ro процессорного элемента (1 Tjn) подключен к i-му входу, сумматора 32, выход которого является выходом 31 вычислительного блока.

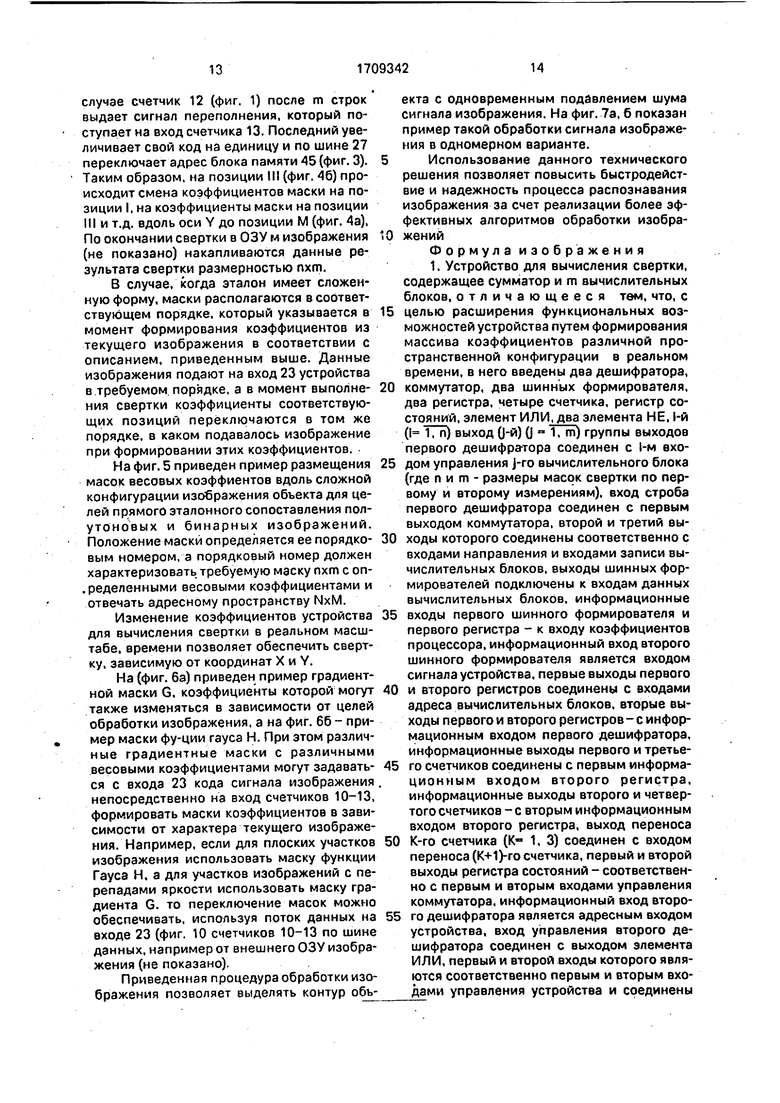

Процессорный элемент 33 (фиг, 2) содержит регистр 43 (фиг. 3), умножитель 44, блок 45 памяти, шинный формирователь 46. Выход формирователя соединен с входомвыходом данных блока 45 памяти и с первым входом умножителя 44, выход которого является выходом 35 свертки процессорного элемента. Вход разрешения блока 45 памяти соединен с первым входом управления шинного формирователя 46 и является входом 36 управления процессорного элемента. Вход записи блока 45 памяти является входом 37 записипроцессорного элемента, второй вход управления шинного формирователя 46 является входом направления процессорногоэлемента, вход адреса блока 45 памяти является адресным входом 39 процессорного элемента, входданных шинного формирователя 46 является входом 40 данных процессорного элемента, информационный вход регистра 43 является входом 41 кода сигнала изображения процессорного элемента, а выход регистра 43 соединен со вторым входом умножителя 44 и является выходом 42 переноса процессорного элемента.

Рассмотрим три режима работы процессора, свертки: режим формирования коэффициентов из текущего изображения при помощи ЭВМ и собственно режим свертки.

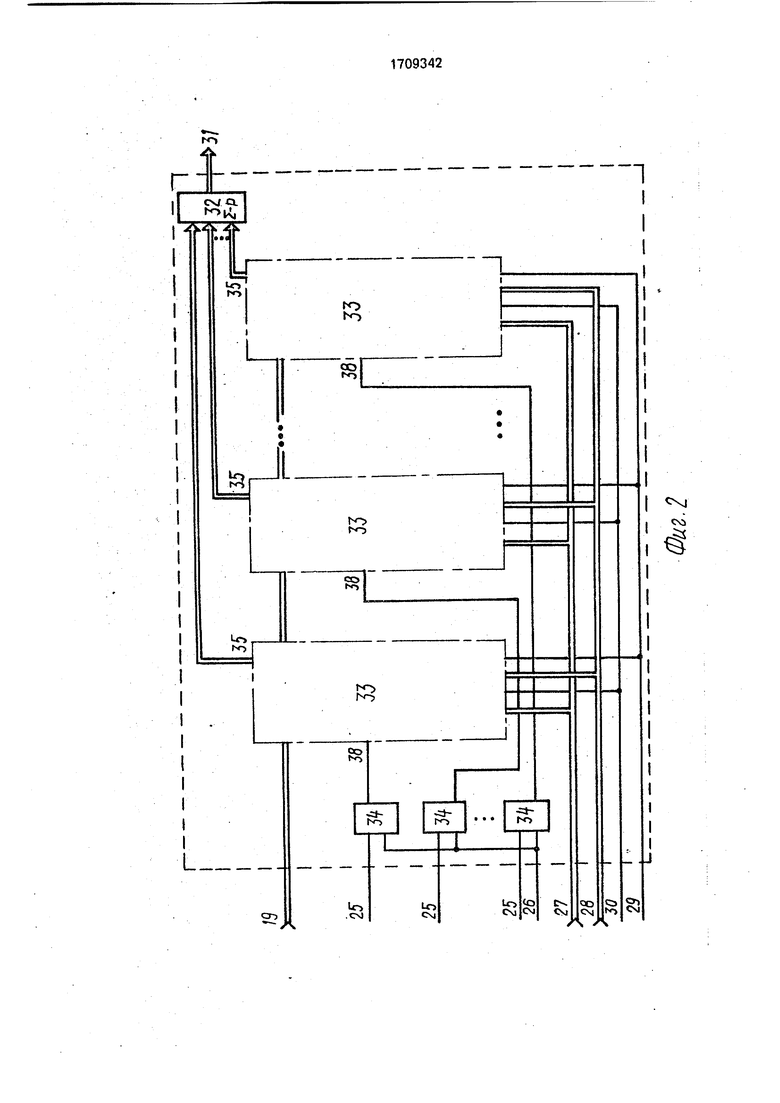

I. Режим формирования весовых коэффициентов из текущего изображения в реальном времени производится следующим образом. На адресный вход 20 (фиг. 1) устройства для вычисления свертки устанавливается код, соответствующий формированию сигнала на втором выходе второго дешифратора 4. Это сигнал поступает на вход записи регистра 14 состояний и обеспечивает запись данных, установленных на его входе, т.е. на входе 19 устройства. С первого и второго выхода регистра 14 состояний на вход управления коммутатора 5 поступает код, обеспечивающий прохождение данных с входов третьей группы коммутатора 5 на выход коммутатора 5. Сигнал логической единицы с первого выхода коммутатора 5 поступает на вход 29 направления каждого из m вычислительных блоков 2:1...2.m (фиг. 1). на вход 29 направления процессорного элемента 33 (фиг. 2) и на второй вход шинного формирователя 46 (фиг. 3). С третьего выхода коммутатора 5 (фиг. 1) сигнал тактовых импульсов поступает на вход 30 записи каждого из вычислительных блоков 2.1...2.т (фиг. 1), на вход 30 записи процессорного элемента 33 (фиг. 2) и на вход записи блока 45 (фиг. 3) памяти (фиг, 3). С второго выхода коммутатора 5 (фиг. 1) сигнал тактовых импульсов поступает на вход строба первого дешифратора 3, а на его информационный вход - данные с выхода регистра 9. Эти данные формируются счетчиками 10 и 12 и соответствуют адресному пространству памяти коэффициентов (фиг. 4а). Каждая из групп по п сигналов управления с выхода дешифратора 5 (фиг. 1) Поступают на каждый из m вычислительных блоков устройства (фиг. 1), на п входов25 управления, .ча перэые входы

n элементов ИЛИ 34 (фиг. 2), с выхода каждого из элементов ИЛИ 34 на вход разрешения блока 45 (фиг. 3) памяти и первый вход управления шинного формирователя 46. Эти сигналы разрешают прохождение данных сигнала и изображения с выхода шинного формирователя 46 на вход данных блока 45 памяти. Таким образом, данные сигнала изображения, поступающие в виде последовательности строк с входа 23 (фиг. 1) устройства через шинный формирователь 7 на вход 28 каждого из m вычислительных блоков 2.1...2,т и на вход 28 каждого из n процессорных элементов 33 (фиг. 2), записываются последовательно в n ячеек первого блока nxm первой строки (фиг. 4а), n ячеек второго блока nxm первой строки и т.д. до n ячеек N-ro блока первой строки. Затем n ячеек первого блока nxm втЬрой строки и т.д. до n ячеек N-ro блока М-й строки.

Таким образом, производится формирование пространства весовых коэффициентов из сигнала изображения в реальном времени.

Вывод весовых коэффициентов из устройства и представление их в виде весовых коэффициентов производится тем же путем, только в этом случае коммутатор 5 (фиг. 1) под действием нового кода управления с первого и второго выходов регистра 14 состояний выдает на свой выход сигналы с второй группы входов. При этом на вход 29 направления каждого из вычислительных блоков 2.1..,2,т поступает логический нуль. На вход 30 записи каждого из вычислительных блоков 2.1...2.m поступает сигнал логической единицы, на вход строба первого дешифратора 3 - сигнал тактовых импульсов. Блок 45 памяти (фиг. 3) находится в режиме Чтение, а шинный формирователь 46 переключен к обратное направление.

Данные весовых коэффициентов с выхода данных блока 45 памяти поступает через шинный формирователь 46 на вход данных 28 (фиг. 2), через шинный формирователь 7 (фиг. 1) - на вход 19 кода сигнала изображения устройства, при этом с выхода регистра 14 состояний на второй вход управления (направление) шинного формирователя 7 должен поступать сигнал логического нуля. Данные весовых коэффициентов могут выводиться в той же последовательности, в какой они были записаны в блок 45 памяти (фиг, 3), или в любой последовательности в зависимости от того, как будут запрограммированы счетчики 10-13.

В качестве коммутатора 5 (фиг. 1) может быть использована, например, микросхема КбЗТКПИ. В качестве входа управления коммутатора 5 используется вывод 01, в качестве входов первой группы-выводы 02,05, 11, в качестве,входов второй группы - выводы 03, 06, 10, в качестве выходов - выводы

04,07, 09.

5В качестве дешифратора 3 (фиг. 1) может быть использована, например, микросхема К155 ИДЗ. Информационными входами, соединенными с выходами регистров 8 и 9, в данном случае являются выводы

0 23, 22, 21, 20, входом управления - выводы 18,19, выходом первого канала-выводы 04,

05,06, 07, 08, второго канала - выводы 13, 14, 15, 16, 17.

В качестве регистров 8 и 9 (фиг. 1) может 5 быть использована, например, микросхема, К555ИР23. Входом записи является вывод 11, входом разрешения - вывод 01, информационными входами - 3, 4, 7, 8, 13, 14. 17, 19, выходами - 2. 5, 6, 9. 12, 15, 16, 19. 0 В качестве шинных формирователей 6 и

7(фиг. 1) может быть использована например микросхема, КР580ВА86. Информационным входом в данном случае являются выводы 1, 2, 3,4, 5, 6, 7, 8, выходом - вывод

5 09, вторым входом управления - вывод 11. .В качестве блоков памяти 15 (фиг. 3) может использована, например микросхема, К132РУ8.

Входом управления в данном случае яв0 ляется вывод 08, входом записи - вывод 10, входом адреса - выводы 5, 6, 7, 4, 3, 2, 1, 17, 16, 15, входами-выходами данных - выводы 14,13,12,11.

II. Режим записи, считывания весовых

5 коэффициентов при помощи ЭВМ.

В этом режиме коммутатор 5 (фиг. 1) под действием управляющих сигналов, поступающих с выхода регистра 14 состояний, обеспечивает прохождение данных с входов

0 первой группы на свой выход, т.е.,с первого выхода коммутатора 5 сигнал чтения, поступающий на его вход с первого входа 21 управления устройства, поступает на вход 29 направления процессорного элемента 33

5 (фиг. 2), на второй вход управления шинного формирователя 46 (фиг. 3). С третьего выхода коммутатора 5 (фиг. 1) сигнал, поступающий с второго входа 22 управления устройства, поступает на вход 30 записи

0 процессорного элемента 33 (фиг, 2), на вход записи блока 45 памяти (фиг. 3). С второго выхода коммутатора 5 (фиг. 1), сигнал, поступающий с третьего выхода второго дешифратора 4, поступает на вход строба первого

5 дешифратора 3, с третьего выхода регистра 14 состояний сигнал логического нуля поступает на вход разрешения первого регистра

8и через элемент НЕ 17 - сигнал логической единицы на вход разрешения второго регистра 9, Данные, установленные на входе 19

коэффициентоз устройства, записываются в регистр 8 при помощи сигнала, поступающего с первого выхода второго дешифратора 4 на вход записи регистра 8, Данные с выхода регистра 8 поступают на адресный вход 27 (фиг. 2). на адресный вход блока 45 (фиг. 3) памяти. С четвертого выхода второго дешифратора 4 (фиг. 1) сигнал управления поступает на первый вход управления первого шинного формирователя 6 и через элемент НЕ 16 - на первый вход управления второго шинного формирователя 7, На втором входе управления шинного формирователя 6 устанавливается сигнал логической единицы, поступающий с первого входа 21 управления устройства. Данные, установленные на входе 19 коэффициентов устройства, через шинный формирователь б поступают на вход 28 (фиг. 2) данных, через шинный формирователь 46 (фиг. 3) - на вход данных блока 45 памяти.

Считывание ЭВМ данных из блока 45 осуществляется в той же последовательности. В этом случае шинный формирователь 6 (фиг. 1) сигналом чтения с первого входа 21 управления устройства устанавливается в обратном направлении. Шинный формирователь 46 (фиг. 1} также устанавливается в обратном направлении. А на входе записи блока 45 памяти устанавливается сигнал логической единицы, который приходит с третьего выхода коммутатора 5 (фиг. 1). Таким образом, ЭВМ имеет доступ ко всем ячейкам блока 45 (фиг. 3) памяти во всем адресном пространстве (фиг. 4).

III. Режим свертки.

Устройство для вычисления свертки работает Следующим образом.

Входные данные сигнала изображения, задержанные один относительно другого на строку, поступают на входы 19 (фиг. 1) каждого вычислительного блока 2.1...2.т и на вход регистра 43 (фиг. 3), с выхода регистра

43данные сигнала изображения поступают

на первый вход умножителя 44. В качестве умножителя 44 (фиг. 3) может быть использована, например микросхема, К1802ВРЗ.

Первым входом в данном случае являются выводы 36, 37, 38, 39, 40, 11, 42, 01, вторым входом - выводы 22, 23, 24, 25, 26, 27, 28, 29, выходом - выводы 21, 20. 19, 18, 17, 16, 15, 14, 13, 12, 10, 09, 08, 07, 06, 05.

С выхода умножителя 44 каждого процессорного элемента 33 (фиг. 2) результат произведения поступает на 1-й вход сумматора 32 (1 1, п). На второй вход умножителя

44(фиг. 3) поступают данные с выхода блока

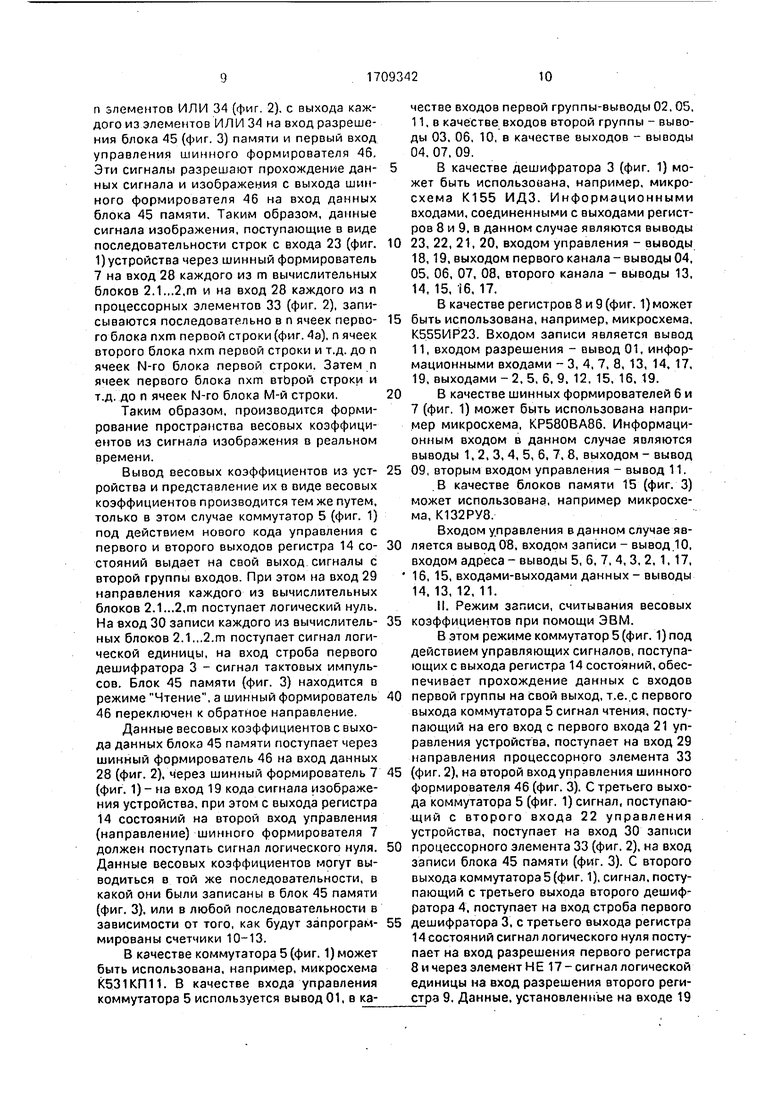

45памяти. На адресный вход блока 45 по входу 27 (фиг. 2) поступают данные с выхода регистра 9 (фиг. 1). Эти данные формируются счетчиками 10-13 и могут изменяться со скоростью поступления входных данных сигнала изображения, т.е. с периодом следования тактовых импульсов ТИ, поступающих на вход 18 (фиг. 4), поясняется процесс формирования адреса блока 45 памяти (фиг. 3). Все адресное пространство всех блоков 45 памяти разбито на NxM блоков, каждый из которых в свою очередь разбит на nxm ячеек (фиг. 4). каждого блока NxM формируется регистром 8 (фиг. 1) и задается счетчиками 11 и 13. Адрес каждой ячейки nxm формируется на выходе дешифратора 3 (фиг. 1) по входам управления 25 (фиг. 2) и задается счетчиками 10 и 12. Таким образом, обеспечивается доступ к любой ячейке адресного пространства блока 45 памяти (фиг. 3). Адрес блока 45 памяти может изменяться непосредственно в процессе свертки в реальном времени, обеспечивая тем самым поступление различных значений весовых коэффициентов на первый вход умножителя 44 (фиг. 3), т.е. оперативную смену масок любого размера nxm и любой конфигурации NxM.

Если эталон изображения представлен в виде масок коэффициентов поля NxM т.е. эталон сформирован из реального сигнала изображения, так как это было описано в разделе 1, то процесс свертки указанного эталона с текущим изображением обеспечивается путем свертки отдельных масок nxm последующим накоплением результатов свертки с выхода сумматора 1 (фиг. 1) в ОЗУ изображения (не показано).Переключение номера маски осуществляется счетчиками 11 и 13 (фиг. 1). Это процесс изображен на фиг. 46. Текущее изображение поступает на вход 23 вычислительных блоков, обеспечивая перемещение маски nxm в горизонтальном направлении (по стрелке х). В это момент работает счетчик 10, просчитывая сигнал тактовых импульсов с 18. После п-го импульса на выходе счетчика 10 возникает сигнал переноса, который поступает на вход счетчика 11. Последний увеличивает свой код единицу и по шине 27 переключает адрес ЗУ 45 (фиг. 3). Таким образом, на позиции II (фиг. 46) происходит смена коэффициентов маски I на коэффициенты маски II размерностью nxm элементов и т.д. вдоль оси X до позиции N (фиг. 4а), где на выходе счетчика 11 (фиг. 1) появляется сигнал переноса, который поступаетна вход счетчика 12 и увеличивает его ход на единицу. Счетчик 11 приходит в исходное состояние, и устройство возвращается на позицию I (фиг. 46), но со смещением на одну строку. Так продолжается до тех пор, пока устройство не займет позицию III (фиг. 46). В этом

случае счетчик 12 (фиг. 1) после m строк выдает сигнал переполнения, который поступает на вход счетчика 13. Последний увеличивает свой код на единицу и по шине 27 переключает адрес блока памяти 45 (фиг. 3). Таким образом, на позиции III (фиг. 46) происходит смена коэффициентов маски на позиции I, на коэффициенты маски на позиции III и т.д. вдоль оси Y до позиции М (фиг. 4а), По окончании свертки в ОЗУ м изображения (не показано) накапливаются данные результата свертки размерностью nxm.

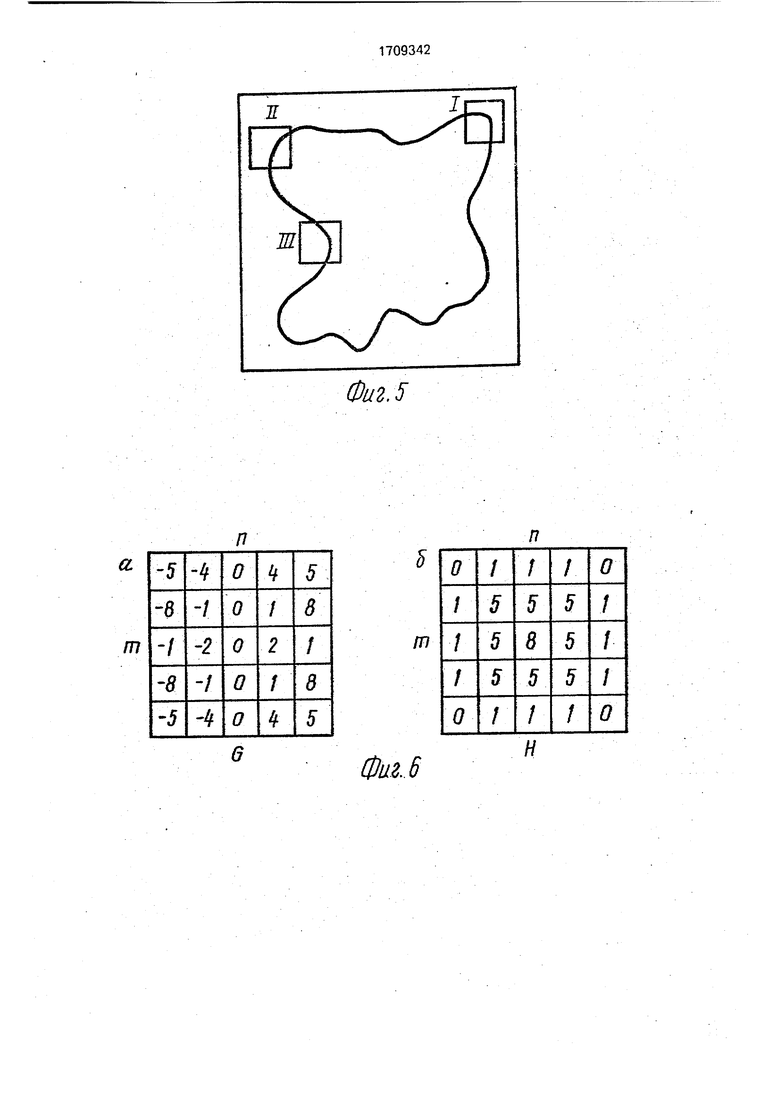

В случае, когда эталон имеет сложенную форму, маски располагаются в соответствующем порядке, который указывается в момент формирования коэффициентов из текущего изображения в соответствии с описанием, приведенным выше. Данные изображения подают на вход 23 устройства в требуемом, порядке, а в момент выполнения свертки коэффициенты соответствующих позиций переключаются в том же порядке, в каком подавалось изображение при формировании этих коэффициентов.

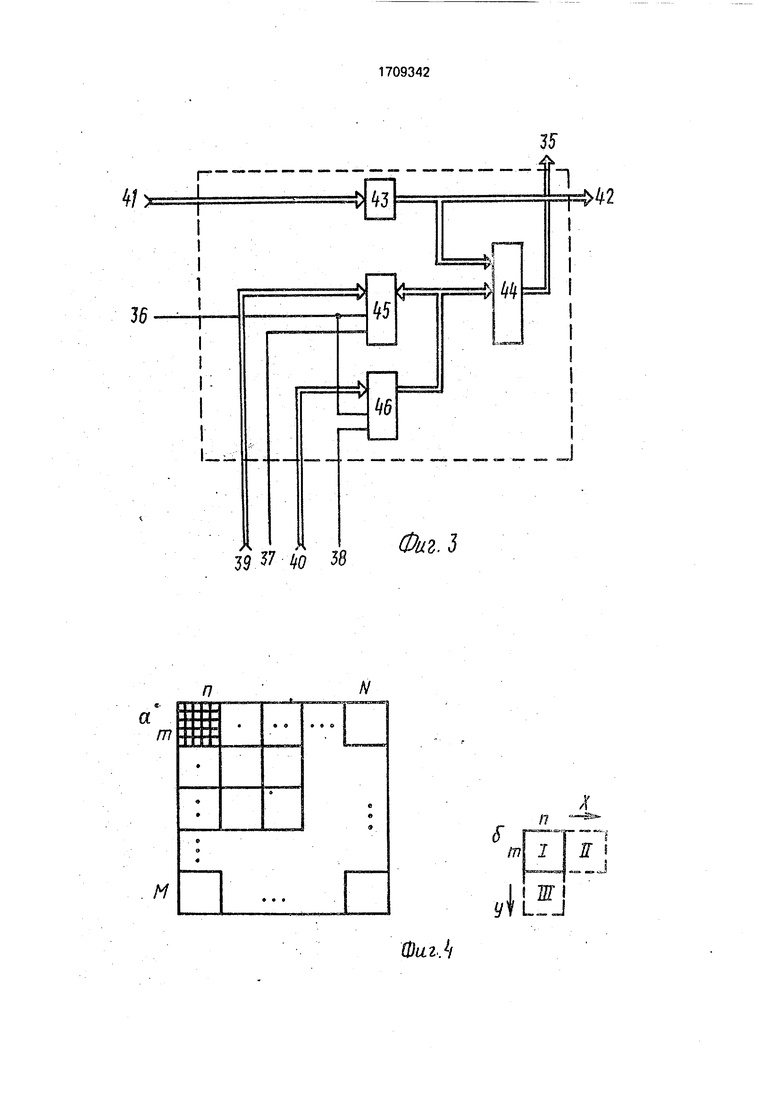

На фиг, 5 приведен пример размещения масок весовых коэффиентов вдоль сложной конфигурации изображения объекта для целей прямого эталонного сопоставления полутоновых и бинарных изображений. Положение маски определяется ее порядковым номером, а порядковый номер должен характеризовать требуемую маску nxm с оп.ределенными весовыми коэффициентами и отвечать адресному пространству NxM.

Изменение коэффициентов устройства для вычисления свертки в реальном масштабе, времени позволяет обеспечить свертку, зависимую от координат X и Y.

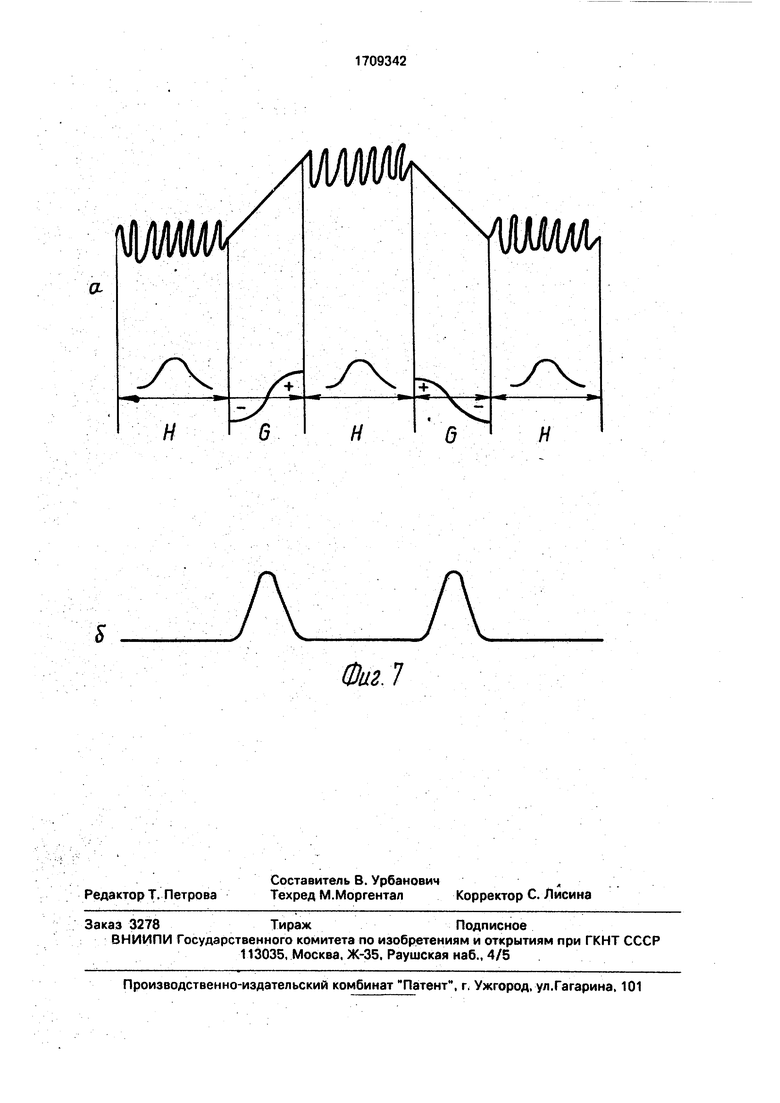

На (фиг. 6а) приведен пример градиентной маски G, коэффициенты которой могут также изменяться в зависимости от целей обработки изображения, а на фиг. 66 - пример маски фу-ции гауса Н. При этом различные градиентные маски с различными весовыми коэффициентами могут задаваться с входа 23 кода сигнала изображения непосредственно на вход счетчиков 10-13, формировать маски коэффициентов в зависимости от характера текущего изображения. Например, если для плоских участков изображения использовать маску функции Гауса Н. а для участков изображений с перепадами яркости использовать маску градиента G. то переключение масок можно обеспечивать, используя поток данных на входе 23 (фиг. 10 счетчиков 10-13 по шине данных, например от внешнего ОЗУ изображения (не показано).

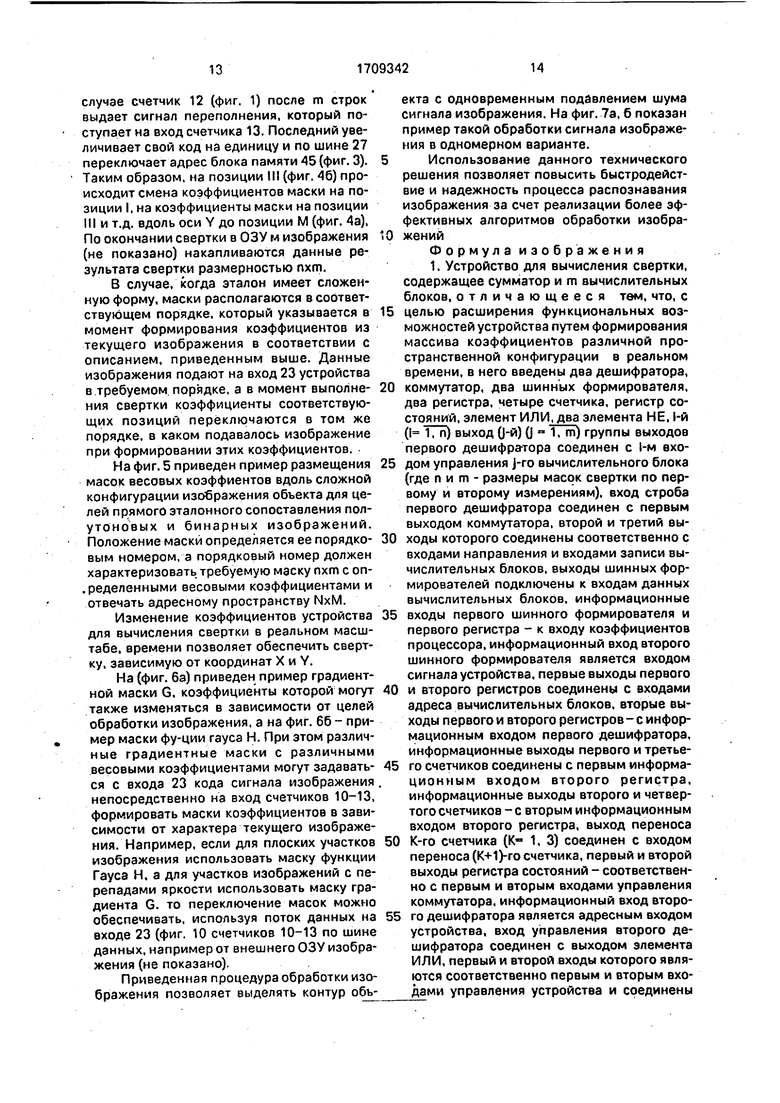

Приведенная процедура обработки изображения позволяет выделять контур объекта с одновременным подавлением шума сигнала изображения. На фиг. 7а, б показан пример такой обработки сигнала изображения в одномерном варианте.

Использование данного технического решения позволяет повысить быстродействие и надежность процесса распознавания изображения за счет реализации более эффективных алгоритмов обработки изображений

Формула изображения 1, Устройство для вычисления свертки, содержащее сумматор и m вычислительных блоков, отличающееся , что, с целью расширения функциональных возможностей устройства путем формирования массива коэффициентов различной пространственной конфигурации в реальном времени, в него введены два дешифратора, коммутатор, два шинных формирователя, два регистра, четыре счетчика, регистр состояний, элемент ИЛИ, два элемента НЕ, 1-й (1 1, п) выход (j-й) О 1, пт) группы выходов первого дешифра-тора соединен с 1-м входом управления j-ro вычислительного блока (где пит- размеры масок свертки по первому и второму измерениям), вход строба первого дешифратора соединен с первым выходом коммутатора, второй и третий выходы которого соединены соответственно с входами направления и входами записи вычислительных блоков, выходы шинных формирователей подключены к входам данных вычислительных блоков, информационные входы первого шинного формирователя и первого регистра - к входу коэффициентов процессора, информационный вход второго шинного формирователя является входом сигнала устройства, первые выходы первого и второго регистров соединены с входами вычислительных блоков, вторые выходы первого и второго регистров - с информационным входом первого дешифратора, информационные выходы первого и третьего счетчиков соединены с первым информационным входом второго регистра, информационные выходы второго и четвертого счетчиков -с вторым информационным входом второго регистра, выход переноса К-го счетчика (К- 1, 3) соединен с входом переноса (К+1)-го счетчика, первый и второй выходы регистра состояний - соответственно с первым и вторым входами управления коммутатора, информационный вход второго дешифратора является адресным входом устройства, вход управления второго дешифратора соединен с выходом элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым входами управления устройства и соединены

соответственно с первым и вторым информационными входами первой группы коммутатора, первый информационный вход второй группы которого соединен с источником логического нуля, второй информационный вход второй группы коммутатора - с первым и вторым информационными входами третьей группы коммутатора, синхровходом второго регистра, счетными входами счетчиков и является входом синхронизации устройства, третьи информационные входы второй и третьей групп коммутатора соединены с источником логической единицы, первый выход второго дешифратора с входом 39ПИСИ первого регистра, второй - с входом записи регистра состояний, третий - с третьим информационным входом первой группы коммутатора, четвертый -с первым входом управления первого шинного формирователя и с входом первого элемента НЕ. выход которого соединен с первым входом управления второго шинного формирователя. Третий выход регистра состояний соединен с входрм разрешения первого регистра и с входом второго элемента НЕ, выход которого соединен с входом разрешени-я второго регистра, четвертый выход- с вторым входом управления второго шинного формирователя, пятый выход- с входами блокировки вычислительных блоков, второй вход управления первого шинного формирователя является первым управляющим входом устройства, информационные входы счетчиков и входы кода сигнала изображения вычислительных блоков соединены с входом кода сигнала изображения устройства, выход j-ro Q 1, m) вычислительного блока подключен к j-му входу сумматора, выход которого является выходом свертки устройства.

2. Уст эойство по п. 1, о т чающеес я тем, что каждый вычислительный блок содержит сумматор m процессорных элементов, п элементов ИЛИ, выход 1-го (И 1, п) элемента ИЛИ подключен к первому управляющему входу 1-го процессорного элемента, первые входы элементов ИЛИ являются соответствующими входами управления вычислительного блока, а вторые соединены между собой и являются входом блокировки вычислительного блока, адресные входы процессорных элементов подключены к адресному входу вычислительного блока, входы данных, направления и записи

процессорных элементов являются соответственно одноименными входами, вычислительного блока, вход кода сигнала изображения первого процессорного элемента - одноименным вычислительного

блока, выход переноса 1-го процессорного элемента (1 1, п-1) подключен к входу кода сигнала изображения ()-ro процессорного элемента, выход свертки (1-го процессорного элемента (I 1, п) подключен к 1-му

входу сумматора, выход которого является выходом вычислительного блока.

3. Устройство по пп. 1и2,отличающ ее с я тем, что каждый процессорный элемент содержит регистр, умножитель,

блок памяти, шинный формирователь, выход которого соединен с входом-выходом данных блока памяти и с первым входом умножителя, выход которого является выходом свертки процессорного элемента, вход

разрешения блока памяти соединен с первым входом управления шинного формирователя и является входом управления процессорного элемента, вход записи блока памяти является входом записи процессорного элемента, второй вход управления шинного формирователя - входом направления процессорного элемента, вход адреса блока памяти - адресным входом процессорного элемента, вход данных шинного

формирователя - входом данных процессорного элемента, информационный вход регистра - входом сигнала процессорного элемента, а выход регистра соединен с вторым входом умножителя и является выходом переноса процессорного элемента.

1

t .

Г

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1989 |

|

SU1644208A1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

Изобретение относится к вычислительной технике, в частности к специализиро-ванным процессорам обработки изображений, и позволяет выполнять двумерные линейные операции над двумерными массивами данных в реальном масштабе времени. Цель изобретения - расширение функциональных возможностей за счет формирования массива коэффициентов различной пространственной конфигурации в реальном масштабе времени. Устройство для вычисления свертки содержит сумматор 1, m вычислительных блоков 2.1....2.m, два дешифратора 3 и 4 , коммутатор 5, два шинных формирователя 6 и 7, два регистра 8 и 9, четыре счетчика 10-13, регистр 14 сосю- яний, элемент ИЛ И 15 и два элемента НЕ 16 и 17. 2 з.п. ф-лы, 7 ил.псос.23VIо юСА)fe'

ч|

39 7 за

М

/Г

сиве1« 51Э J t

I

J

-IL

Ж1

Wut.f

I

n

т

6

Фиг. 5

n

т

Н

Фиг.. 6

(ШМл

Х

А

Фиг. 7

| Устройство для вычисления свертки | 1984 |

|

SU1198535A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-30—Подача