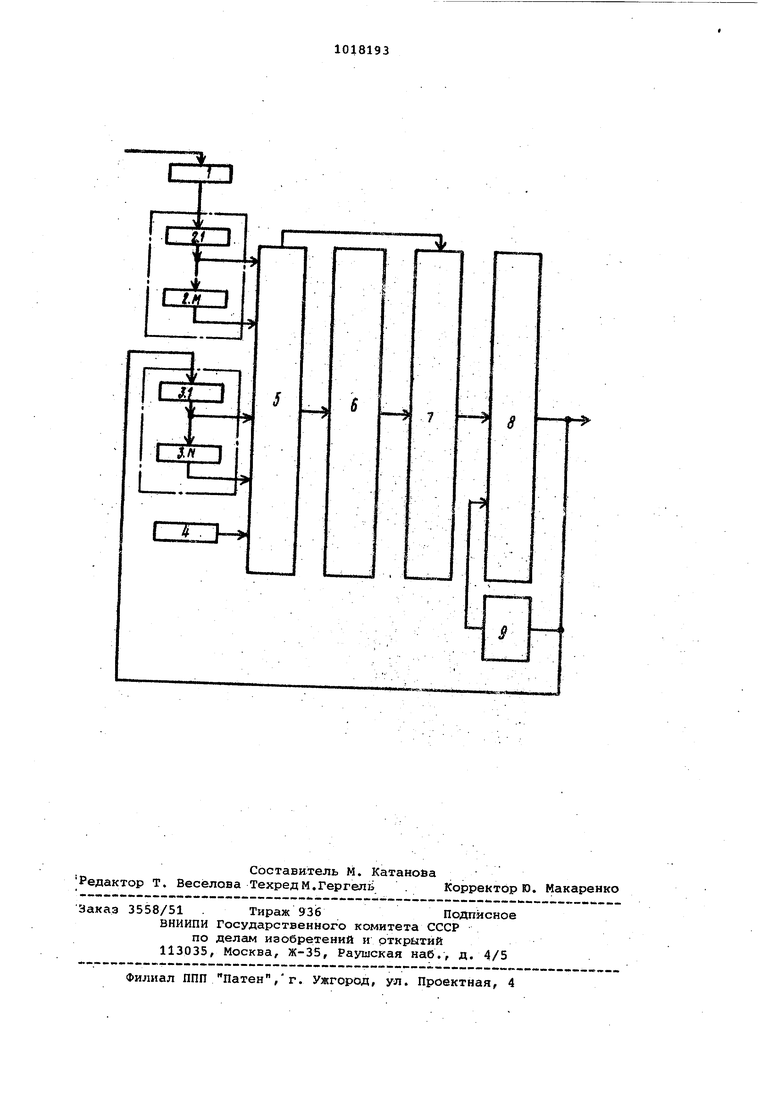

Изобретение относится к радиотехни ке и может использоваться в системах цифровой обработки сигналов в радиоло кации, радиосвязи, радионавигации. Известен аналоговый фазовый детектор с.синусоидальной характеристикой, в состав которого входят аналоговый перемножитель входного напряжения на напряжение, подаваемое с выхода генератора гармонического опорного напряжения, и аналоговый фильтр нижних частот для режекции побочных высокочастотных составляющих, возникающих при перемножении Г ЗНедостатками такого фазового детек тора являются низкая стабильность и сложностьсопряжения с ЦВМ. Известен также цифровой фазовый детектор содержащий блок преобразова ния напряжение - код, цифровой перемножитель и цифровой фильтр нижних частот (усредняющее устройство), причем первый вход блока преобразования напряжение - код соединен с входной шиной .цифрового фазового детектора, выход блока преобразования напряжение - код подключен к первому входу цифрового перемножителя, выход которого подключен к входу цифрового фильтра нижних частот (усредняющего устройства), на второй вход цифрового перемножителя подаются коды, являющився .отсчетами опорного колебания ,2, Недостатком известного цифрового .фазового детектора является низкое быстродействие, вывязанное необходимостью.1эеализации операции перемножения перед операцией фильтрации и oneрацией умножения в цифровом фильтре. Цель изобретения - повышение быстродёйствия цифрового фазового датектора с синусоидальной характерист Поставленная цель достигаетсяТем что в цифровой фазовый детектор, содержащий блок преобразования напряжение - код, вход которого соединен с входной шиной цифрового фазового детектора, вводится первая и вторая Г1:Уппы регистров сдвига, пересчетная схема и последовательно соединенные i,-;-i:L-.T..:r..тор и узел сдвига, причем выход блока преобразования напряжение- кодподклю.чен к входу первого регистра сдвига первой группы регистров сдвига, вход каждого последующегорегистра сдвига первой и второй регистров сдвига подключен к выходу предьадущего регистра сдвига первой и второй групп регистров сдвига соответственно, выходы регистров сдвига первой и второй групп регистров сдвига, а также выход пересчетной схемы подключены к входам блока преобразования кодов,., выход накапливающего сумматора соединен с входом первого регистра сдвига второй65 напа)( .К этому момент времени в регистгруппы регистров сдвига, при этом выход узла сдвига подключен к второму входу накапливающего сумматора, в орой выход блока преобразования кодов подключен к второму входу коммутатора а выход накапливающего сумматора соединен с выходной шиной цифрового фазового детектора. На чертеже представлена структурная схема устройства. В состав цифрового фазового детектора входят блок 1 преобразования напряжение - код, регистры 2-1 - сдвига первой группы регистров сдвига, регистры 3-1 - 3-N сдвига второй груп регистров сдвига, пересчатная схема 4, блок 5 преобразования кодов, блок 6 памяти, коммутатор 7, накапливающий сумматор 8, узел. 9 сдвига, Вход блока 1 преобразования напряже- ние - код соединен с входной шиной цифрового фазового детектора. Выход блока 1 преобразования напряжение код подключен к входу регистра 2-1 сдвига, входы регистров 2-1 - 2-М, 3-1 - 3-W подключены соответственно к выходам регистров 2-1 -2- (АЛ-1), 3-1 - З-XN-i) сдвига и выход пересчет ной схемы 4 подключен к входам блока 5 преобразования кодов, первый выход которого подключен к выходу блока 6 памяти, выход которого подключен к первому входу коммутатора 7, выход которого подключен к первому входу накапливающего сумматора 8, выход которого подключен к входу узла 9 сдвига и к входу регистра 3-1 сдвига выход узла 9 сдвига подключен к второму входу накапливающего сумматора 8, второй выход блока 5 преобразования кодов подключен к второму входу коммутатора 7. Цифровой фазовый детектор работает следуюищм образом., Сигнал, действующий на вход цифрового фазового детектора, имеет вид XCi)SU)siVCis;fc+ fCt)), ti) где s(t) - амплитуда сигнала;; ч - нёсущая угловая частота; tf(t) - фаза сигнала. с. i счетов из входного сигнала. X -5 (1СТ)51И (K(i)T+ (КТ) ),(2) где Т - интервал дискретизации; V г П 1 5 У,Х,Л Перед началом работы цифрового фазового детектора в блок б памяти записываются числа, предварительно вычисленные в соответствии с заданной характеристикой преобразования. В первом такте работы цифрового фазового детектора в первый регистр 2-1 сдвига первой группы регистров сдви га передается с выхода преобразователя напряжение - кол отсчет входного сигpax сдвига первой и второй групп регистров сдвига хранятся соответственно числс1, входной X и выходной n.j последовательностей отсчетов, причем номера регистров входной последовательности 1 -М, а выходной 1 -W .

В пересчетной схеме записано число P kw«od(vnoXP - остаток от деления на максимальное число Р, в накапливающем сумматоре установлено число О. Блок 5 преобразования кодов формирует адрес блока б памяти и из блока 6 памяти считывается число, которое при помощи коммутатора 7. передается с противоположным знаком (на первый вход накапливающего сумматора 8). После этого производится сдвиг в сторону clapiiBix разрядов в регистрах сдвига первой и второй групп регистров сдвига таким образом, что значения .старших разрядов предыдущих регистров сдвига в каждой группе регистров сдвига переписалвакстся в младшие разряды последуюивйх регистроэ сдвига в той же группе регистров сдвига. После этого описанная последовательность Д0ЯСТВИЙ повторяется. Отличие заключается в том, что коммутатор 7 пере-. дает Числа, считываемые из блока б памяти/без изменения, а на второй вход накапливающего сумматора 8 передается содержимое ЗТого же накапливающего сумматора 8, вычисленное в предыдущих тактах, сдвинутое наодин разряд в сторону младциих разрядов. Если ej- - разрядность регистров сдвига Нервой и второй групп регистров сдвига, то после tV описанных выше тактов в накаплива1«цем сумматоре вычисляетЬя выходной отсчет циЧрбвого фазового детектора Уц , который в следующем такте передается в первый регистр 3-1 сдвига второй группы регистров сдвига, а число в пересчетной схеме увеличивается на единицу. После этого цифрово1й фазовый детектор готов к об.работке следующего отсчета выходйой последовательности. В соответствии с описанной работой цифрового фазового

детектора выходной отсчет вычисляется по формуле

t

V-|oaKn,od(Yvo4p)K-i-Hj,.

т Jl. Выражение (3) при Т ш |ГДе Ц,

I/J.- целые числа, легко привести к виду

Uk.--K.-COSt(K-OU)Ti, (4)

;VK--4a,UK.)Vk.:i(5)

представляя (1) в С), получим

Vr-Vi WK..(6J где Vi0,5S((K--i)T)siw Ч((К-1)таЗ, (1)

y.,s(fK-i)T)5ihUk-i)aQ}T

1(8)

+v({K--i)T)

Jg представляет собой полезную составляющую входного сигнала, содержащую информацию о фазе сигнала, ttfgпобочную высокочастотную составляющую сигнала. Коэффициенты Q и Ъ в (5) выбираются таким образом, чтобы пропустить с наименьшими искажениями V и как можно сильнее подавить (fe

Полагая SCt) S «« Const и f(t) con st .получим

(9)

B-S-sin o e;

где В - коэффициент передачи цифрового фазового, детектора; 6 г остаток режек1Ши побочной высокочастотной составляющей, т.е. предлагаемый цифровой фазовый детектор имеет синусоидальную характеристику.

Таким образом, в предлагаемом цифровом детекторе удалось избежать выполнения операции умножения, в результате чего быстродействие цифрового фазового детектора увеличивается.

I .л I

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель сдвига фаз | 1979 |

|

SU834593A2 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Многоканальный модем | 1985 |

|

SU1297250A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1129641A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Способ обнаружения и высокоточного определения параметров морских ледовых полей и радиолокационная система для его реализации | 2019 |

|

RU2710030C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1689937A1 |

| Индикаторное устройство | 1990 |

|

SU1779936A1 |

| Устройство контроля веществ | 2016 |

|

RU2618488C1 |

ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР С СИНУСОИДАЛЬНОЙ ХАРАКТЕРИСТИКОЙ, содер:жащий блок преобразования напряжение код, первый вход которого соединен с входной шиной цифрового фазового де-, тектора, отличающийся тем, что, с целью повышения быстродействия, ;в него введены первая и вторая группы регистров сдвига, пересчетная схема и последовательно соединенные блок преобразования кодов, блок памяти, коммутатор, накапливающий сумматор и узел сдвига, причем выход блока преобразования напряжение - код подключен к входу первого регистра сдвига первой группы регистров сдвига, вход каивдого последующего регистра сдвига первой и второй группы регистров сдвига подключен к выходу предыдущего регистра сдвига Первой и второй групп регистров сдвига соответственно, выходы регистров сдвига первой и второй групп регистров сдвига, а также выход пересчет ной схемы подключены к входам блока преобразования кодов,выход накапливаю-О щего сумматора соединен с входом перво-® го регистра сдвига второй группы регист а с ров сдвига, при этом выход узла сдвига подключен к второму входу накапливаю щего сумматора, второй выход блока преобразования кодов подключен к BTO-Q рому входу коммутатора, а выход накап ливающего сумматора соединен с выход- ной шиной цифрового детектора.

сжз

I

u.

LJLZJ-

7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чистяков Н.И | |||

| и др | |||

| Радиоприемные устройства | |||

| М., Связь, 1974, с | |||

| Крутильный аппарат | 1922 |

|

SU233A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Лихарев В.А | |||

| Цифровые методы и устройства в радиолокации | |||

| М., Сов | |||

| радио, 1973, с | |||

| Приспособление для картограмм | 1921 |

|

SU247A1 |

Авторы

Даты

1983-05-15—Публикация

1981-11-06—Подача