множимого блока четвертого умножителя, а второй вход связан с вторыми входами множителя и множимого блока четвертого умножителя и с выходом четвертого сумматора, первый вход которого соединен с выходом блока восьмого регистра, первый вход которого связан с выходом блока четвертого умножителя, второй вход четвертого сумматора является четвертым информационным входом устройства, второй вход блока восьмого регистра связан с первыми входами первого,вто рого, третьего элементов И и с пятым информационным входом устройства, выходы блока управления с первого по восьмой подключены к управляющим входам блоков первого, второго,третьего, четвертого, пятого шестого, седьмого и восьмого регистров соответственно, выходы блока управления с девятого по двадцатый подключены к первым, вторым и третьим управляющим входам блоков первого, второго, третьего и четвертого умножителей соответственно, выходы блока управления с двадцать первого по двадцать третий, подключены к вторым входам первого, второго и третьего элементов И, двадцать четвертый выход блока управления является выходом признака окончания операции устройства, первый и второй входы синхронизации блока управления являются первым и вторым входами синхронизации устройства, первый информационный вход блока управления является первым входом устройства, каждый блок регистра содержит мультиплексор и регистр, причем первый и второй входы блока регистра являются первым и

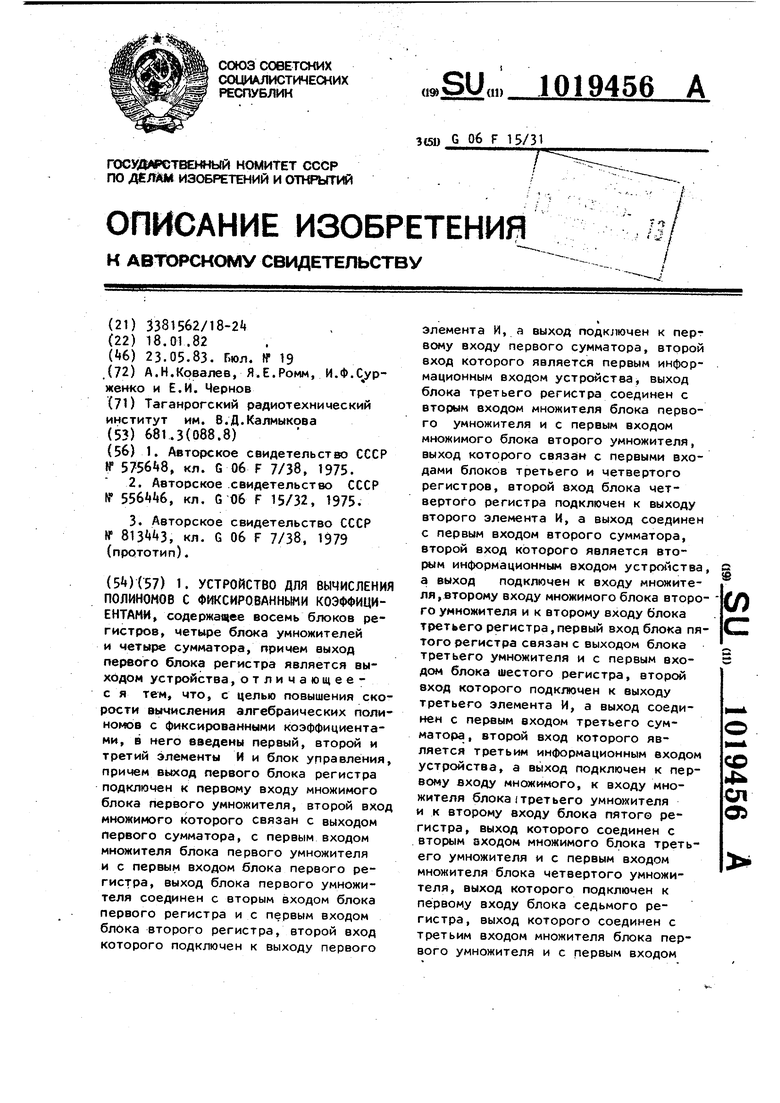

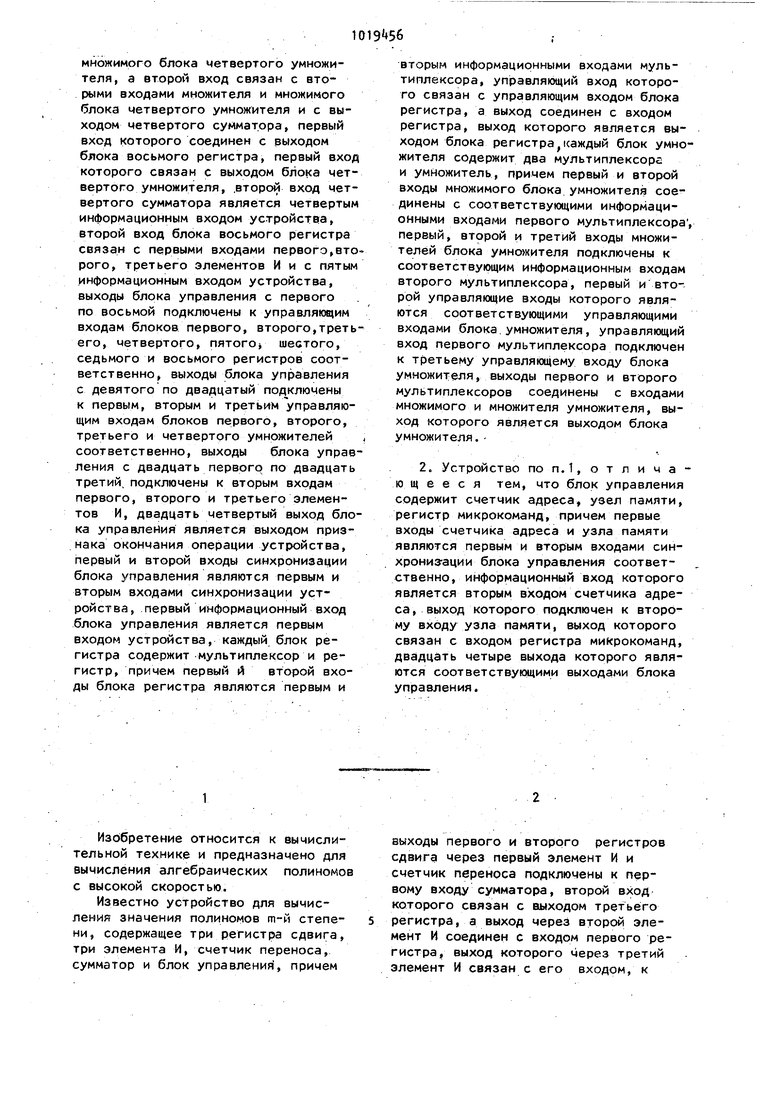

вторым информационными входами мультиплексора, управляющий вход которого связан с управляющим входом блока регистра, а выход соединен с входом регистра, выход которого является выходом блока регистра,каждый блок умножителя содержит два мультиплексор и умножитель, причем первый и второй входы множимого блока умножителя соединены с соответствующими информационными входами первого мультиплексора первый, второй и третий входы множителей блока умножителя подключены к соответствующим информационным входам второго мультиплексора, первый и второй управляющие входы которого являются соответствующими управляющими входами блока умножителя, управляющий вход первого мультиплексора подключен к третьему управляющему входу блока умножителя, выходы первого и второго мультиплексоров соединены с входами множимого и множителя умножителя, выход которого является выходом блока умножителя.2. Устройство по п.1, отличающее с я тем, что блок управления содержит счетчик адреса, узел памяти, регистр микрокоманд, причем первые входы счетчика адреса и узла памяти являются первым и вторым входами синхрониз-ации блока управления соответственно, информационный вход которого является вторым входом счетчика адреса, выход которого подключен к второму входу узла памяти, выход которого связан с входом регистра микрокоманд, двадцать четыре выхода которого являются соответствующими выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU813443A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Арифметическое устройство процессора быстрого преобразования Фурье | 1981 |

|

SU999061A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Модулярное устройство вычисления систем линейных алгебраических уравнений | 2015 |

|

RU2611963C1 |

| Устройство для вычисления полинома @ -ой степени | 1985 |

|

SU1305670A1 |

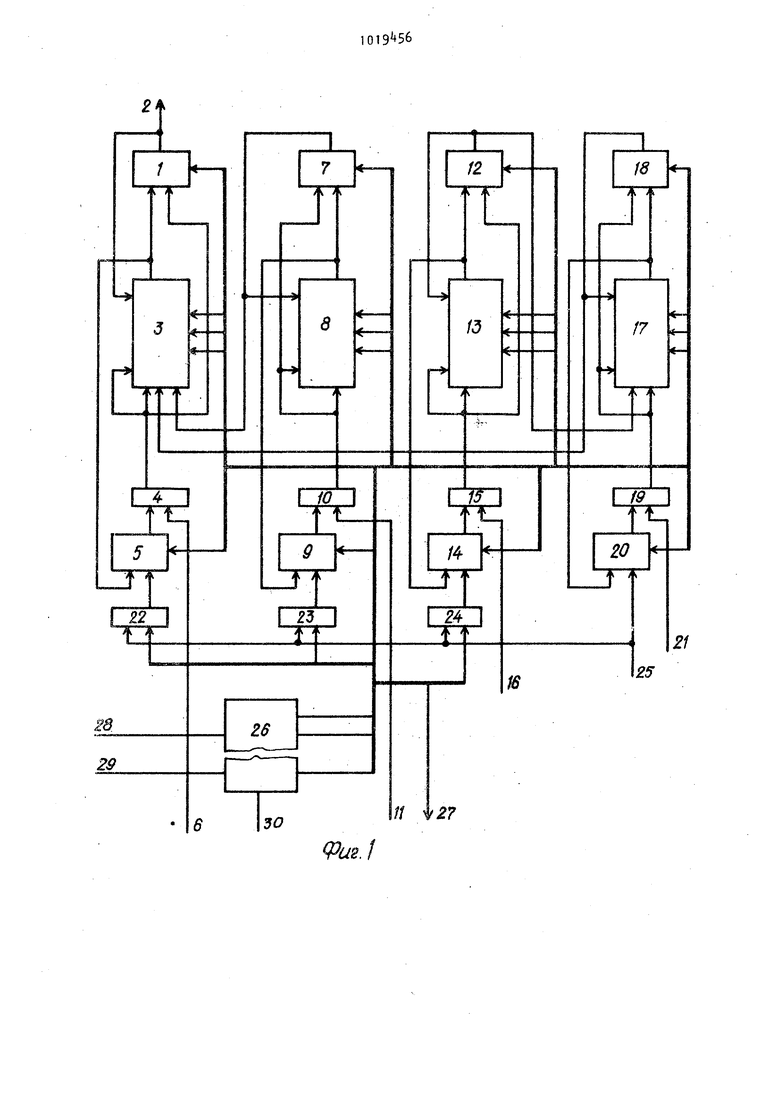

Изобретение относится к вычислительной технике и предназначено для вычисления алгебраических полиномов с высокой скоростью.

Известно устройство для вычисления значения полиномов т-й степени, содержащее три регистра сдвига, три элемента И, счетчик переноса, сумматор и блок управления , причем

выходы первого и второго регистров сдвига через первый элемент И и счетчик переноса подключены к первому входу сумматора, второй вход которого связан с выходом третьего регистра, а выход через второй элемент И соединен с входом первого регистра, выход которого через третий элемент И связан с его входом, к

31

управляющим входам трех регистров сдвига, счетчика переноса, сумматора, трех элементов И 13Однако 3Tq. устроистuo не может обеспечить необходимую скорость вычисления алгебраических полиномов.

Известно устройство для вычисления полиномов, содержащее сумматоры регистр, реверсивный счетчик, схему сравнения, элемент задержки, группу пар элементов И, три пары элементов И, причем сумматоры соединены последовательно через соответствующую пару элементов И группы, входы первог сумматора через пару элементов И группы соединены с выходом регистра , первый и второй выходы схемы сравнения соединены с первыми входами соответствующих элементов И всех трех пар, третий выход схемы сравнения соединен с вторыми входами элементов И первой пары, второго элемента И второй пар первого элемента И третьей пары и входом элемента задержки, выходы элементов И первой пары соединены с входом схемы сравнения, второй вход которого соединен с вторыми вх дами первого элемента И второй пары и второго элемента И третьей пары, третий вход схемы сравнения соединен с входом устройства, выходы элементов И второй пары соединены с входами соответствующих элементов И нечетных пар группы,а выходы элементов И третьей пары соединены входами соответствующих элементов И четНых пар группы t2 .

Однако такое устройство не может обеспечить необходимую скорость вычисления алгебраических полиномов.

Наиболее близким к изобретению является устройство для вычисления полиномов, содержащее блок первого регистра, вход которого соединен с выходом первого сумматора, первый вход которого подключен к первому выходу блока первого умножителя, второй вход первого сумматора, подключен к выходу первого буферного запоминающего устройства, третий вход первого сумматора соединен с первым выходом второго сумматора, первый вход которого связан с первым выходом блока второго умножителя , второй вход подключен к выходу второго блока буферного запоминаю9 564

щего устройства, второй выход соединен с входом блока второго регистра, а третий вход связан с первым выходом третьего сумматора, первый вход которого подключен к первому выходу блока третьего умножителя, второй вход - к выходу третьего блока буферного запоминающего устройства,второй выход связан с

10 входом блока третьего регистра, а третий вход соединен с первым выходом блока четвертого регистра, вход которого Подключен к выходу четвертого сумматора, первый вход которого

15 связан с выходом блока четвертого умножителя, а второй вход с выходом четвертого блока буферного запоминающего устройства, второй выход блока второго умножителя подключен к входу

20 блока пятого регистра,выход которого

I

соединен с первым входом множимого блока первого умножителя, первый вход множителя которого связан с выходом блока шестого регистра, первый

вход которого подключен к выходупервого блока буферного запоминающего устройства, а второй вход соединен с первым выходом блока первого регистра, второй выход которого является первым выходом устройства, второй выход блока первого умножителя связан с входом блока седьмого регистра , первым входом множимого бло,ка второго умножителя, первым входом множимого и первым входом множителя блока третьего умножителя, выход блока седьмого регистра подключен к второму входу множимого блока второго умножителя, первый вход

40 множителя которого соединен с выходом второго блока буферного запоминающего устрриства, а второй вход подключен к выходу блока второго регистра,первый выход блока девятого регистра

45 связан с вторым входом множителя блоков второго и первого умножителей, а также с вторым входом множимого блока первого умножителя, второй выход блока девятого регистра

50 соединен с вторым входом множимого блока третьего умножителя,первый вход блока десятого регистра подключен к выходу третьего блока буферного запоминающего устройства,

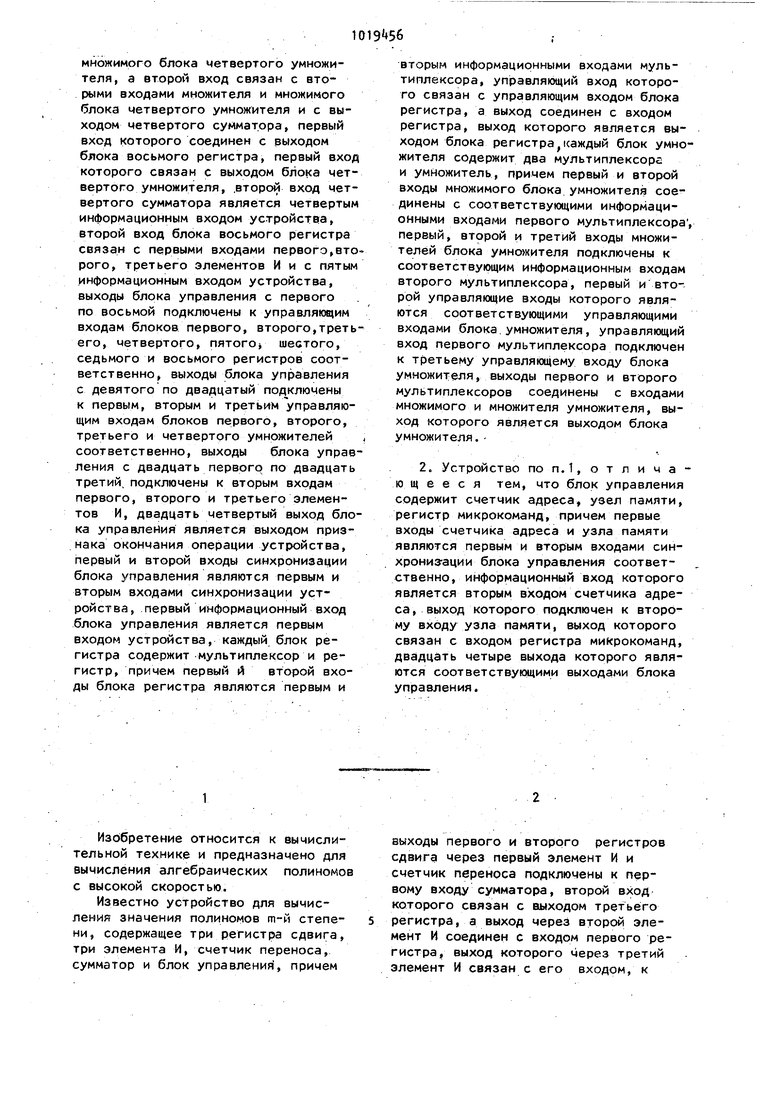

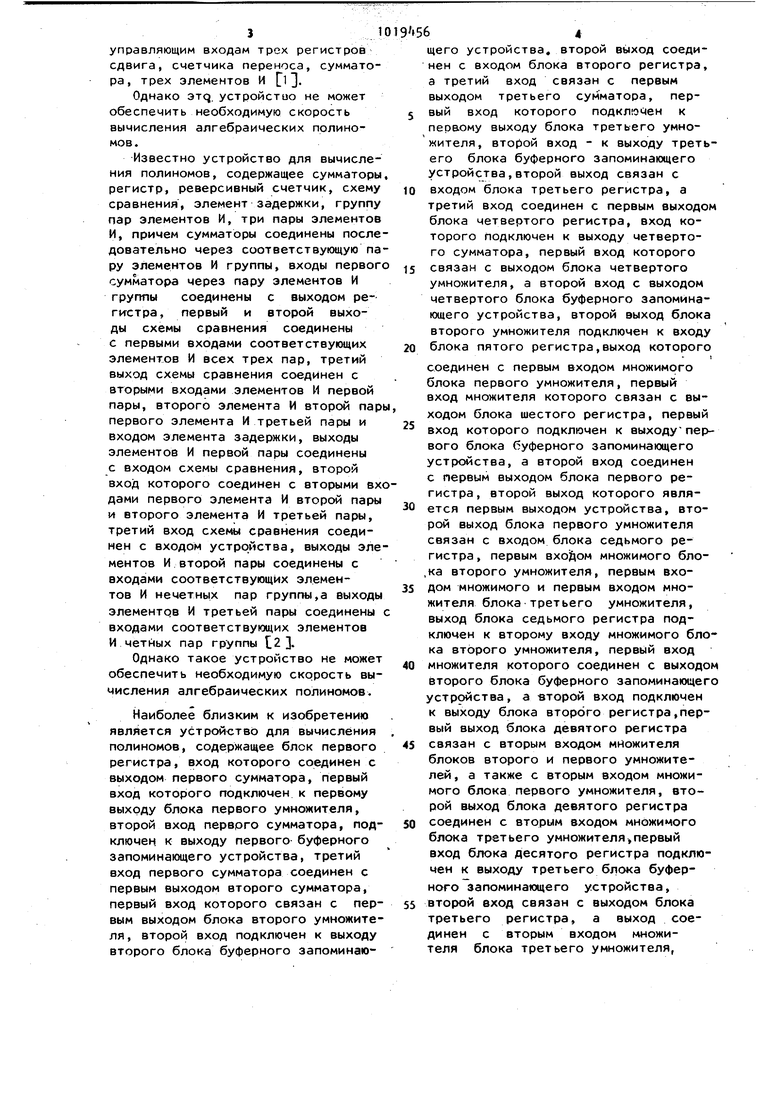

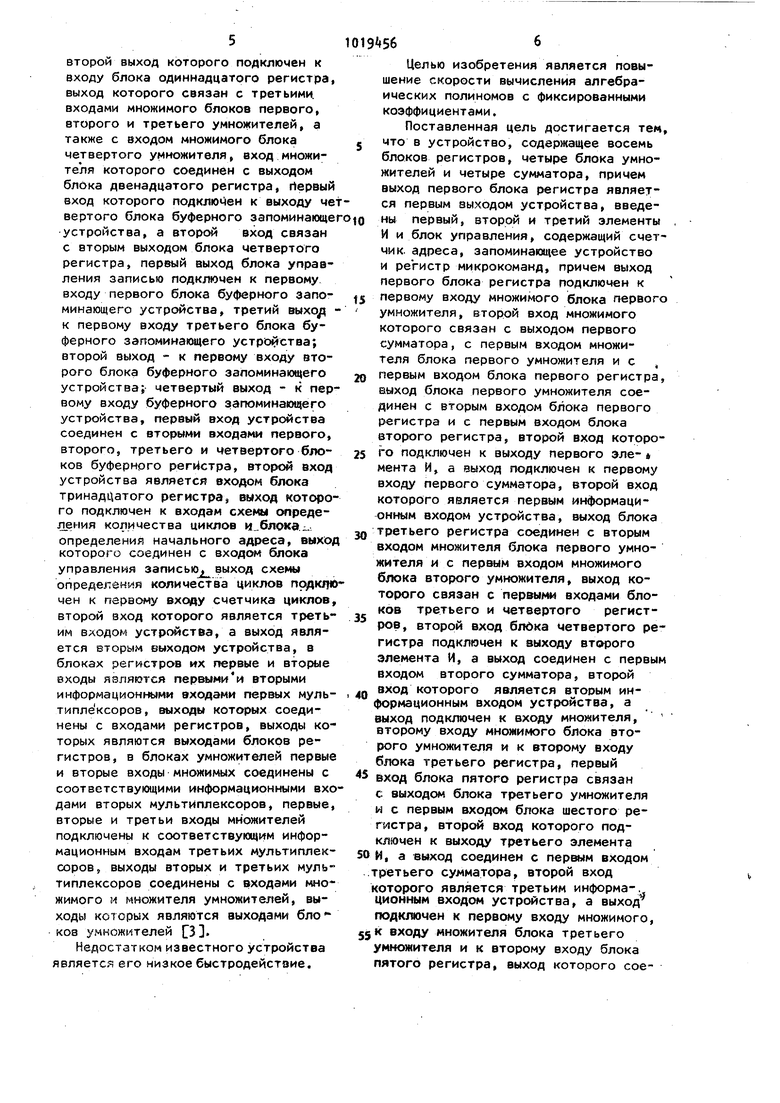

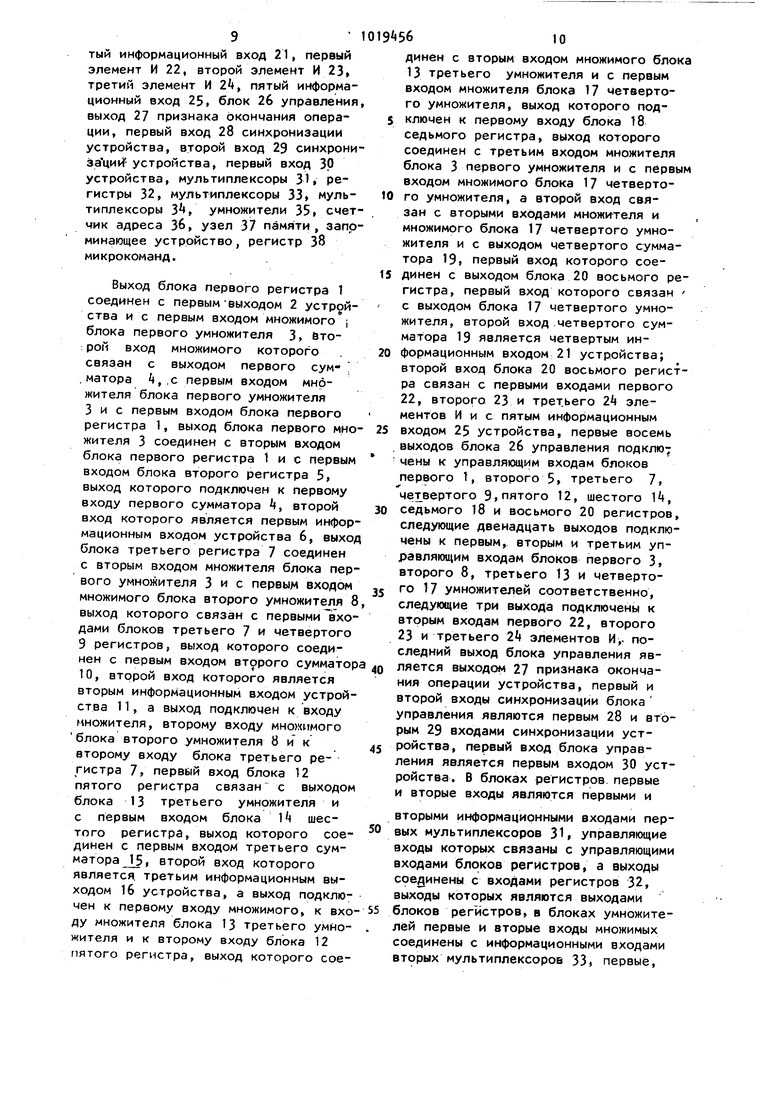

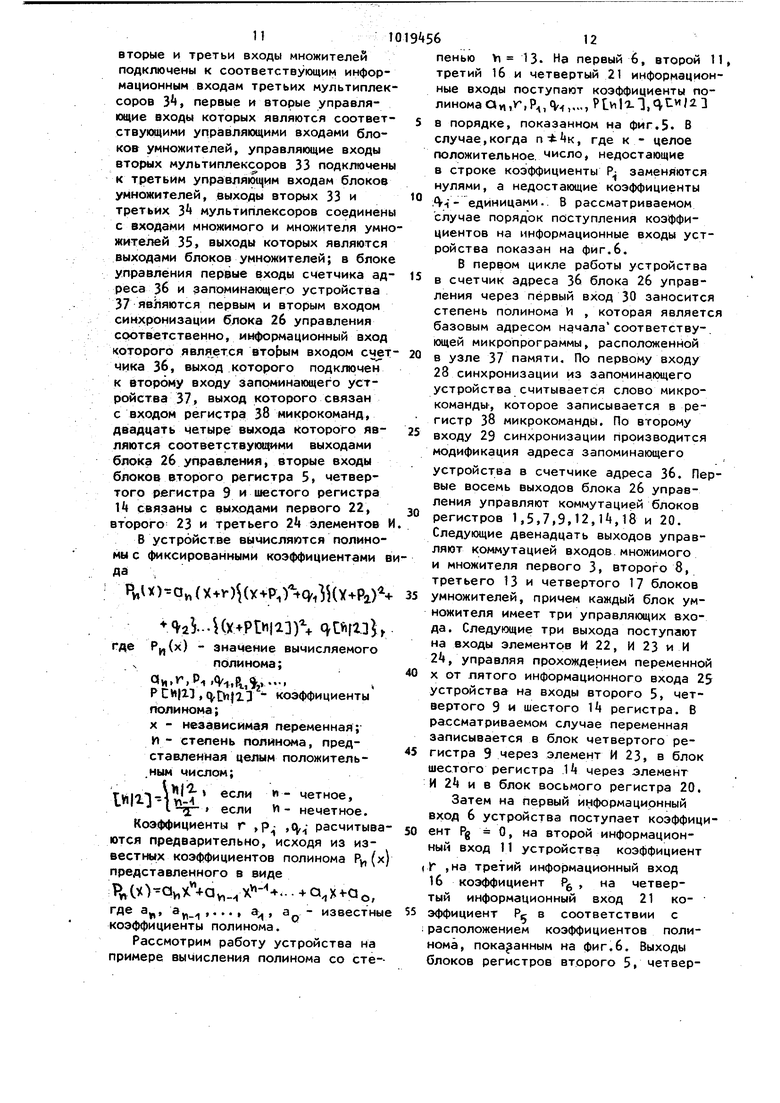

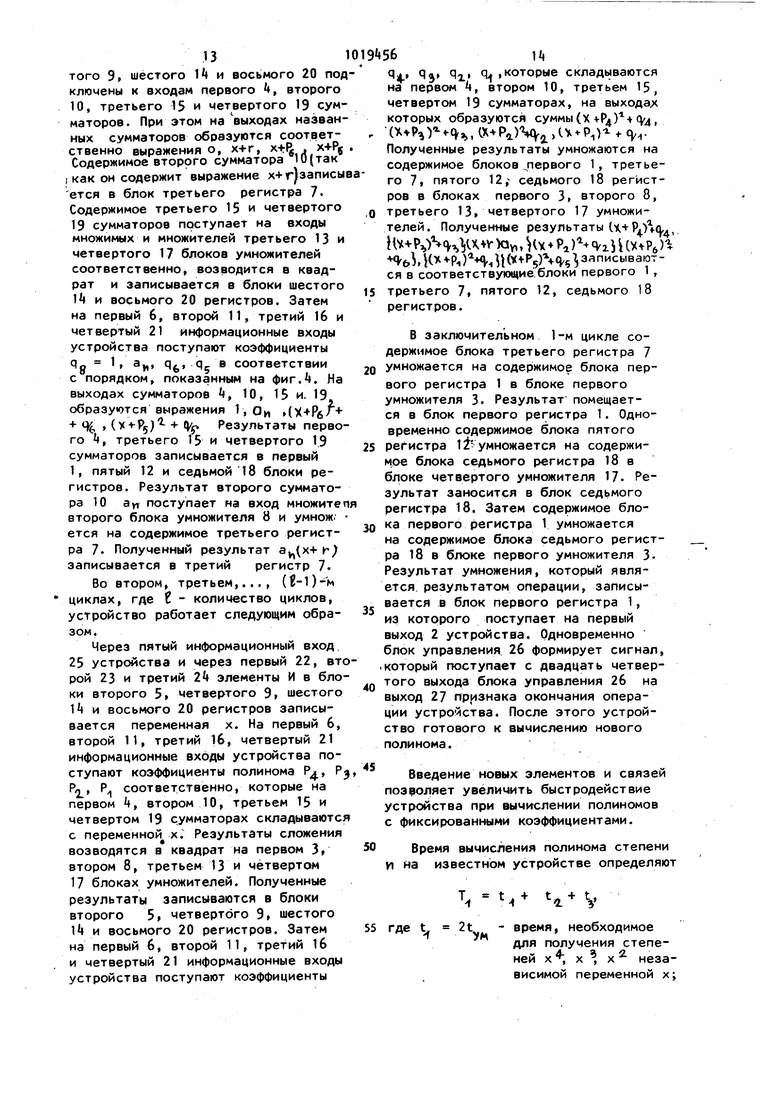

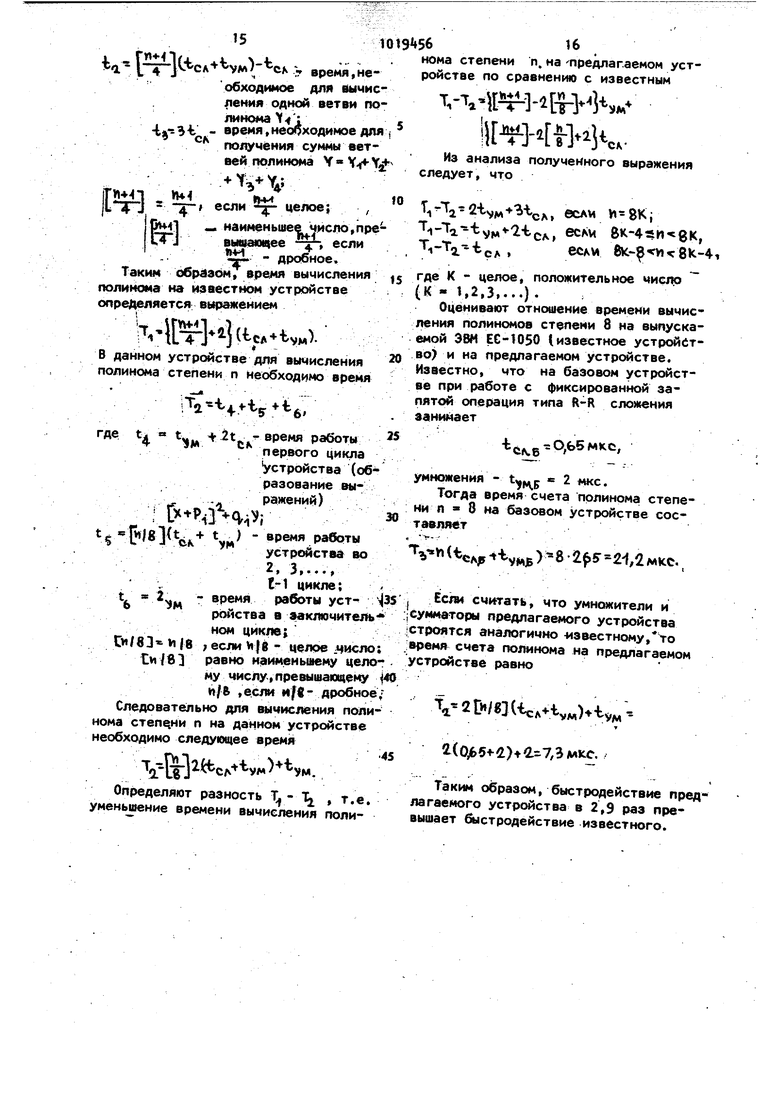

55 второй вход связан с выходом блока третьего регистра, а выход соединен с вторым входом множителя блока третьего умножителя, второй выход которого подключен к входу блока одиннадцатого регистра, выход которого связан с третьими, входами множимого блоков первого, второго и третьего умножителей, а также с входом множимого блока четвертого умножителя, вход множителя которого соединен с выходом блока двенадцатого регистра, первый вход которого подклю1 ен к выходу 4e вертого блока буферного запоминающе устройства, а второй вход связан с вторым выходом блока четвертого регистра, первый выход блока управления записью подключен к первому входу первого блока буферного запоминающего устройства, третий выхо к первому входу третьего блока буферного запоминающего устройства; второй выход - к первому входу второго блока буферного запоминающего устройства; четвертый выход - к пер вому входу буферного запоминающего устройства, первый вход устройства соединен с вторыми входами первого, второго, третьего и четвертого блоков буферного регистра, второй вход устройства является входом блока тринадцатого регистра, выход которого подключен к входам схемы определения количества циклов и блока... определения начального адреса, выход которого соединен с входом блока управления записью выход схемы определения количества циклов подкгмб чен к первому входу счетчика циклов, второй вход которого является третьим входом устройства, а выход является вторым выходом устройства, в блоках регистров их первые и вторые входы являются первыми и вторыми информационными входами первых мультиплексоров, выходы которых соединены с входами регистров, выходы ко торых являются выходами блоков регистров, в блоках умножителей первые и вторые входы множимых соединены с соответствующими информационными вхо дами вторых мультиплексоров, первые, вторые и третьи входы множителей подключены к соответствующим информационным входам третьих мультиплексоров , выходы вторых и третьих мультиплексоров соединены с входами множимого м множителя умножителей, выходы которых являются выходами бло ков умножителей З. Недостатком известного устройства является его низкое быстродейстаие. fSS6 Целью изобретения является повышение скорости вычисления алгебраических полиномов с фиксированными коэффициентами. Поставленная цель достигается тем, что в устройство, содержащее восемь блоков регистров, четыре блока умножителей и четыре сумматора, причем выход первого блока регистра является первым выходом устройства, введены первый, второй и третий элементы И и блок управления, содержащий счетчик, адреса, запоминающее устройство и регистр микрокоманд, причем выход первого блока регистра подключен к первому входу множимого блока первого умножителя, второй вход множимого которого связан с выходом первого сумматора, с первым входом множителя блока первого умножителя и с , первым входом блока первого регистра, выход блока первого умножителя соединен с вторым входом блока первого регистра и с первым входом блока вторюго регистра, второй вход которого подключен к выходу первого эле- мента И, а выход подключен к первому входу первого сумматора, второй вход KOTOpdro является первым информационным входом устройства, выход блока третьего регистра соединен с вторым входом множителя блока первого умножителя и с первым входом множимого блока второго умножителя, выход которого связан с первыми входами блоков третьего и четвертого регистров, второй вход блдка четвертого регистра подключен к выходу второго элемента И, а выход соединен с первым входом второго сумматора, второй вход которого является вторым информационным входом устройства, а выход подключен к входу множителя, второму входу множимого блока второго умножителя и к второму входу блока третьего регистра, первый вход блока пятого регистра связан с выходом блока третьего умножителя и с первым входом блока шестого реглстра, второй вход которого подключен к выходу третьего элемента и, а выход соединен с первым входом ретьего сумматора, второй вход оторого является третьим информа-. ционным входом устройства, а выход подкломен к первому входу множимого, к входу множителя блока третьего умножителя и к второму входу блока пятого регистра, выход которого соединен с вторым входом множимого блока третьего умножителя и с первым входом множителя блока четвертого умножителя, выход которого подключен к первому входу блока седьмого регистра, выход которого соединен с третьим входом множителя блока первого умножителя, и с первым входом множимого блока четвертого умножителя, а второй вход связан с вторыми входами множителя и множимого блока четвертого умножителя и с выходом четвертого сумматора, первый вход которого соединен с выходом бло ка восьмого регистра, первый вход ко торЪго связан с выходом блока четвер того умножителя, второй вход четвертого сумматора является четвертым информационным входом устройства, второй вход блока восьмого регистра связан с первьи 1и входами первого, второго и третьего элементов И и с пятым информационным входом устройства, выходы блока управления с первого по восьмой подключены к управляющим входам блоков первого, второг третьего, четвертого, пятого, шестого, седьмого и восьмого регистров соответственно, выходь блока управле имя с девятого по двадцатый подключе мы к первым, вгогшм и третьим управляющим входам блоков первого, второ го, третьего и четвертого умножителей, выходы блока управления с двадцатъ первого по двадцать третий подключены к вторым входам первого, второго и третьего элементов И, двад цать четвертый выход блока управления является выходом признака окончания операции устройства, первый и второй входы синхронизации блока управления являются первым и вторым входами синхронизации устройства, первый информационный вход блока управления является первым вхо дом устройства, каждый блок peiHcTp оодержит мультиплексор и регистр, причем первый и второй входы блока регистра являются первым и вторым информационными входами мультиплексора, управляющий вход которого свя зан с управляющим входом блока регистра, а выход соединен с входом регистра, выход которого является выходом блока регистра, каждый блок умножителя содержит два мультиплекс ра и умножитель, причем первый и второй входы множимого блока умножи теля соединены с соответствующими информационными входами первого мультиплексора, первый, второй и третий входы множителей блока умножителя подключены к соответствующим информационным входам второго мультиплексора, первый и второй управляющие входы которого являются соответствующими управляющими входами блока умножителя, управляющий вход первого мультиплексора подключен к третьему управлпкяцему входу блока умножителя, выходы первого и второго мультиплексоров соединены с входами множимого и множителя, выход KOTopqго является выходом блока умножителя. Блок управления содержит счетчик адреса, узел памяти, регистр микрокоманд, причем первые входы счетчика адреса и узла памяти являются первым и вторым входами синхронизации блока управления соответственно, информационный вход которого является вторым входом счетчика адреса, выход которого подключен к второму входу узла памяти, выход которого связан с входом регистра микрокоманд,, двадцать четыре выхода которого являются соответствующими выходами блока управления. На фиг.1 приведена структурная схема устройства ля вычисления полиномов; на фиг.2 - схема бхк5ка регистра; на фиг.З схема блока умножителя; на фиг. - схема блока управления; на фиг.5 - порядок поступления коэффициентов .полинома на информационные входы устройства в общем случае; на фиг.6 - то же, для случая, когда степень полинома m 13.,. . Устройство.содержит блок 1 первого регистра, первый выход 2, блок 3 первого умножителя, первый сумматор , блок 5 второго регистра, первый информационный вход 6, блок 7 третьего регистра, блок 8 второго умножителя, блок 9 четвертого регистра, второй сумматор 10, второй информационный вход 11, блок 12 пятого регистра блок 13 третьего умножителя, блок I шестого регистра, третий сумматор 15, третий информационный вход 16, блок 17 четвертого умножителя, блок 18 седьмого регистра, четвертый сумматор 19, блок 20 восьмого регистра, четвер9тый информационный вход 21, первый элемент И 22, второй элемент И 23, третий элемент И 24, пятый информационный вход 25, блок 26 управления выход 27 признака окончания операции, первый вход 28 синхронизации устройства, второй вход 23 синхрони sauMkT устройства, первый вход ЗР устройства, мультиплексоры 31, регистры 32, мультиплексоры 33, мультиплексоры 3, умножители 35, счет чик адреса Зб, узел 37 памяти, запо минающее устройство, регистр 38 микрокоманд. Выход блока первого регистра 1 соединен с первым-выходом 2 устройства и с первым входом множимого I блока первого умножителя 3, бторой вход множимого которого связан с выходом первого сум.матора 4,.с первым входом множителя блока первого умножителя 3 и с первым входом блока первого регистра 1, выход блока первого мно жителя 3 соединен с вторым входом блока первого регистра 1 и с первым входом блока второго регистра 5, выход которого подключен к первому входу первого сумматора 4, второй вход которого является первым инфор мационным входом устройства 6, выхо блока третьего регистра 7 соединен с вторым входом множителя блока пер вого умножителя 3 и с первым входом множимого блока второго умножителя 8 выход которого связан с первыми вхо дами блоков третьего 7 и четвертого 9 регистров, выход которого соединен с первым входом второго суммато 10, второй вход которого является вторым информационным входом устрой ства 11, а выход подключен к входу множителя, второму входу множимого блока второго умножителя 8 и к второму входу блока третьего регистра 7, первый вход блока 12 пятого регистра связан с выходом блока 13 третьего умножителя и с первым входом блока И шестого регистра, выход которого соединен с первым входом третьего сумматора JJ, второй вход которого является, третьим информационным выходом 16 устройства, а выход подключен к первому входу множимого, к вхо ду множителя блока 13 третьего умножителя и к второму входу блока 12 пятого регистра, выход которого сое6динен с вторым входом множимого блока 13 третьего умножителя и с первым входом множителя блока 17 четвертого умножителя, выход которого подключен к первому входу блока 18 седьмого регистра, выход которого соединен с третьим входом множителя блока 3 первого умножителя и с первым входом множимого блока 17 четвертого умножителя, а второй вход связан с вторыми входами множ14теля и множимого блока 17 четвертого умножителя и с выходом четвертого сумматора 19, первый вход которого соединен с выходом блока 20 восьмого регистра, первый вход которого связан с выходом блока 17 четвертого умножителя, второй вход четвертого суммаТора 19 является четвертым информационным входом 21 устройства; второй вход блока 20 восьмого регист ра связан с первыми входами первого 22, второго 23 и третьего 2 элементов И и с пятым информационным входом 25 устройства, первые восемь выходов блока 26 управления подклю чены к управляющим входам блоков первого 1, второго 5, третьего 7, четвертого 9,пятого 12, шестого Т, седьмого 18 и восьмого 20 регистров, следующие двенадцать выходов подключены к первым, вторым и третьим управляющим входам блоков первого 3, второго 8, третьего 13 и четвертого 17 умножителей соответственно, следующие три выхода подключены к вторым входам первого 22, второго 23 и третьего 2 элементов И,- последний выход блока управления является выходом 27 признака окончания операции устройства, первый и второй входы синхронизации блока управления являются первым 28 и вторым 29 входами синхронизации устройства, первый вход блока управления является первым входом 30 устройства. В блоках регистров первые и вторые входы являются первыми и вторыми информационными входами первых мультиплексоров 31, управляющие входы которых связаны с управляющими входами блоков регистров, а выходы соединены с входами регистров 32, выходы которых являются выходами блоков регистров, в блоках умножителей первые и вторые входы множимых соединены с информационными входами вторых мультиплексоров 33, первые. вторые и третьи входы множителей подключены к соответствующим информационным входам третьих мультиплек соров З, первые и вторые управляющие входы которых являются соответ ствующими управляющими входами блоков умножителей, управляющие входы вторых мультиплексоров 33 подключен к третьим управлякнцим входам блоков умножителей, выходы вторых 33 и третьих 3 мультиплексоров соединен с входами множимого и множителя умн жителей 35, выходы которых являются выходами блоков умножителей; в блок управления первые входы счетчика ад реса Зб и запоминающего устройства 37 являются первым и вторым входом синхронизации блока 2б управления ссютветственно, информационный вход которого является вторым входом счет чика 36, выход которого подк/яочен к второму входу запоминающего устройства 37, выход которого связан с входом регистра 38 микрокоманд, двадцать четыре выхода которого являются соответствующими выходами блока 26 упраеления, вторые входы блоков второго регистра 5, четвертого регистра 9 и шестого регистра 1Л связаны с выходами первого 22, второго 23 и третьего 21 элементов В устройстве вычисляются полиномы с фиксированными коэффициентами да Pv,U),(X-nr)(X+P:,)-fq)HY+P2) Л25.-Их Р1и}13)% где значение вычисляемого полинома; C«v,,r,P-,,V.p,4,..., PCHjll ,t{. - коэффициенты полинома; X - независимая переменная; И- степень полинома, представленная целым положитель.ным числом; Ul и- четное, -ttiil. И- нечетное. Коэффициенты г ,р ,с,- расчитыва ются предварительно, исходя из известнь,х коэффициентов полинома Р„ (х представленного в виде :Ц,(У )С1у,Х. ау, X + Q/jX- Qo, где а, а,..., а , а - известны коэффициенты полинома. Рассмотрим работу устройства на примере вычисления полинома со стеЮб12 пенью Vi 13. На первый 6, второй 11, третий 16 и четвертый 21 информационные входы поступают коэффициенты полиномаац,г,Р,с,..,,Р1и|а.1,Ч в порядке, показанном на фиг.5 В случае,когда , где к - целое положительное, число, недостающие в строке коэффициенты Р заменяются нулями, а недостающие коэффициенты ,V-i- единицами.. В рассматриваемом случае порядок поступления коэффициентов на информационные входы устройства показан на фиг.6. В первом цикле работы устройства в счетчик адреса Зб блока 26 управления через первый вход 30 заносится степень полинома И , которая является базовым адресом началасоответству-, ющей микропрограммы, расположенйой в узле 37 памяти. По первому входу 28 синхронизации из запоминающего устройства считывается слово микрокoмaндь, которое записывается в регистр 38 микрокоманды. По второму входу 29 синхронизации производится модификация адреса запоминающего устройства в счетчике адреса 36. Первые восемь выходов блока 26 управления управляют коммутацией блоков регистров 1,5,7,9,12,1i,l8 и 20. Следующие двенадцать выходов управляют коммутацией входов множимого и множителя первого 3, второго 8, третьего 13 и четвертого 17 блоков умножителей, причем каждый блок умножителя имеет три управлящих входа. Следующие три выхода поступают на входы элементов И 22, И 23 и И 2, управляя прохождением переменной X от пятого информационного входа 2S устройства на входы второго 5, четвертого 9 и шестого 1 регистра. В рассматриваемом случае переменная записывается в блок четвертого регистра Э через элемент И 23, в блок шестого регистра Н через элемент И 2) и в блок восьмого регистра 20. Затем на первый информационный вход 6 устройства поступает коэффициент Pg 0, на второй информацион„ый вход 11 устройства коэффициент :.. информационный вход , коэффициент Р . на четвертый информационный вход 21 коэффициент Р в соответствии с расположением коэффициентов полинома, показанным на фиг.6. Выходы блоков регистров второго 5, четвер13того 9, шестого И и восьмого 20 под ключены к входам первого , второго 10, третьего 15 и четвертого 19 сумматоров. При этом на выходах названных сумматоров образуются соответственно выражения о, х+г, . д, Содержимое второго сумматора 10(так ; как он содержит выражение х+г)записы ется в блок третьего регистра 7. Содержимое третьего 15 и четвертого 19 сумматоров поступает на входы множимых и множителей третьего 13 и четвертого 17 блоков умножителей соответственно, возводится в квадрат и записывается в блоки шестого I и восьмого 20 регистров. Затем на первый 6, второй 11, третий 16 и четвертый 21 информационные входы устройства поступают коэффициенты Pg 1 а,,, q, q в соответствии с порядком, показанным на фиг.. На выходах сумматоров Ц, 10, 15 и. 19 образуются выражения 1, Оц ( + 9, , (Ki-Pj} + Результаты первого , третьего 15 и четвертого 19 сумматоров записывается в первый 1, пятый 12 и седьмой 18 блоки регистров. Результат второго сумматора 10 an поступает на вход множитеп второго блока умножителя 8 и умнож. ется на содержимое третьего регистра 7. Полученный результат ау(х+ ) записывается в третий регистр 7. Во втором, третьем,..., (В-1)-м циклах, где t - количество циклов, устройство работает следующим образом. Через пятый информационный вход. 25 устройства и через первый 22, вто рой 23 и третий 2 элементы И в блоки второго 5, четвертого 9, шестого 1 и восьмого 20 регистров записывается переменная х. На первый 6, второй 11, третий 16, четвертый 21 информационные входы устройства поступают коэффициенты полинома Р, Pj P/j, Р соответственно, которые на первом kf втором 10, третьем 15 и четвертом 19 сумматорах складываются с переменной х; Результаты сложения возводятся в квадрат на первом 3, втором 8, третьем 13 и четвертом 17 блоках умножителей. Полученные результаты записываются в блоки второго 5, четвертого 9, шестого И и восьмого 20 регистров. Затем на первый 6, второй 11, третий 16 и четвертый 21 информационные входы устройства поступают коэффициенты 5б11, 44. Я а Чх Ч , которые складываются на первом 4, втором 10, третьем 15, четвертом 19 сумматорах, на выхода которых образуются суммы(х )4 фд (P%),)H2. V4Полученные результаты умножаются на содержимое блоков .первого 1, третьего 7, пятого 12, седьмого 18 регистров в блоках первого 3, второго 8, третьего 13, четвертого 17 умножителей. Полученные результаты )(л, ) toy,, Нч PI) tvii i )М и 5 Ф5 записываются в соответствующие блоки первого 1 , третьего 7, пятого 12, седьмого 18 регистров. В заключительном 1-м цикле содержимое блока третьего регистра 7 умножается на содержимое блока первого регистра 1 в блоке первого умножителя 3. Результат помещается в блок первого регистра 1. Одновременно содержимое блока пятого регистра llумножается на содержим.ое блока седьмого регистра 18 в блоке четвертого умножителя 17. Результат заносится в блок седьмого регистра 18. Затем содержимое блока первого регистра 1 умножается на содержимое блока седьмого регистра 18 в блоке первого умножителя 3. Результат умножения, который является результатом операции, записывается в блок первого регистра 1, из которого поступает на первый выход 2 устройства. Одновременно блок управления 26 формирует сигнал, который поступает с двадцать четвертого выхода блока управления 26 на выход 27 признака окончания операции устройства. После этого устройство готового к вычислению нового полинома. Введение новых элементов и связей позволяет увеличить быстродействие устройства при вычислении полиномов с фиксированными коэффициентами. Время вычисления полинома степени И на известном устройстве определяют Ч V 2t - время, необходимое для получения степеней X , X X независимой переменной х; 1 время,необходимое для вычисления одной ветви полинома : -гЗ-Ь - время,нео(5ходимое дня получения суммы ветвей полинома Ч Ч Y w n - целое; « наименьшее число,превыоююцеепи дробное. Таким о6рдэом7 Время вычисления полинома на известном устройстве определяется выражением i lDT:l ttc +tv«. в данном устройстве для вычисления полинома степени п необходимо время Ч (и -V 2t|,| время работы первого цикла Устройства (образование выражений) : р| 18 {t + t) - время работы устройства во 5,««, t-1 цикле; V м - время работы уст ройства в эaкm читeлitl ном цикпе; Си/83 и 18 ; если Vife целое лисло Пи 183 равж) наименьшему цело му числу, превышающе и/6 .если и/в- дробное Следовательно для вычисления поли нома степени п на данном устройстве необходимо следующее время . Определяют разность Т - 1 , т.е. уменьшение времени вычисления полинома степени п. на Предлагаемом устройстве по сравнению с известным T,-7,MIiJiMtf JSM . Из анализа полученного выражения следует, что 1 2 2tvM+ 4A, есАМ Vi 8Кj Т -Та-t j -l-bcA, есХц 8К-4: И 8К, ,еслч ftc M c8K-4t где К - целое, положительное число (К - 1,2,3,...)Оценивают отношение времени вычисления полиномов степени 8 на выпускаемой ЪШ ЕС-1050 (известное устройство) и на предлагаемом устройстве. Известно, что на базовом устройстве при работе с фиксированной запятой операция типа R-R сложения занимает fecN5-0,feSMKo, умножения - « 2 «кс. Тогда время счета полинома степени л 8 на базовом устройстве составляет). Ecie считать, что умножители и еумматоры предлагаемого устройства строятся аналогично + звестному,Чо время счета полинома на предлагаемом устройстве равно ()+iv,,-. 2()+2.г7,Змкс. Таким образом, быстродействие предлагаемого устройства в 2,9 раз превышает &1стродействие известного.

ш.

Фив.2

(Pu2:3

7W

US

Qn ГЖ

9-9

г

P4

.1.

(Рие.5

PeO

B-f

an

Яг

/V

«

)-: 1Ж2

i.

А

я.

1

Рб

Pf

95А

е

z

фиг. 6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аккумуляторная батарея | 1926 |

|

SU5756A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1983-05-23—Публикация

1982-01-18—Подача