Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных системах, работающих в реальном мас- mta6e времени.

Цель изобретения - повышение быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов.

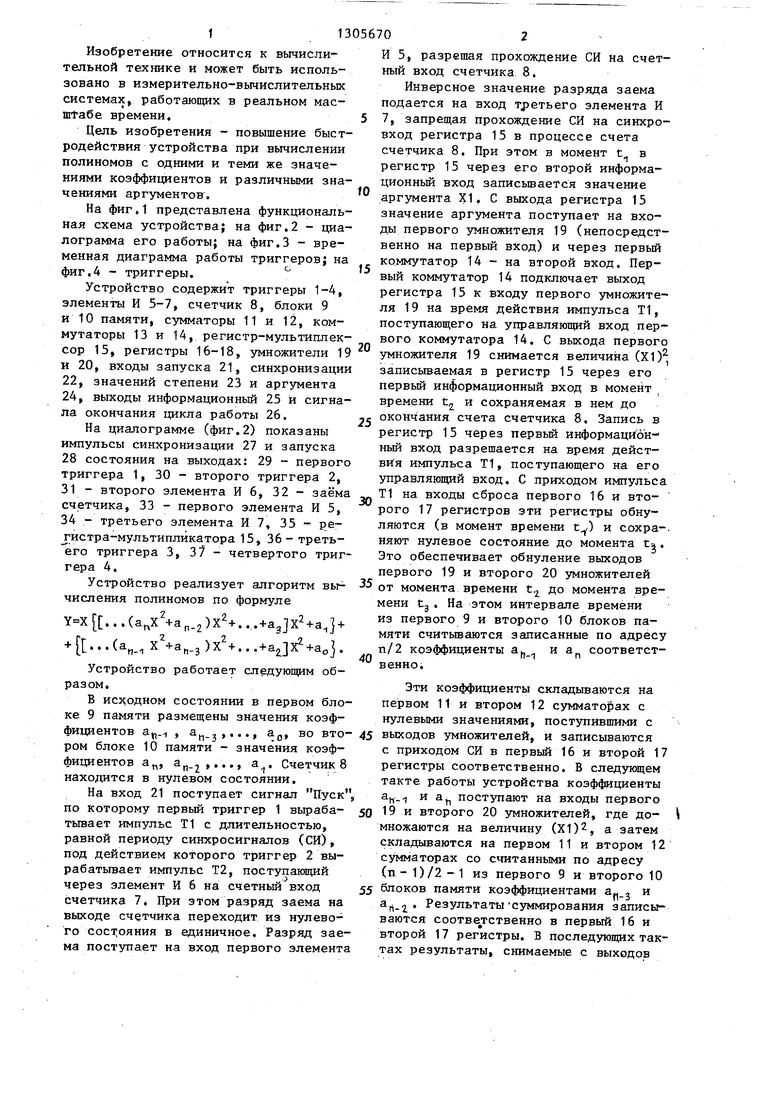

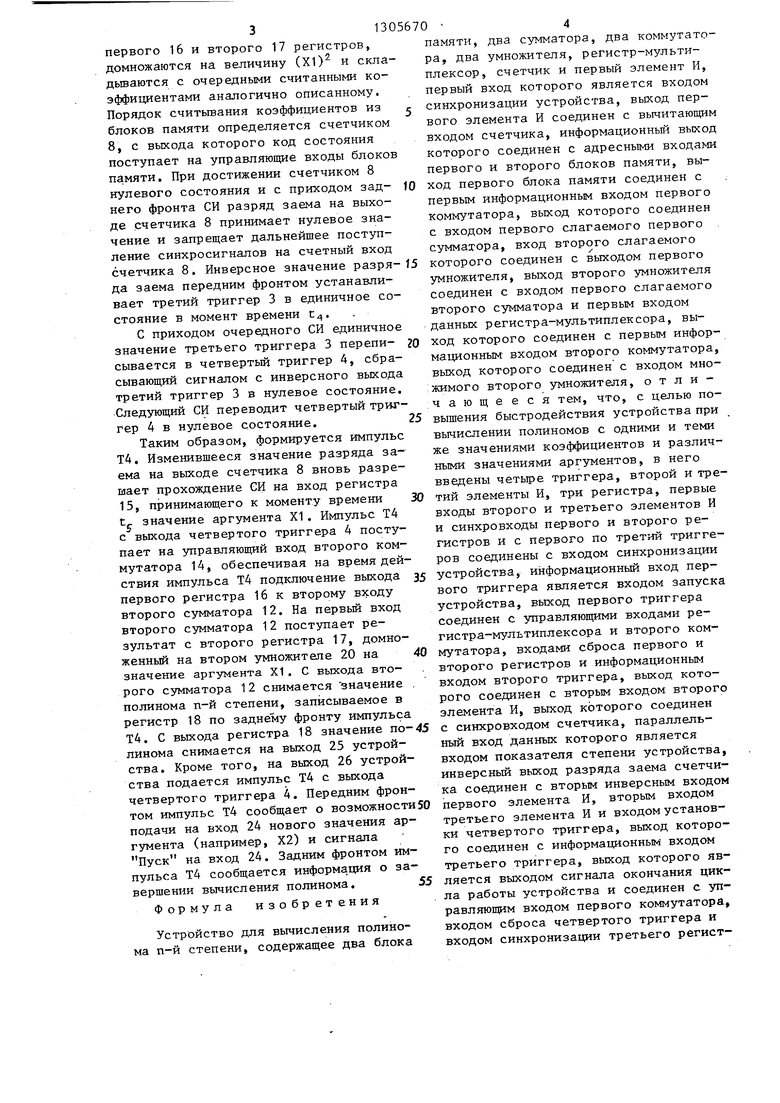

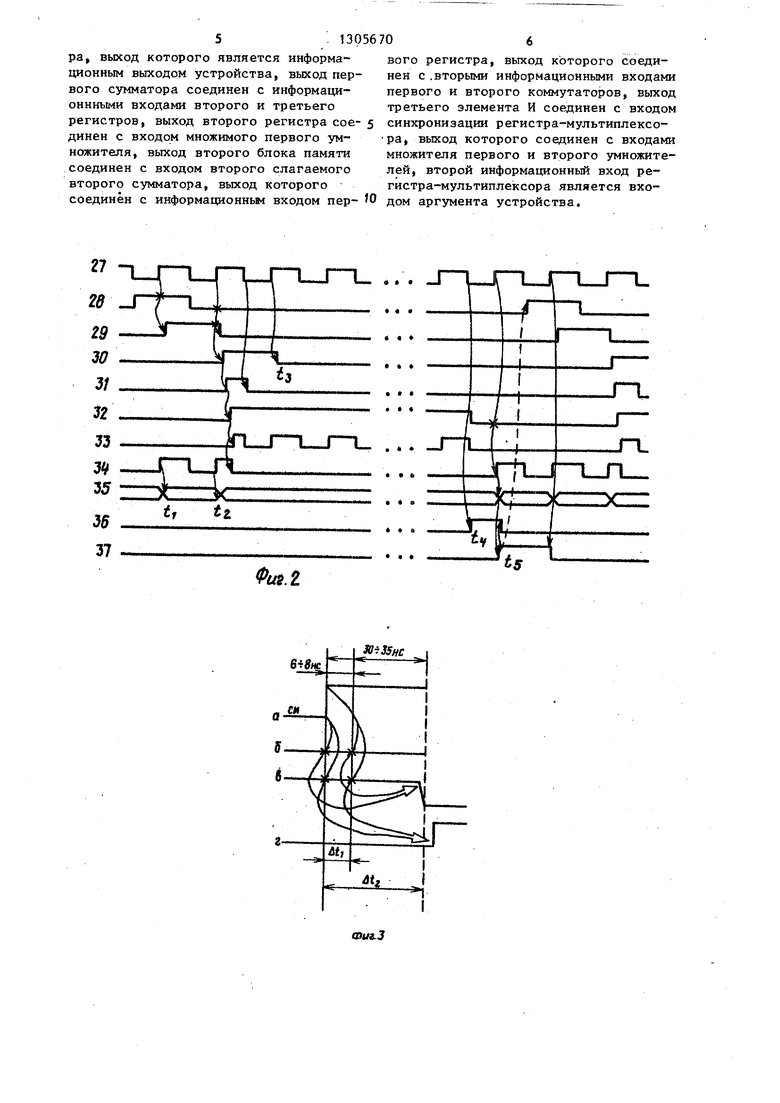

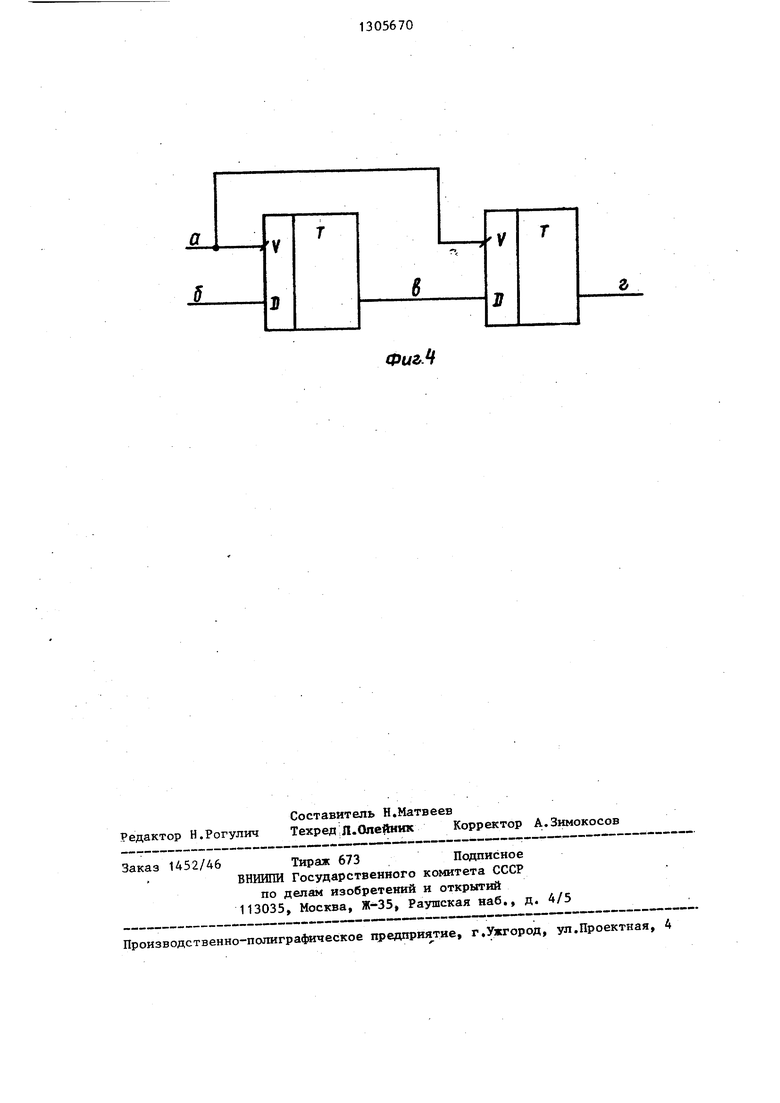

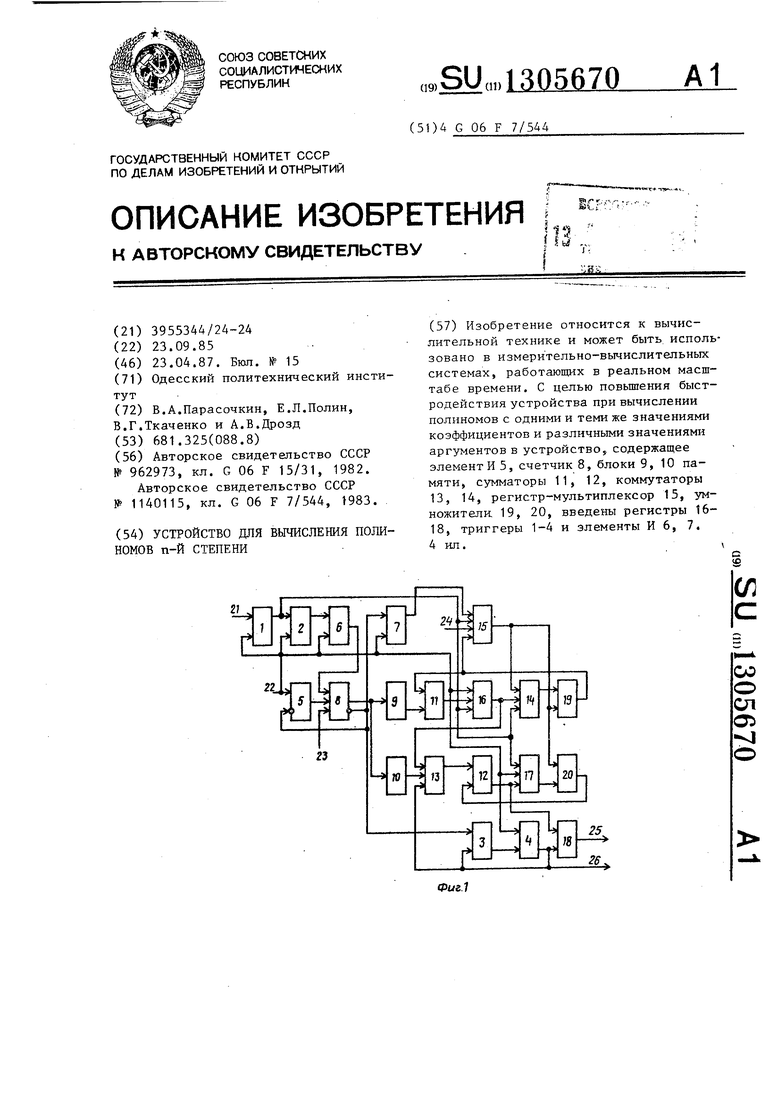

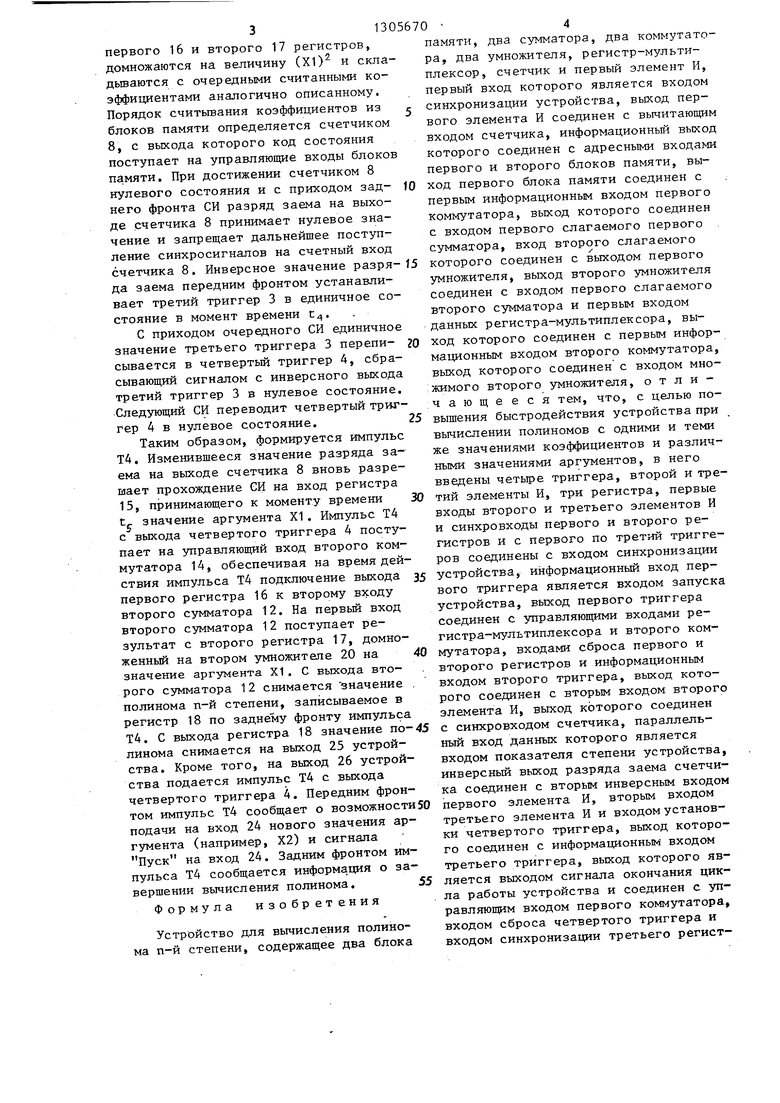

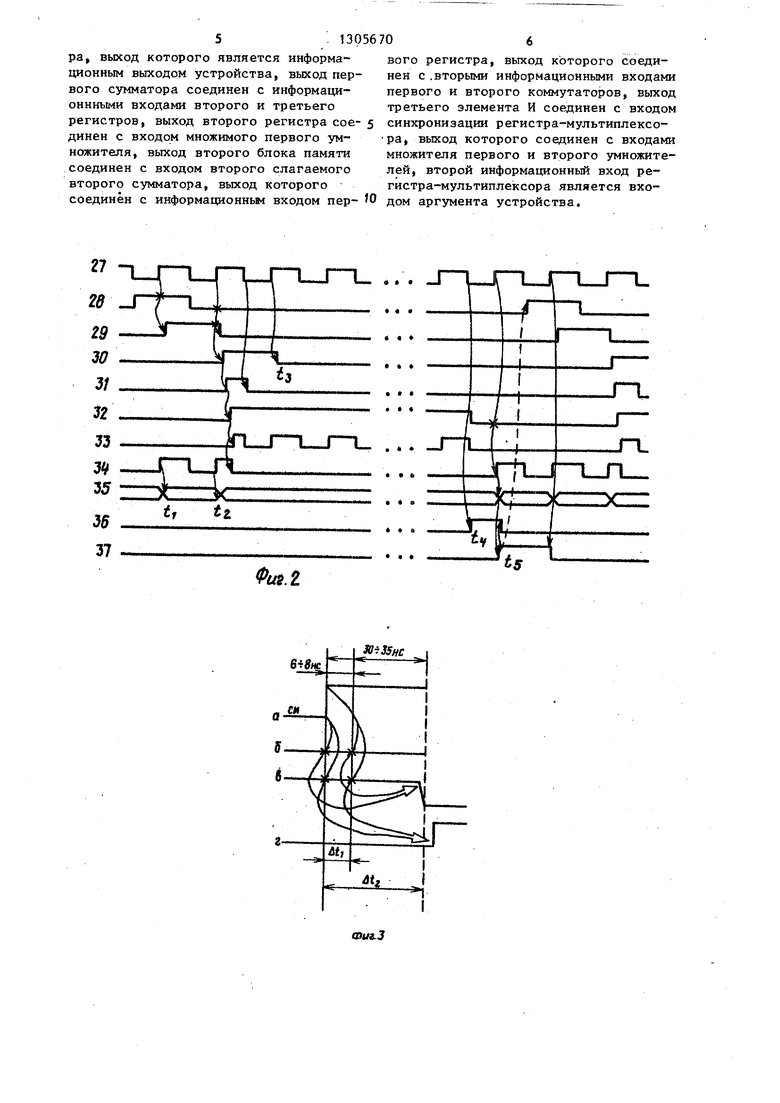

На фиг,1 представлена функциональная схема устройства; на фиг.2 - циа- лограмма его работы; на фиг.З - временная диаграмма работы триггеров; на фиг.4 - триггеры.

Устройство содержит триггеры 1-4, элементы И 5-7, счетчик 8, блоки 9 и 10 памяти, сумматоры 11 и 12, коммутаторы 13 и 14, регистр-мультиплексор 15, регистры 16-18, умножители 19 и 20, входы запуска 21, синхронизации 22, значений степени 23 и аргумента 24, выходы информационньй 25 и сигнала окончания цикла работы 26.

На циалограмме (фиг.2) показаны импульсы синхронизации 27 и запуска 28 состояния на выходах: 29 - первого триггера 1, 30 - второго триггера 2, 31 - второго элемента И 6, 32 - заёма счетчика, 33 - первого элемента И 5, 34 - третьего элемента И 7, 35 - ре- Jиcтpa-мyльтиплйкaтopa 15, 36 - треть- его триггера 3, 37 - четвертого триггера 4.

Устройство реализует алгоритм вьг числения полиномов по формуле

... ( .2 ). .., + + ... (а . )....

Устройство работает следующим образом.

В исходном состоянии в первом блоке 9 памяти размещены значения коэффициентов а.1 , а

ром блоке 10 фициентов а

п-3

0,

во ВТО- 45 выходов умножителей, и записываются

памяти - значения коэф-

п

Счетчик 8

находится в нулевом состоянии.

На вход 21 поступает сигнал Пуск, по которому первый триггер 1 вырабатывает импульс Т1 с длительностью, равной периоду синхросигналов (СИ), под действием которого триггер 2 вы- рабатьшает импульс Т2, поступанщий через элемент И 6 на счетньй вход счетчика 7. При этом разряд заема на выходе счетчика переходит из нулевого сост ояния в единичное. Разряд заема поступает на вход первого элемента

с приходом СИ в первый 16 и второй 1 регистры соответственно. В следующем такте работы устройства коэффициенты а. fi поступают на входы первого

50 19 и второго 20 умножителей, где до- множаются на величину (Х1)2, а затем складываются на первом 11 и втором 1 сумматорах со считанными по адресу (п - 1)/2 - 1 из первого 9 и второго 1

55 блоков памяти коэффициентами а- и . . Результаты суммирования записы ваются соотве гственно в первый 16 и второй 17 регистры. В последующих та тах результаты, снимаемые с выходов

5

0

5

0

5

И 5, разрешая прохождение СИ на счетный вход счетчика 8.

Инверсное значение разряда заема подается на вход тд етьего элемента И 7, запрещая прохождение СИ на синхро- вход регистра 15 в процессе счета счетчика 8. При этом в момент t в регистр 15 через его второй информа- ционньй вход записьгоается значение аргумента XI, С выхода регистра 15 значение аргум€ нта поступает на входы первого з ножителя 19 (непосредственно на первый вход) и через первый коммутатор 14 - на второй вход. Первый коммутатор 14 подключает выход регистра 15 к входу первого умножителя 19 на время действия импульса Т1, пост упающего на управляющий вход первого коммутатора 14. С выхода первого ут ножителя 19 снимается величина (XI ) записьгоаемая в регистр 15 через его первьй информационный вход в момент времени t и сохраняемая в нем до окончания счета счетчика 8. Запись в регистр 15 через первьй информационный вход разрешается на время действия импульса Т1, поступающего на его управляющий вход. С приходом импульса Т1 на входы сброса первого 16 и второго 17 регистров эти регистры обнуляются (в момент времени t,) и сохра-. няют нулевое состояние до момента t. Это обеспечивает обнуление выходов первого 19 и второго 20 умножителей

0

от момента времени t, до момента времени tj. На этом интервале времени из первого 9 и второго 10 блоков памяти считываются записанные по адресу п/2 коэффициенты а п соответственно.

Эти коэффициенты складываются на первом 11 и втором 12 суммато)ах с нулевыми значениями, поступившими с

с приходом СИ в первый 16 и второй 17 регистры соответственно. В следующем такте работы устройства коэффициенты а. fi поступают на входы первого

50 19 и второго 20 умножителей, где до- множаются на величину (Х1)2, а затем складываются на первом 11 и втором 12 сумматорах со считанными по адресу (п - 1)/2 - 1 из первого 9 и второго 10

55 блоков памяти коэффициентами а- и . . Результаты суммирования записываются соотве гственно в первый 16 и второй 17 регистры. В последующих тактах результаты, снимаемые с выходов

первого 16 и второго 17 регистров, домножаются на величину (Х1) и скла- дьтаются с очередными считанными коэффициентами аналогично описанному. Порядок считьгеания коэффициентов из блоков памяти определяется счетчиком 8, с выхода которого код состояния поступает на управляющие входы блоков памяти. При достижении счетчиком 8 нулевого состояния и с приходом заднего фронта СИ разряд заема на выходе счетчика 8 принимает нулевое значение и запрещает дальнейшее поступление синхросигналов на счетный вход

счетчика 8, Инверсное значение разря-15 которого соединен с выходом первого да заема передним фронтом устанавливает третий триггер 3 в единичное состояние в момент времени t.

С приходом очередного СИ единичное значение третьего триггера 3 перепи- 20 ход которого соединен с первым инфор- сывается в четвертый триггер 4, сбрасывающий сигналом с инверсного выхода третий триггер 3 в нулевое состояние. Следующий СИ переводит четвертый тригумножителя, выход второго умножителя соединен с входом первого слагаемого второго сумматора и первым входом данных регистра-мультиплексора, вымационным входом второго коммутатора, выход которого соединен с входом множимого второго умножителя, о т л и - ч ающе е ся тем, что, с целью погер 4 в нулевое состояние.

Таким образом, формируется импульс Т4. Изменившееся значение разряда заема на выходе счетчика 8 вновь разрешает прохождение СИ на вход регистра 15, принимающего к моменту времени tf значение аргумента Х1. Импульс Т4 с вькода четвертого триггера 4 поступает на управляющий вход второго коммутатора 14, обеспечивая на время действия импульса Т4 подключение выхода первого регистра 16 к второму входу второго сумматора 12. На первьй вход второго сумматора 12 поступает результат с второго регистра 17, домно- женный на втором умножителе 20 на значение аргумента Х1. С выхода вто рого сумматора 12 снимается значение полинома п-й степени, записываемое в регистр 18 по заднему фронту импульса

инверсный выход разряда заема счетчика соединен с вторым инверсным входом

Т4. С выхода регистра 18 значение по-45 с синхровходом счетчика, параллель- линома снимается на выход 25 устрой- ный вход данных которого является ства. Кроме того, на выход 26 устрой- входом показателя степени устройства, ства подается импульс Т4 с выхода четвертого триггера 4. Передним фронтом импульс Т4 сообщает о возможности50 первого элемента И, вторым входом подачи на вход 24 нового значения ар- третьего элемента И и входом установ- гумента (например, Х2) и сигнала Пуск на вход 24. Задним фронтом импульса Т4 сообщается информация о завершении вычисления полинома. 55 Формула изобретения

ки четвертого триггера, выход которого соединен с информационным входом третьего триггера, выход которого является выходом сигнала окончания цикла работы устройства и соединен с управляющим входом первого коммутатора, входом сброса четвертого триггера и входом синхронизации третьего регист-

Устройство для вычисления полинома п-й степени, содержащее два блока

памяти, два сумматора, два коммутатора, два умножителя, регистр-мультиплексор, счетчик и первый элемент И, первый вход которого является входом синхронизации устройства, выход первого элемента И соединен с вьиитающим входом счетчика, информационньм выход которого соединен с адресными входами первого и второго блоков памяти, выход первого блока памяти соединен с первым информационным входом первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого

которого соединен с выходом первого

ход которого соединен с первым инфор-

умножителя, выход второго умножителя соединен с входом первого слагаемого второго сумматора и первым входом данных регистра-мультиплексора, выход которого соединен с первым инфор-

мационным входом второго коммутатора, выход которого соединен с входом множимого второго умножителя, о т л и - ч ающе е ся тем, что, с целью повышения быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов, в него введены четыре триггера, второй и третий элементы И, три регистра, первые входы второго и третьего элементов И и синхровходы первого и второго регистров и с первого по третий триггеров соединены с входом синхронизации

устройства, информационный вход первого триггера является входом запуска устройства, виход первого триггера соединен с управляющими входами регистра-мультиплексора и второго коммутатора, входами сброса первого и второго регистров и информационньпч входом второго триггера, выход которого соединен с вторьзм входом второго элемента И, выход которого соединен

инверсный выход разряда заема счетчика соединен с вторым инверсным входом

с синхровходом счетчика, параллель- ный вход данных которого является входом показателя степени устройства, первого элемента И, вторым входом третьего элемента И и входом установ-

с синхровходом счетчика, параллель- ный вход данных которого является входом показателя степени устройства, первого элемента И, вторым входом третьего элемента И и входом установ-

ки четвертого триггера, выход которого соединен с информационным входом третьего триггера, выход которого является выходом сигнала окончания цикла работы устройства и соединен с управляющим входом первого коммутатора, входом сброса четвертого триггера и входом синхронизации третьего регист-

5. 1305670

pa, выход которого является информационным выходом устройства, выход первого сумматора соединен с информаци- ониными входами второго и третьего регистров, выход второго регистра сое- 5 динен с входом множимого первого умножителя, выход второго блока памяти соединен с входом второго слагаемого второго сумматора, выход которого

вого регистра, выход котор нен с .вторыми информацион первого и второго коммута третьего элемента И соеди синхронизации регистра-мул ра, выход которого соедин множителя первого и второ лей, второй информационны гистра-мультиплексора явл

соединён с информационньм входом пер- О дом аргумента устройства.

вого регистра, выход которого соединен с .вторыми информационными входами первого и второго коммутаторов, выход третьего элемента И соединен с входом синхронизации регистра-мультиплексора, выход которого соединен с входами множителя первого и второго умножителей, второй информационный вход регистра-мультиплексора является вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для вычисления коэффициентов интерполирующего полинома | 1990 |

|

SU1748158A1 |

| Устройство для вычисления значений полинома | 1986 |

|

SU1348827A1 |

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для вычисления полинома @ -ой степени | 1983 |

|

SU1140115A1 |

| Устройство для вычисления значений многомерного полинома | 1990 |

|

SU1742829A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1348828A1 |

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных системах, работающих в реальном масштабе времени. С целью повьшения быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов в устройство, содержащее элементы 5, счетчик 8, блоки 9, 10 памяти, сумматоры 11, 12, коммутаторы 13, 14, регистр-мультиплексор 15, умножители. 19, 20, введены регистры 16- 18, триггеры 1-4 и злементы И 6, 7. 4 ил., СО о СП а

35

35 37

ti tz

Фшг

«

35нс .

Редактор Н.Рогулич Заказ 1452/46

Составитель Н.Матвеев

Техред ;л.0лейник Корректор А.Зимокосов

Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35 Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг.

| Устройство для вычисления значений полиномов | 1981 |

|

SU962973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления полинома @ -ой степени | 1983 |

|

SU1140115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-09-23—Подача