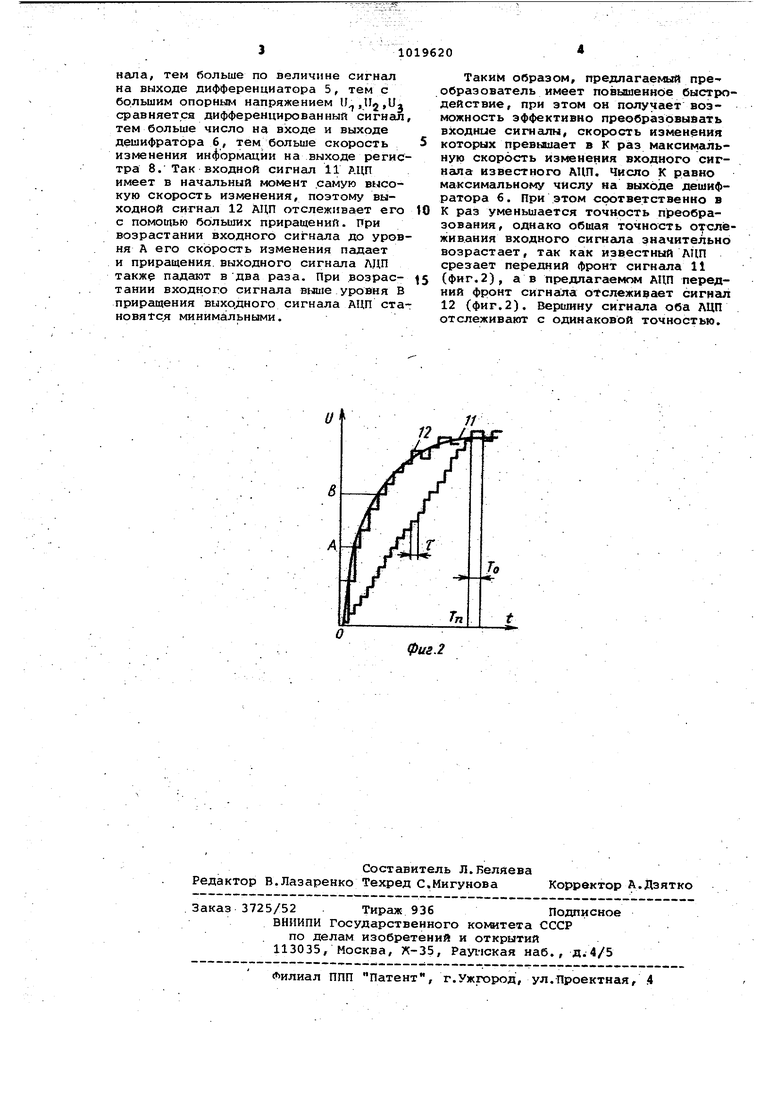

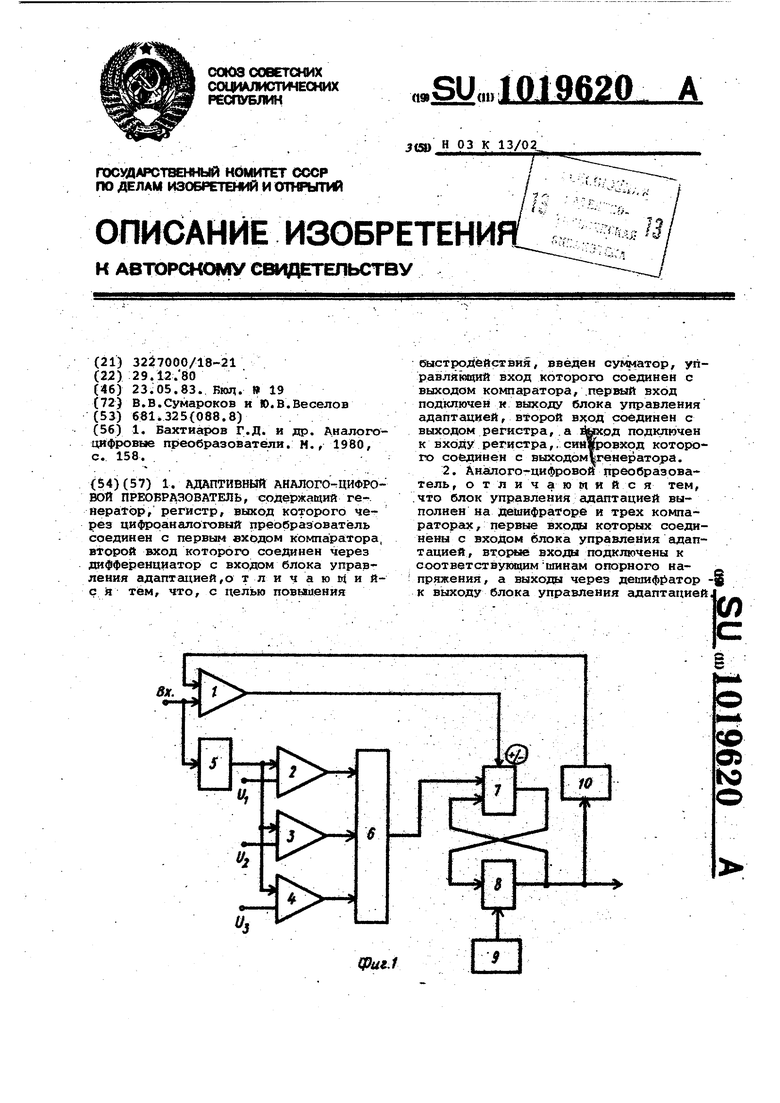

Изобретение относится к измерительной технике и предназначено для осутествления преобразования аналог вого сигнала в цифровой вид. Известен аналого-цифровой преобр зователь () следящего типа. Вход АЦП подключен к входу компаратора, выход которого через блок управления реверсивный счетчик, циброаналоговый преобразователь (ЦЛП) подключен к другому входу компаратора, а на тактовый вход- .реверсивного счетчика под ключен выход тактового генератора. Выходом АЦП является выход логики пе редачи данных, которая входом соединена с другим выходом блока управлеНИН, а другой вход подключен к входу установки начальных условий реверсив ного счетчика 11. Такой преобразователь обладает ма лым временем одного преобразования, но время переходного процесса достаточно велико, что снижает в целом быстродействие всего АЦП. Цель изобретения - повышение быст родействия. Поставленная цель достигается тем что в адаптивный аналого-цифровой пр образователь, содержащий генератор., регисфр, выход которого через цифроаналоговый преобразователь соединен первым входом компаратора, второй вход которого соединен через дифференциатор с входом блока управления адаптацией, введен сумматор, управляющий вход которого соединен с выходом компаратора, первый вход подключен к выходу блока управления адаптацией, второй вход соединен с выходом регистра, а выход подключен к входу регистра, синхровход которого соединен с выходом генератора. Причем, блок управления адаптацией выполнен на дешифраторе и трех компараторах, первые входы которых соединены с входом блока управления адаптацией, вторые входы подключены к соответствующим шинам опорного напряжения, а выходы через дешифраторк выходу блока управления адаптацией На фиг.1 представлена структурная схема адаптивного аналого-цифрового преобразователя/ на фиг.2 - временная диаграмма, поясняющая его работу Устройство содержит компараторы 1-4, дифференциатор 5, дешифратор б, сумматор 7, регистр 8, тактовый генератор 9, цифроаналоговый преобразо ватель (ЦА,П) 10, причем вход устройства связан с/твходом дифференциатора и через компаратор 1 с управляющим входом сумматора 7, выход которого через регистр 8 подключен к входу сумматора 7, к входу всего АЦП и через ЦАП к другому входу компара тора 1, кроме того, выход дифференциатора 5 соединен через компараторы 2,3,4, дешифратор 6 с другим входом сумматора 7, к другим входам компараторов 2,3,4 подключены. соответственно опорные напряжения 11, U2, U, а к синхронизирующему входу регистра 8 подключен выход тактового генератора 9. АЦП работает следую1чим образом. При возрастании входного сигнала 11 (фиг.2) выше сигнала на выходе ПАП 10, на выходе компаратора 1 появляется логическая единица, которая переводит сумматор 7 в режим сложе- . ния входных сигналов. Сумматор 7 совместно с регистром 8 образуют интегратор, вход которого соединен с выходом дешифратора 6. При поступлении с тактового генератора импульсов интегратор производит прибавление входного сигнала к выходному сигналу регистра 8. Данный сигнал начинает возрастать по величине и после преобразования с помощью ЦАП 10 в аналоговый вид этот сигнал сравнивается с входным на входах компаратора 1. Если сигнал с выхода ДАП 10 превысит входной сигнал устройства, то на выходе компаратора 1 появляется логический ноль, который переводит сумматор 7 в режим вычитания, и сигнал на выходе регистра 8 уменьшается. Таким образом, выходной цифровой сигнал АП,П отслеживает свой входной аналоговый сигнал. Причем информация о новом преобразовании появляется на выходе АЦП после каждого тактового сигнала генератора 9. Дифференциатор 5 обеспечивает дифференцирование входного сигнала и на его выходе имеет: место сигнал, пропорциональный скорости изменения входн.ого сигнала. При обычной работе АЦП вkoднoй сигнал имеет -малую скорость изменения. В этом случае на вход сумматора 7 с дешифратора б подается Код, равный единице. При этом на выходе регистра 8 информация при каждом новом такте изменяется на единицу Mnajijiiero разряда, что обеспечивает максимальную точность преобразования (сигнал 12 на .верхнем пологом участке фиг.2). Однако, если входной сигнал имеет большую скорость изменения, когда единичные положитедьные приращения сигнала на выходе регистра 8 не успевают отслеживать входной сигнал АЦП, то срабатывает цепь формирования сумматора 7. При этом сигнал на выходе дифференциатора начинает превышать один из уровней U,U,,U , на выходе компараторов 2, 3,4 появляются логические единицы, что обеспечивает появление на выходе дешифратора 6 числа, болыие единицы. При этом возрастает, величина приращения сигнала на выходе регистра 9, т.е. возрастает скорость отслеживания входнрго аналогового сигнала АЦП. Причем, чем выше скорость из 1енения входного сигнала, тем больше по величине сигнал на выходе дифференциатора 5, тем с большим опорным напряжением l iHjjU сравняется дифференцированный сигнал, тем больше число на входе и выходе дешифратора 6, тем больше скорость изменения информации на выходе регистра 8. Так входной сигнал 11 АЦП имеет в начальный момент самую высокую скорость изменения, поэтому выходной сигнал 12 АЦП отслеживает его с помощью больших приращений. При возрастании входного сигнала до уровня А его скорость изменения падает и приращения выходного сигнала Л1Ш также падают в два раза. При возрастании входного сигнала выше уровня В приращения выходного сигнала АЦП становятся МИНИМ 1ЛЬНЫМИ.

Таким образом, предлагаемый прв образователь имеет повышенное быстродействие, при этом он получает возможность эффективно преобразовывать входные сигналы, скорость изменения которых прев лиает в К раз максимальную скорость изменения входного сигнала известного АЦП. Число К равно максимальному числу на выхОде дешифратора 6. При этом соответственно в К раз уменьшается точность преобразования, однако общая точность отслеживания входного сигнала значительно возрастает, так как известный А1Ш срезает передний фронт сигнала 11 (фиг.2), а в предлагаемом АЦП передний фронт сигнала отслеживает сигнал 12 {фиг.2). Вершину сигнала оба АЦП отслеживают с одинаковой точностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| УСТРОЙСТВО ДЛЯ ДИФФЕРЕНЦИРОВАНИЯ МЕДЛЕННО ИЗМЕНЯЮЩИХСЯ ФУНКЦИЙ | 1991 |

|

RU2050591C1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ СОСТОЯНИЯ ОБЪЕКТОВ УПРАВЛЕНИЯ | 1991 |

|

RU2061253C1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1125643A1 |

| Цифровой адаптивный фильтр | 1990 |

|

SU1837322A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Аналого-цифровой логарифмический преобразователь | 1984 |

|

SU1236511A1 |

1. АДАПТИВНЫЙ АНАЛОГО-тЦИФРОВОЙ ПРЕОВРАЗОВАТЕЛБ, содержащий ге-. Bepatbp, регистр, выход которого через цифрраналоговый преобразователь соединен с первым входом компаратора, второй юсод которого соединен через дифференциатор с входом блока управления адаптацией,о тли ч а ю Ы и йс я тем, что, с пвлъю повьяаения вХ. t и, быстродействия, введен , уйравлй{вщий вход которого соединен с выходом компаратора, .первый вход подключен и выходу блока управления адаптацией, второй вход соединен с выходом регистра,. а ЁВСОД подключен к входу регистра,. синировход которого соединен с выходом1генератора. 2. Аналого-цифровой преобразователь, о т л и ч а ю | и и с я тем, что блок управления адаптацией выполнен на дешифраторе и трех компаpaTojpax, первые входы которых соединены с входом блока управления адаптацией, вторые входы подключены к соответствукмцимшинам опорного на- пряжения, а выходы через дешиф атор -5 к выходу блока управления адаптагшей Ф сь ho фиг.1

//

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бахтиаров Г.Д | |||

| и др | |||

| Аналогоцифровые преобразователи | |||

| М., 1980, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-05-23—Публикация

1980-12-29—Подача