Изобретение относится к автоматике и вычислительной технике, предназначено для получения цифрового значения производной входного аналогового сигнала в следящем режиме и может быть использовано, в частности, при построении цифровых измерительных, управляющих устройств, работающих в реальном масштабе времени.

Цель изобретения - расширение частотного диапазона обрабатываемых сигналов.

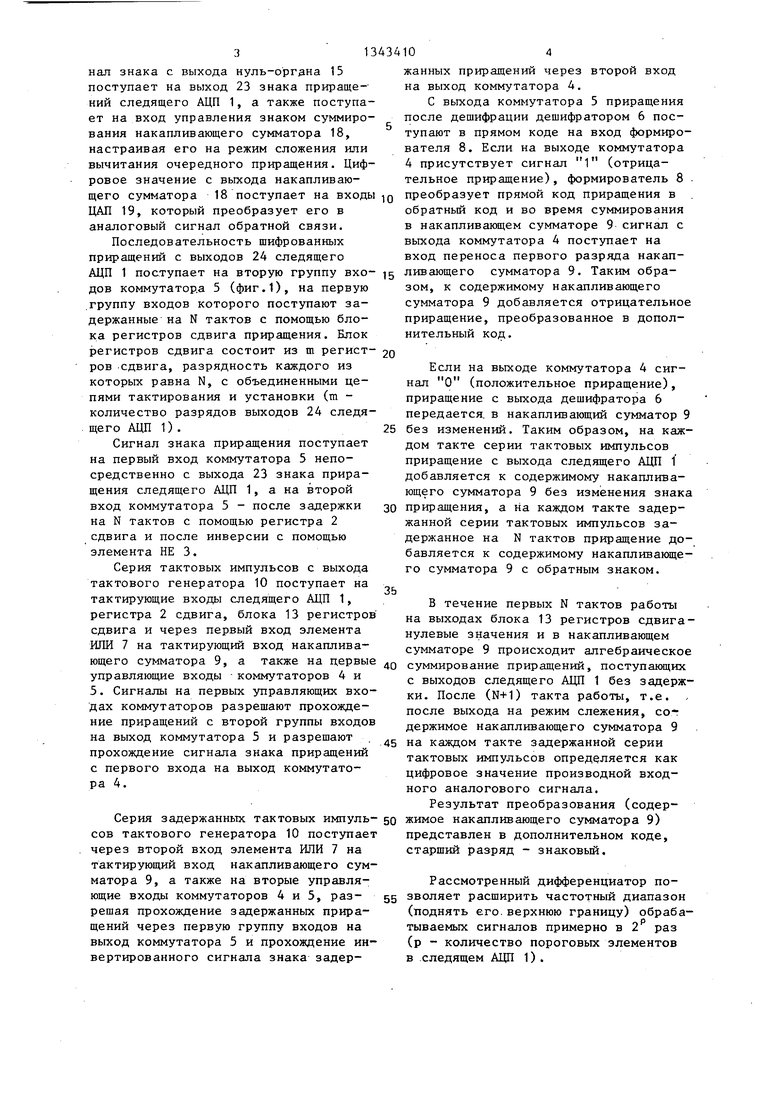

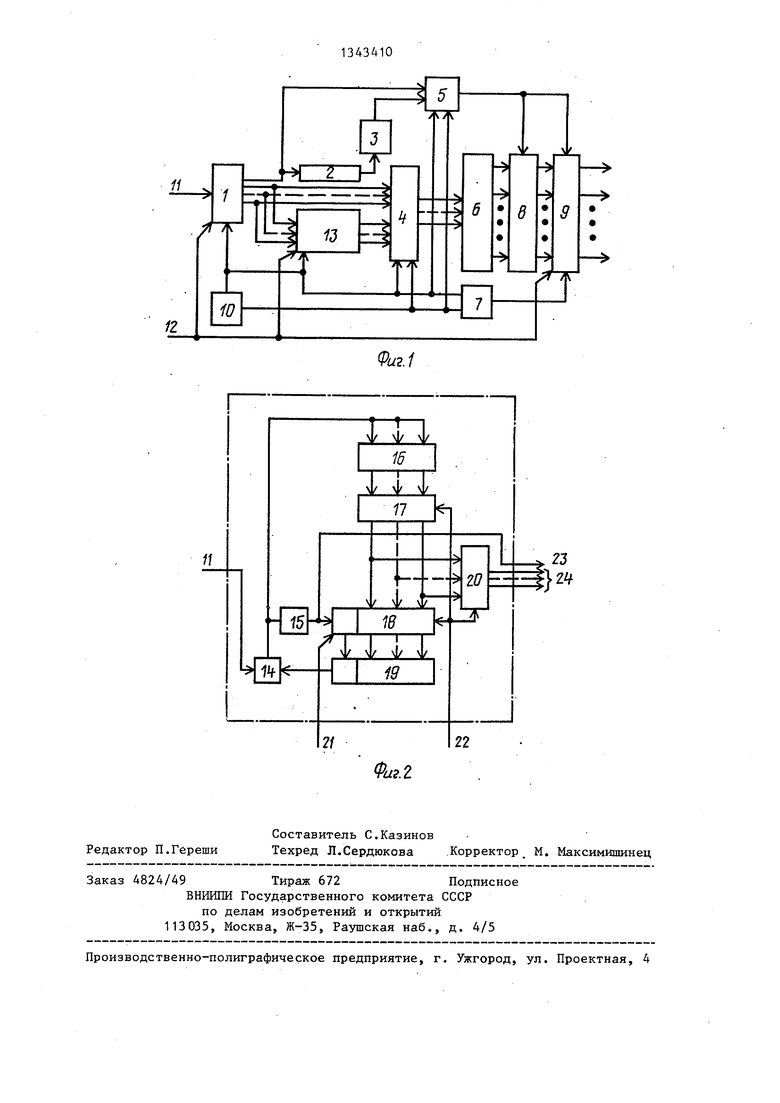

На фиг.1 изображена блок-схема аналого-цифрового инкрементного дифференциатора; на фиг.2 - схема следящего аналого-цифрового преобразователя (АЦП).

Дифференциатор содержит следящий АДП 1, регистр 2 сдвига, элемент НЕ 3, первый коммутатор А (коммутатор знака), второй коммутатор 5 (коммутатор приращений), дешифратор 6, элемент 1ШИ 7,- управЛяемьй формирователь 8 обратного кода, накапливающий сумматор 9, тактовьй генератор 10, аналоговый вход 11, вход 12 начальной установки и блок 13 регистров сдвига.

Сигналом на входе 12 производится 25 установка в О накапливающего сумматора 18 следящего АЦП 1, регистра 2 сдвига, блока 13 регистров сдвига и накапливающего сумматора 9. Входной аналоговый сигнал преобразуется слеАЦП 1 содержит вычитающий узел 14, нуль-орган 15, блок 16 пороговых эле- 30 дящим АЦПJ в последовательность шиф

ментов, приоритетный блок 17, накапливающий сумматор 18, цифроаналоговый преобразователь (ЦАП) 19, шифратор 20, установочный вход 21, тактирующий вход 22, выход 23 знака приращения, выходы 24 разрядов двоичного кода приращения.

В дифференциаторе реализован следящий алгоритм вычисления производной входного сигнала, представляемого приращениями, кодированными . по пока35

рованных (с целью минимизации оборудования) приращений.

Преобразование в следящем АЦП 1 (фиг.2) происходит следующим образом

Вычитающий узел 14 вырабатывает сигнал, равный разности входного ана логового сигнала и сигнала от ЦАП .19 Сигнал разности с выхода узла 14 пос тупает на вход нуль-органа 15, где

40 определяется его знак, а также на входы всех пороговых элементов блока 16, которые настроены на пороги срабатывания, например, по показательному закону: 1, 2, 4, 8, ... 2

зательному закону, что обеспечивает расширение частотного диапазона обрабатываемых сигналов.

Цифровое значение производной в следящем режиме определяется как алгебраическая сумма приращений входного сигнала за определенный интервал времени NT

пт.

и. Z . ,

(n-N)T

где t/. - приращение на i-м такте работы устройства;

п N, N+1, N+2, ...;

N const - разрядность регистров в группе регистров сдвига-,

Т - период тактовых импульсов.

Для момента времени (п записать

п

+ 1) Т можно

и

п-и

.

n+1-N

и,

Ч

п-и

х

n-N - V

. + .

-

n-N

5

Таким образом получена рекуррентная процедура. Результат представлен в дополнительном коде, поэтому О п (Ч п,) , если sign(t/) О - по- -ложительное приращениеj t/n+i ) (V,,,) + 2 если sign(v,, ) 1 - отрицательное приращение, .f/ (.tt ) , если sign(t/.) 1; .-.) (,/.., ) - 2- если sif,n(t/.n,) 0, где (...)P, (...) , (...) - приращения соответственно в прямом, обратном .и дополнительном кодах ;, г - разрядность накапливающего сумматора.

Дифференциатор работает следующим образом.

Сигналом на входе 12 производится 5 установка в О накапливающего сумматора 18 следящего АЦП 1, регистра 2 сдвига, блока 13 регистров сдвига и накапливающего сумматора 9. Входной аналоговый сигнал преобразуется сле0

0 дящим АЦПJ в последовательность шиф

ящим АЦПJ в последовательность шиф

.r-i

ованных (с целью минимизации оборуования) приращений.

Преобразование в следящем АЦП 1 (фиг.2) происходит следующим образом.

Вычитающий узел 14 вырабатывает сигнал, равный разности входного анаогового сигнала и сигнала от ЦАП .19. Сигнал разности с выхода узла 14 поступает на вход нуль-органа 15, где

определяется его знак, а также на входы всех пороговых элементов блока 16, которые настроены на пороги срабатывания, например, по показательному закону: 1, 2, 4, 8, ... 2

условных единиц, где г - разрядность ЦП 1.

Приоритетный блок 17 определяет старший сработавший разряд и передает на свой выход удвоенное значение.

Таким,образом, на выходе приоритетного блока 17 - приращение в .позиционном коде: один разряд 1, остальные О. Прирал ение с выхода приоритетного блока 17 поступает на входы

накапливающего сумматора 18 и на шифратор 20, который шифрует номер единичного разряда приращения по двоичному закону. Эта величина передается на выходы 24 следящего АЦП 1. Сигнал знака с выхода нуль-органа 15 поступает на выход 23 знака приращений следящего АЦП 1, а также поступает на вход управления знаком суммирования накапливающего сумматора 18, настраивая его на режим сложения или вычитания очередного приращения. Цифровое значение с выхода накапливающего сумматора 18 поступает на входы Q преобразует прямой код приращения в

ЦАП 19, который преобразует его в

аналоговый сигнал обратной связи.

Последовательность шифрованных

приращений с выходов 24 следящего

АЦП 1 поступает на вторую группу вхо- 5 ливающего сумматора 9. Таким обрадов коммутатора 5 (фиг.1), на первую группу входов которого поступают задержанные на N тактов с помощью блока регистров сдвига приращения. Блок регистров сдвига состоит из m регист- 2о ров сдвига, разрядность каждого из которых равна N, с объединенными цепями тактирования и установки (т - количество разрядов выходов 24 следящего АЦП 1).

Сигнал знака приращения поступает на первый вход коммутатора 5 непосредственно с выхода 23 знака приращения следящего АЦП 1, а на второй вход коммутатора 5 - после задержки на N тактов с помощью регистра 2 сдвига и после инверсии с помощью элемента НЕ 3.

Серия тактовых импульсов с выхода тактового генератора 10 поступает на тактирующие входы следящего АЦП 1, регистра 2 сдвига, блока 13 регистров сдвига и через первый вход элемента ИПИ 7 на тактирующий вход накапливающего сумматора 9, а также на дервые управляющие входы коммутаторов 4 и 5. Сигналы на первых управляющих входах коммутаторов разрешают прохождение приращений с второй группы входов на выход коммутатора 5 и разрешают прохождение сигнала знака приращений с первого входа на выход коммутатора 4.

зом, к содержимому накапливающего сумматора 9 добавляется отрицательно приращение, преобразованное в дополнительный код.

Если на выходе коммутатора 4 сигнал О (положительное приращение), приращение с выхода дешифратора 6 передается, в накапливающий сумматор

25 без изменений. Таким образом, на каж дом такте серии тактовых импульсов приращение с выхода следящего АЦП 1 добавляется к содержимому накапливающего сумматора 9 без изменения знак

30 приращения, а на каждом такте задержанной серии тактовых импульсов задержанное на N тактов приращение до бавляется к содержимому накапливающе го сумматора 9 с обратным знаком.

ЗЬ

40

В течение первых N тактов работы на выходах блока 13 регистров сдвига нулевые значения и в накапливающем сумматоре 9 происходит алгебраическо суммирование приращений, поступающих с выходов следящего АЦП 1 без задерж ки. После (N+1) такта работы, т.е. после выхода на режим слежения, содержимое накапливающего сумматора 9 45 на каждом такте задержанной серии тактовых импульсов определяется как цифровое значение производной входного аналогового сигнала.

Результат преобразования (содерСерия задержанньж тактовых импуль- 50 жимое накапливающего сумматора 9) сов тактового генератора 10 поступает через второй вход элемента ИЛИ 7 на тактирующий вход накапливающего сумматора 9, а также на вторые управляющие входы коммутаторов 4 и 5, разрешая прохождение задержанньпс прирапредставлен в дополнительном коде, старщий разряд - знаковый.

55

Рассмотренный дифференциатор позволяет расширить частотный диапазо (поднять его. верхнюю границу) обраб тываемых сигналов примерно в 2 раз (р - количество пороговых элементов в .следящем АЦП 1) .

щении через первую группу входов на выход коммутатора 5 и прохождение инвертированного сигнала знака задер34104

жанных приращений через второй вход на выход коммутатора 4,

С выхода коммутатора 5 приращения после дешифрации дешифратором 6 поступают в прямом коде на вход формирователя 8. Если на выходе коммутатора 4 присутствует сигнал 1 (отрицательное приращение), формирователь 8

обратный код и во время суммирования в накапливающем сумматоре 9 сигнал с выхода коммутатора 4 поступает на вход переноса первого разряда накапзом, к содержимому накапливающего сумматора 9 добавляется отрицательное приращение, преобразованное в дополнительный код.

Если на выходе коммутатора 4 сигнал О (положительное приращение), приращение с выхода дешифратора 6 передается, в накапливающий сумматор 9

без изменений. Таким образом, на каждом такте серии тактовых импульсов приращение с выхода следящего АЦП 1 добавляется к содержимому накапливающего сумматора 9 без изменения знака

приращения, а на каждом такте задержанной серии тактовых импульсов задержанное на N тактов приращение добавляется к содержимому накапливающего сумматора 9 с обратным знаком.

В течение первых N тактов работы на выходах блока 13 регистров сдвига- нулевые значения и в накапливающем сумматоре 9 происходит алгебраическое суммирование приращений, поступающих с выходов следящего АЦП 1 без задержки. После (N+1) такта работы, т.е. после выхода на режим слежения, содержимое накапливающего сумматора 9 на каждом такте задержанной серии тактовых импульсов определяется как цифровое значение производной входного аналогового сигнала.

жимое накапливающего сумматора 9)

представлен в дополнительном коде, старщий разряд - знаковый.

жимое накапливающего сумматора 9)

Рассмотренный дифференциатор позволяет расширить частотный диапазон (поднять его. верхнюю границу) обрабатываемых сигналов примерно в 2 раз (р - количество пороговых элементов в .следящем АЦП 1) .

Формула изобретения

1. Аналого-цифровой инкрементный дифференциатор, содержащий следящий аналого-цифровой преобразователь, подключенный информационным входом к аналоговому входу дифференциатора, установочным входом - к входу начальной установки дифференциатора и уста- Q установки дифференциатора, а тактиновочному входу регистра сдвига, тактирукяцим входом - к первому выходу тактового генератора и тактирующему входу регистра сдвига, а выходо знака приращения - к информационному входу регистра сдвига и первому информационному входу первого коммутатора, соединенного вторым информационным входом через элемент НЕ с выходом регистра сдвига, а управлякнцимн входами - с первым и вторым выходами тактового генератора, о т л и ч а ю- щ и и с я тем, что, с целью расширения частотного диапазона обрабатываемых сигналов, в него дополнительно введены второй коммутатор, дешифратор, элемент ИЛИ, управляемый формирователь обратного кода, накапливающий сумматор и блок регистров сдвига подключенных информационными входами к выходам соответствующих разрядов двоичного кода приращения следящего аналого-цифрового преобразователя, установочными входами - к входу начальной установки дифференциатора, тактирующими входами - к первому выходу тактового генератора, а выходами - к, первой группе информационных входов второго коммутатора, соединенного второй группой информационных входов с выходами разрядов двоичного кода приращения следящего аналого- цифрового преобразователя, управляющими входами - с первым и вторым выходами тактового генератора, а выходами - с входами дешифратора, выходы которого подключены к информационным

входам управляемого формирователя обратного кода, соединенного управляющим входом с выходом первого коммутатора и входом переноса первого разряда накапливающего сумматора, а выходами - с информационными входами накапливающего сумматора, подключенного установочным входом к входу начальной

рующим входом - к выходу элемента ИЛИ, соединенного входами с первым и вторым выходами тактового генератора.

2. Дифференциатор по п.1, о т л и- чающийся тем, что следящий аналого-цифровой преобразователь содержит блок пороговых элементов, подключенный входами к выходу вычитающего узла, а выходами - к информационным входам приоритетного блока, соединенного тактирующим входом с тактирующим входом следящего аналого-цифрового преобразователя и тактирующими входами накапливающего сумматора и шифратора, а выходами - с информационными входами накапливающего сумматора и входами шифратора, выходы которого являются выходами разрядов двоичного кода приращения следящего аналого-цифрового преобразователя, причем выходы накапливающего сумматора подключены к входам цифроаналого- вого преобразователя, соединенного выходом с первым входом вычитающего узла, второй вход которого является информационным входом следящего аналого-цифрового преобразователя, а выход подключен к входу нуль-органа, соединенного выходом с выходом знака приращения следящего аналого-цифрового преобразователя и с входом управления знаком суммирования накапливающего сумматора, установочный вход которого является установочным входом следящего аналого-цифрового преобразователя.

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Дифференцирующее устройство | 1984 |

|

SU1264170A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

Изобретение относится к области автоматики и вычислительной техники. Аналого-цифровой инкрементный диффе- 4зенциатор содержит следящий аналого- цифровой преобразователь, регистр сдвига, элемент НЕ, первый и второй коммутаторы, дешифратор, управляемый формирователь образного кода, элемент ИЛИ, накапливающий сумматор и тактовый генератор. Расширение частотного диапазона,обрабатываемых сигналов достигается на основе использования следящего алгоритма вычисления производной входного сигнала, представляемого приращениями, кодированными по показательному закону. В про- , цессе работы дифференциатора в накапливающим сумматоре код производной формируется --как алгебраическая сумма приращений входного сигнала за определенный интервал времени, вычисляемая на основе соответствующей рекуррентной процедуры. 1 з.п. ф-лы, 2 ил. (С (Л оо 4 ОО .

Редактор П.Гереши

Составитель С.Казинов

Техред Л.Сердюкова .Корректор М. Максимишинец

Заказ 4824/49 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР то заявке № 3769358/24, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР по заявке № 3773077/24; кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР по заявке № 3741036/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-07—Публикация

1985-02-22—Подача