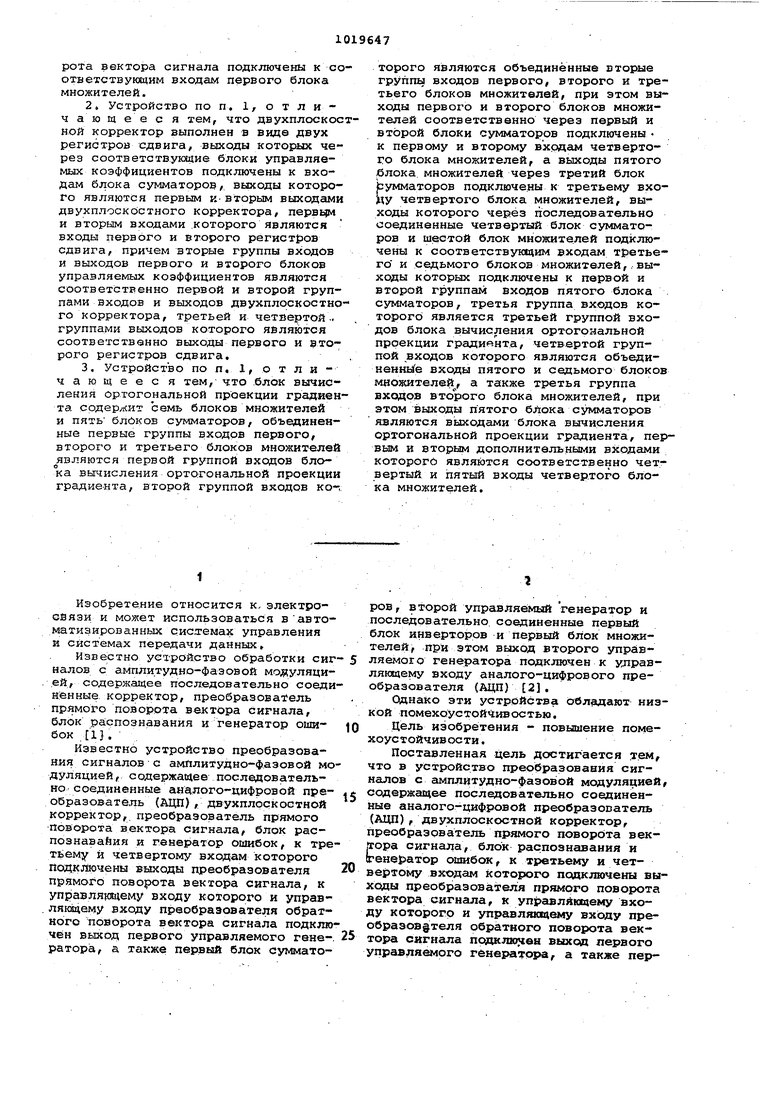

рота вектора сигнала подключены к соответствующим входам первого блока множителей.

2,Устройство по п. 1/ отличающееся тем, что двухплоскосной корректор выполнен в виде двух регистров сдвига, выходы которых через соответствуняцие блоки управляемых коэффициентов подключены к входам блока сумматоров, выходы которого являются первым к- вторым выходгши двукплоскбстного корректора, первцм

и вторым входами .которого являются входы первого и второго регистров сдвига, причем вторые группы входов и выходов первого и второго блоков управляемых коэффициентов являются соответственно первой и второй группами входов и выходов двухплоскостного корректора, третьей и четвертой группами выходов которого яйляются соответственно выходы первого и рторого регистров сдвига.

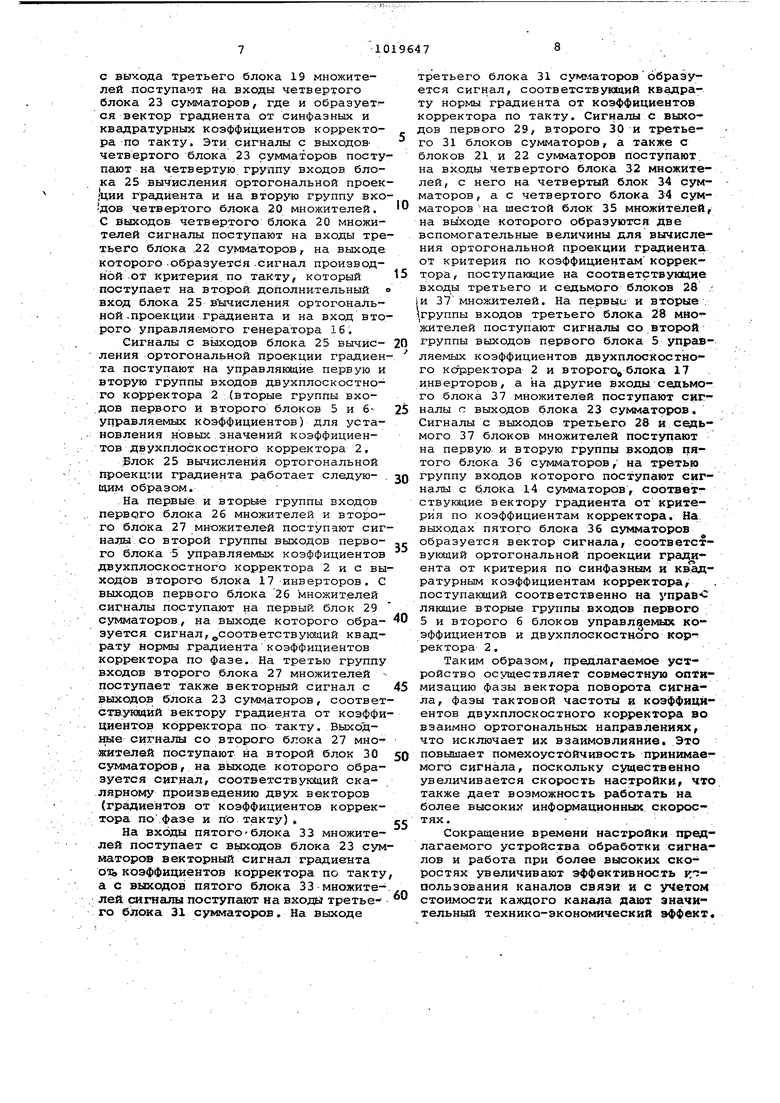

3,Устройство по п. 1, отличающееся тем, что .блок вычисления ортогональной проекции градиента содержит семь блоков множителей

и ПЯТЬ бликов сумматоров/ объединенные первые группы входов первого, второго и третьего блоков множителей являются первой группой входов бло°ка вЕлчисления ортогональной проекции градиента, второй группой вкодов ко-,:

торого я вляются объединённые вторые группы входов первого, второго и третьего блоков множителей, при этом выходы первого и второго блоков множителей соответственно через первый и второй блоки сумматоров подключены к первому и второму входам четвертого блока множителей, а выходы пятого блока множителей через третий блок Ьумматоров подключе.ны к третьему входу четвертого блока множителей, выходы которого через последовательно соединенные четверотый блок сумматоров и ше1стой блок множителей подключены к соответствук«цим входам третьего и седьмого блоков множителей,. выходы которых подключены к первой и второй группам входов пятого блока сумматоров, третья группа входов которого является третьей группой входов блока вычисления ортогональной проекции градиента, четвертой группой входов которого являются объедиHeHHfcefe входы пятого и седьмого блоков множителей, а также третья группа входов второго блока множителей, при этом выходы пятого блока сумматоров являются выходами блока вычисления ортогональной проекции градиента, первым и вторым дополнительными входами которого являются соответственно четвертый и пятый входы четвертого блока множителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема сигналов с амплитудно-фазовой модуляцией | 1986 |

|

SU1385316A1 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| Устройство для регулирования асинхронного двигателя | 1983 |

|

SU1202006A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| Устройство для быстродействующей токовой защиты электроустановки переменного тока | 1983 |

|

SU1111220A1 |

| Частотно-регулируемый электропривод | 1988 |

|

SU1605307A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ МАНИПУЛЯТОРОМ С ШЕСТЬЮ СТЕПЕНЯМИ ПОДВИЖНОСТИ И ЛИНЕЙНО ПЕРЕМЕЩАЕМЫМ В ГОРИЗОНТАЛЬНОЙ ПЛОСКОСТИ ОСНОВАНИЕМ | 2022 |

|

RU2794082C1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| ТРЕХФАЗНЫЙ КОМПЕНСАТОР РЕАКТИВНОЙ МОЩНОСТИ | 2017 |

|

RU2677628C1 |

| УСТРОЙСТВО ДЛЯ ВЫСТАВКИ ИНЕРЦИАЛЬНЫХ ДАТЧИКОВ | 1986 |

|

RU1426192C |

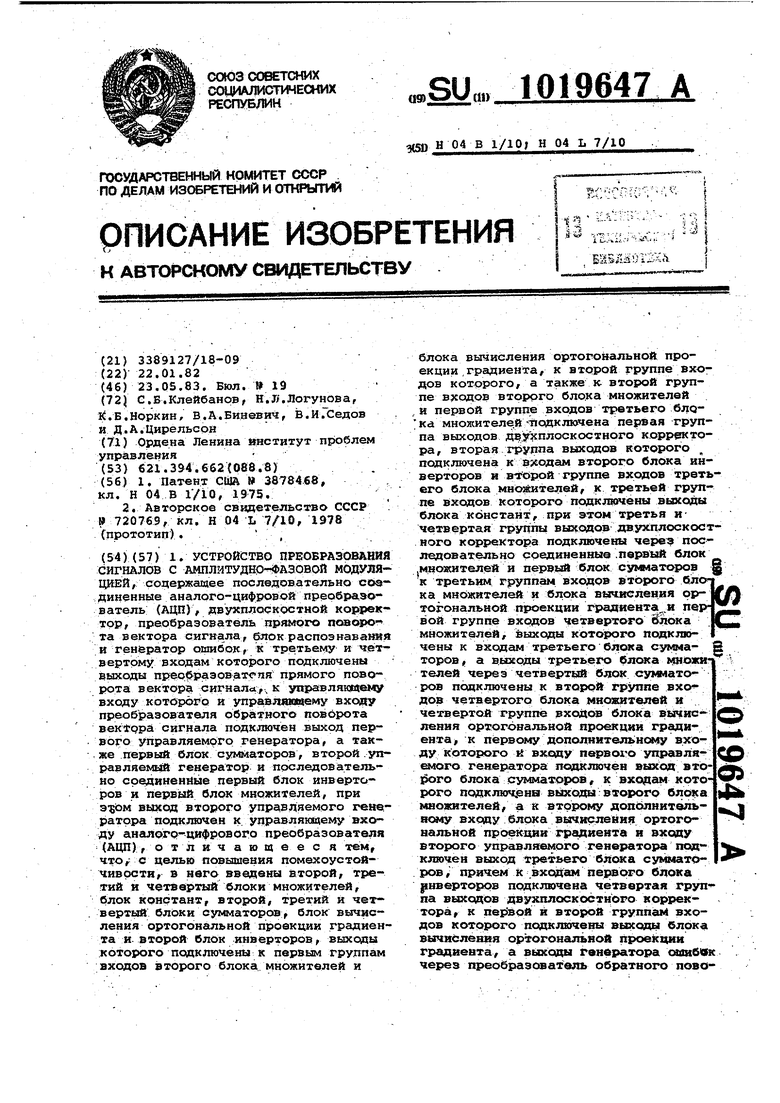

1. УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ С АМПЛИТУДНРНЬАЗОВОЙ МОДУЛЯЦИЕЙ , соцержащее гюследовательно обадиненные аналого-цифровой прер6ра,эователь (АЦП), двухплоскостной корректор, преобразователь прямого поворота вектора сигнала, блок распознавания и генератор ошибок, к третьему и четвертому входам которого подключены выходы .аэов, прямого поворота вектора сигналау, к управляющему входу которого и управлюощему BxoiRy преобразователя обратного поворота вектрра сигнала подключен выход перBoiro управляемргр генератора, а также аервый блок сумматоров, второй.управляемый генерато) и последовательно срединеннкае первый блок инверторов и первый блок множителей, при эфэм выход второго управляемого гене:ратрра подключен к управлякщему входу аналого-цифрового преобразователя АЦП) , о тличающееся тем, что,: с целью повышения помехоустойчиврсти, в него введены Второй, третий я четвертый блоки множителей, блок крнртант, второй, третий и четвертый блоки сумматоров блок вычисления ортогональной проекции градиента и второй блок инверторов, выходы которого подключены к первым группам входов второго блока множителей и

Изобретение относится к, электроовязи и может использоваться вавто.матиаироваиных системах управления и Системах передачи данных.

Известно устройство обработки сигналов с амплитудно-фазовой модуляци.ей, содержащее последовательно соединенные корректор, преобразователь прямого поворота вектора сигнала, блок распознавания и генератор ошибок }. .

Известно устройство преобразования сигналов с амплитудно-фазовой модуляцией, содержащее последовательно Соединенные аналого-цифровой преобразователь (АЦП, двухплрскостной корректор, преобразователь прямого поворота вектора сигнала, блок распознавайия и генератор ошибок, к третьему и четвертому входам которого Подключены выходы преобразователя прямого поворота вектора сигнала, к управлякадему входу которого и управлякщему входу преобразователя обратного поворота вектора сигнала подключён выход первого управляемого гене-. ратора, а также первый блок сумматоров, второй управляемый генератор и последовательно, соединенные первый блок инверторов и первый блок множителей, при этом выход второго управляемого генератора подключен к управляющему входу аналого-цифрового преобразователя (АЦП) 2.

Однако эти устройства обладают низкой помехоус тоййив ос тью.

Цель изобретения - повышение помехоустойчивости.

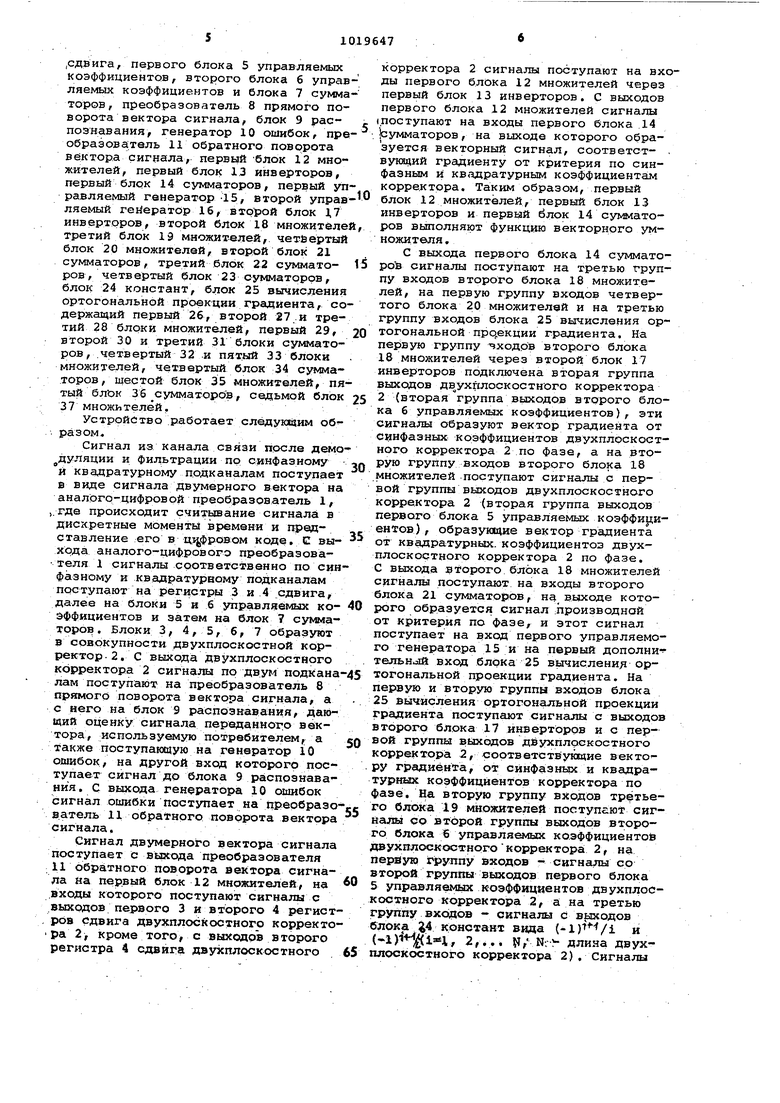

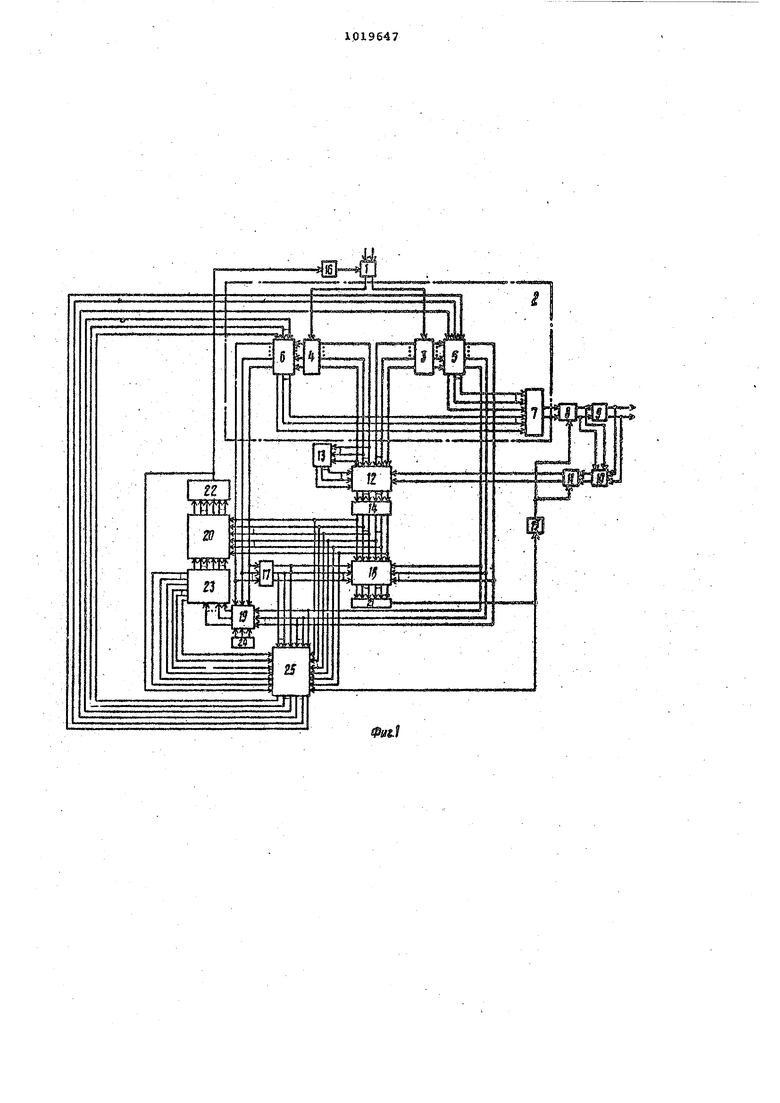

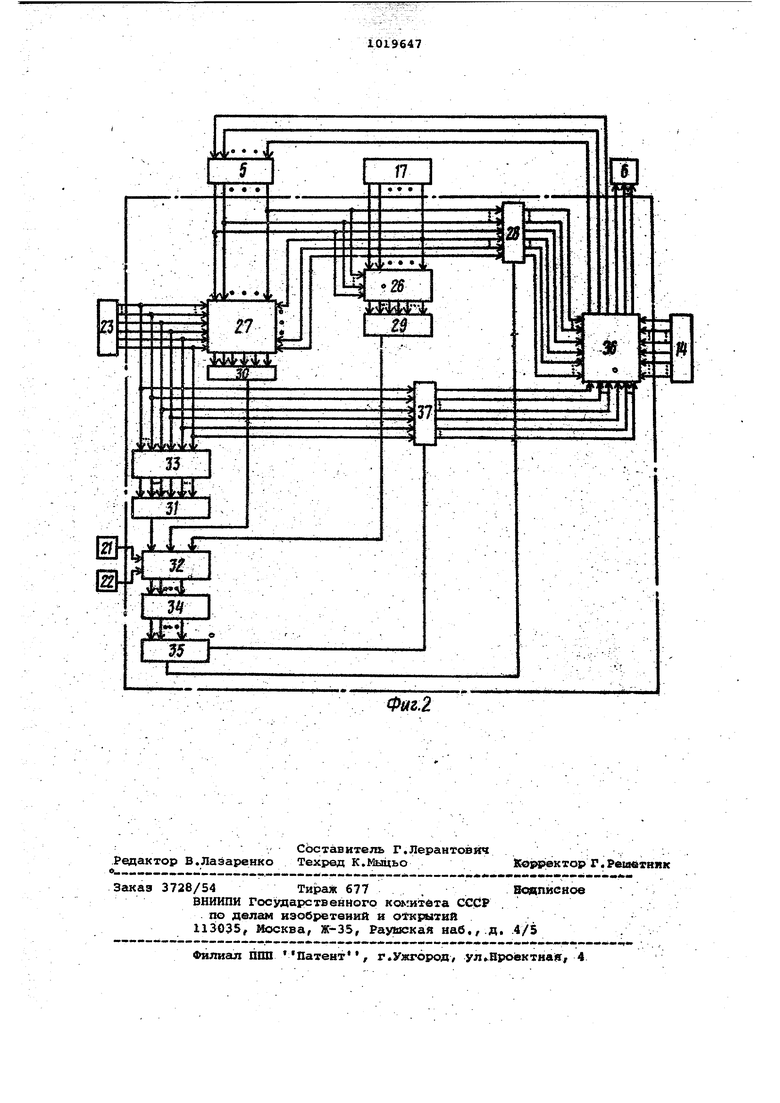

Поставленная цель достигается тем, что в устройство преобразования сигналов с амплитудно-фазовой модуляцией содержащее последовательно соединенные аналого-цифровой преобразователь (АЦП), двухплоскостной корректор, преобразователь прямого поворота векjropa сигнала, блок распознавания и (генератор ошибсж, к третьему и четвертому входам которого псщключены выходы преобразователя прямого поворота вектора сигнала, к управлякщему входу которого и управЛЯК1ЦШ4У входу преобраэоа§теля обратного поворота вектора сигнала подключен выхсл лервого управляемого генератора а также первый блок сумматоров, второй управляемый генератор и последовательно соединенные первый блок инверторов и первый блок множителей, при этом выход управляемого генератора подключен к управлякэдему входу аналого-цифрового преобразователя (АЦП), введены второй, третий н четвертый блоки мнйжителей, блок констант, второй/ третий и четвертьй блоки .сумматоров, блок рычисления ортогональной проекции градиента и второй блок инверторов, выходы которого подключены к первым группам входов второго блока множителей и блока вычисления ортогональной проекции градиента, к второй .группе входов которого, а также к второй группе входов второго блока множителей и первой группе входов третьего блока множителей подключена первая группа выз4одов двухплоскостно го корректора, вторая группа выходов которого подключена ко входам второго блока инверторов и второй группе входов третьего блока множителей, к третьей группе входов которого подключены выходы блока констант, при этом третья и четвертая группы выходов двухплоскостного корректора подключены через последовательно соединенные первый блок, множителей и первый блок сумматоров к третьим группам входов второго блока множителей и блока вычисления ортогональной про .екции градиента и первой группе входов четвертого блока множителей, выходы которого подключены к входам третьего блока сумматоров, а выхода третьего блока множителей через четвертый блок сумматоров подключены к второй группе вхбдов четвертого блока множителей и четвертой группе йхо дов блока вычисления ортогональной проекции градиента, к первому дополнительному входу которого и входу пе вого управляемого генератора подключен выхЬд; второго блока сумматоров, к входам которого подключены выходы второго блока множителей,а к второму дополнительному входу блока в|ачисления ортогональной, проекции градиента и входу второго управляемого генерат ра подключен выход третьего блока су матора, причем к ахоаам первого блока инверторов подклкэчена четвертая груп па выходов двухплоскостного корректо ра, к первЪЙ и второй группам входов которого подключены выходы блока выт числения ортогональной проекции град ента, а выхсАЫ генератора ошибок чере преобразователь обратного поворота вектора сигнала подключены к соответ Ьтвукадим входам первого блока множи(гелей. Кроме того, двухплосксстной корре тор выполнен в виде двух регистров сдвига, выходы которых через соответствующие блоки управляемых коэфФи иентов подключены к входам ЬлоКа умматоров, выходы которого являются ервым и вторым выходами двухплоскостного корректора, первьаи и вто1ялм вхоами которого являются входы первого и второго регистров сдвига, причем торые группы входов и выходов первого и второго- блоков управляемых коэффициентов являются соответственно первой и второй группами входов и выхоов двухплоскостного корректора, третьей и четвертой группами выходов которого являются соответственно выходы первого и второго регистров сдвига. при этом блок вычисления ортогональной проекции градиента содержит семь блоков множителей и пить блоков сумматоров, объединенные первые группы входов первого, второго и третьего блоков множителей являются первой группой входов блока вычисления ортогональной проекции градиента/ второй группой входов- которого являются объединенные вторые группы входов первого, второго и третьего блоков множителей, при этом выходы первого и второго, блоков множителей соответственно через первый и второй блоки сумматоров подключены к первому и втором / входам четвертого блока множителей, : а выходы пятого блока множителей через третий блок сумматоров подключены к -третьему входу четвертого блока множителей, выходы которого через последовательно соединенные четвертый блок сумматоров и шестой блок множителей подключены к соответствующим входам третьего и седьмого блоков множителей, выходы которых подключены к первой и второй группам входов пятого блока сумматоров., третья группа входов которого являете я,-4 третьей группой входов блока вычисления ортогональной проекции градиента четвертой группой входов которого являются объединенные входы пятого и седьмого блоков множителей, а также третья группа входов второго блока множителей, при ятом выходы пятого блока суг«4аторов являются выходами блока вычисления ортогональной проекции градиента , первы&1 и вторым дополнительными входами которого являются соответственно четвертый и пятый входы четвертого блока множителей. На фиг 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - реалиэа 1ия .блока вычисления ортогональной проекции градиента. Устройство преобразования сигналов с амплитудно-фазовой модуляцией содержит аналого-цифровой преобразователь (АЦП) 1, двухплоскостной корректор 2, СОСТОЯЩИЙ из первого регистра 3 сдвига, второго регистра 4

,сдвига, первого блока 5 управляемых коэффициентов, второго блока б управляемых коэффициентов и блока 7 сумматоров, преобразователь 8 прямого поворота вектора сигнала, блок 9 рас- познавания, генератор 10 ошибок, преобразователь 11 обратного поворота Вектора сигнала, первьзй блок 12 множителей, первый блок 1.3 инверторов, первый блок 14 сумматоров, первый управляемый генератор 15, второй управ- ляемый гейератор 16, второй блок 17 инверторов, второй блок 18 множителей, третий блок 19 множителей,, четбертый блок 20 множителей, второй блок 21 сумматоров, третий блок 22 суммато- 15 ров, четвертый блок 23 сумматоров, блок 24 констант, блок 25 вычисления ортогональной проекции градиента, содержащий первый 26, второй 27 и третий 28 блоки множителей, первый 29, 20 второй 30 и третий ЗГ блоки сумматоров, .четвертый 32 .и пятый 33 блоки множителей, четвертый блок 34 сумматоров, шестой блок 35 множителей, пятый блок 36 сумматорф, седьмой блок 25 37 множителей.

Устройство работает следуюгвим об разом.

Сигнал из канала связи после демодуляции и фильтрации по синфазному л и квадратурному подканалам поступает в виде сигнала двумерного вектора на аналого-цифровой преобразователь 1, где происходит считывание сигнала в дискретные моменты времени и представление его в Ц14|фров;ом коде, С вы- хода аналого-цифрового преобразователя 1 сигналы соответственно по синфазному и квадратурному подканалам поступают на регистры 3 и .4 сдвига, далее на блоки 5 и б управляенслх ко- 40 Зффициентов и затем на блок 7 cyivMaторов. Блоки 3, 4, 5, 6, 7 образуют S совокупности двухплоскостной корректор -2. с выхода двухплоскостного корректора 2 сигналы по двум подкана-45 лам поступают на преобразователь 8 прямого поворота вектора си.гнала, а с него на блок 9 распознавания, дающий оценку сигнала переда,нмого вектора, используемую потребителем, а Q также поступающую на генератор 10 ошибок, на другой вход которого поступает сигнал до блока 9 распознавания, С выхода генератора 10 ошибок сигнал ошибки поступает на преобразо-се вательИ обратного поворота вектора сигнала.

Сигнал двумерного вектора сигнала поступает с выхода преобразователя 11 обратного поворота вектора сигнала йа первый блок 12 множителей, на 0 входы которого поступают сигналы с выходов первого 3 и второго 4 регистров сдвига двухплоскостного корректора 2, кроме того, с выходов второго регистра 4 сдвига двухплоскостного 65

корректора 2 сигналы поступают на входы первого блока 12 множителей через первый блок 13 инверторов. С выходов первого блока 12 множителей сигналы .поступают на входы первого блока 14 сумматоров, на выходе которого образуется векторный сигнал, соответст- , вунидий градиенту от критерия по синфазным и квадратурным коэффициентам корректора Таким образом, первый блок 12 множителей, первый блок 13 инверторов и первый ёлок 14 су а аторов выполняют функцию векторного умножителя .

С выхода первого блока 14 сумматоров сигналы поступают на третью группу входов второго блока 18 множителей, на первую группу входов четвертого блока 20 множителей и на третью группу входов блока 25 вычисления ортогональной протекции градиента. На первую группу -чходрв второго блока 18 множителей через второй блок 17 инверторов подключена вторая группа выходов дв ухплоскостного корректора 2 (вторая группа выходов второго блока б управляемых коэффициентов), эти сигналы образуют вектор градиента от синфазных коэффициентов двухплоскостного корректора 2 по фазе, а на вторую группу входов второго блока 18 множителей поступают сигналы с первой группы выходов двухплоскостного корректора 2 (втррая группа выходов первого блока 5 управляемых коэфФи|1;иенфов), образующие вектор градиента от квадратурных, коэффициентоз двух- плоскостного корректора 2 по фазе, С выхода второго блока 18 множителей сигналы поступают на входы второго блока 21 сумматоров, на, выходе которого образуется сигнал :производнай от критерия по фазе, и этот сигнал поступает на щхоя первого управляемого генератора 15 и на Первый дополнительн.лй вход блока 25 вычисления ортогональной проекции градиента. На первую и вторую группы входов блока 25 Вычисления ортогональной проекции градиента поступают сигналы с выходов второго бл.ока 17 инверторов и с первой группы выходов дйухплоскостного корректора 2, соответствующие вектору градиента, от сйнфазньк и квадратуршгх коэффициентов корректора по азе. На вторую группу входов трфтьего блока 19 множителей поступают сигНалы со второй группы выходов второго блока 6 управляемых коэффициентов вухплоскостного корректора; 2, на первую группу входов - сигнсипы со второй группы выходов первого блока 5 управляемых коэффициентов двухплоскостного корректора 2/ а на третью группу входов - сигналы с выходов блока J4 констант вида (-l) и (-1)1 , 2,,,. Яг длина двухплоскостного корректора 2).Сигналы

с выхода третьего блока 19 множителей поступают на входы четвертого блока 23 сумматоров, где и обраэуетгся вектор градиента от синфазных и квадратурных коэффициентов корректора по такту. Эти сигналы с выходовчетвертого блока 23 сумматоров поступают на четвертую группу входов блока 25 вычислений ортогональной проек;ции градиента и на вторую группу входов четвертого блока 20 множителей. С Ввакодов четвертого блока 20 множителей сигналы поступают на входы третьего блока .22 сумматоров, на выходе которого.образуется.сигнал производной от критерия по такту, который поступает на второ-й дополнительный о вход блока 25 вЪгаисления ортогональной -проекции градиента и на вход второго управляем&го генератора 16.

Сигналы с выходов блока 25 вычйсления ортогональной проекции градиента поступают на управляквдйе первую и вторую группы входов двухплоскостного корректора 2 (вторые группы вхо.дов первого и второго блоков 5 и буправляемых коэффициентов) для установления новых.значений коэффициентов двухплоскостного корректора 2,

Блок 25 вычисления ортогональной проекции градиента работает следую- . щим образом.

На первые и вторые группы входов первого блока 26 множителей и второго блока 27 множителей поступают сигналы со второй группы выходов первого блока 5 управляемых коэффициентов двухплоскостного корректора 2 и с выходов второго блока 17 инверторов. С выходов первого блока 26 множит.елей сигналы поступают на первый блок 29 сумматоров, на выходе которого образуется сигнал,соответствукмий квадрату нормы градиента коэффициентов кор ректора по фазе. На третью группу входов второго блока 27 множителей поступает также векторный сигнал с выходов блока 23 сумматоров, соответств уюийй вектору градие.нта от коэффициентов корректора по такту. Выходные сигналы со второго блока 27 мно жителей поступают йа второй блок 30 сумматоров, на выходе которого образуется сигнал, соответствукхций ска.яярному произведению двух векторов (градиентов от коэффициентов корректора по фазе и по такту) ,

На входы пятогоблока 33 множителей поступает с выходов блока 23 сумматоров векторный сигнсш градиента йэь коэффициентов корректора по такту а с выхсщов пятого блока 33 множителей сигналы поступают на входи третье го блока 31 сумматоров. На выходе

третьего блока 31 сумматоровобразуется сигнал, соответствующий квадрату нормы градиента от коэффициентов корректора по такту. Сигналы с выходов первого 29, второго 30 и третьего 31 блоков сумматоров, а также с блоков 21 и 22 сумматоров поступают. на входы четвертого блока 32 множителей, с него на четвертый блок 34 сумматоров, а с четвертого блока 34 сумматоров на шестой блок 35 множителей, на выходе которого образуются две вспомогательные величины для вычисления ортогональной проекции градиента от критерия по коэффициентам корректора, поступакщие на соответствукадие входы третьего и седьмого блоков 28 1И 37 множителей. На первые; и вторые , группы входов третьего блока 28 мно жителей поступают сигналы со второй группы выходов первого блока 5 управляемых коэффициентов двухплоскостного корректора 2 и второго,блока 17 инверторов, а на другие входы седьмого блока 37 множителей поступают сигналы п выходов блока 23 сукматоров. Сигналы с выходов третьего 28 и мого 37 блоков множителей поступают на первую и вторую, группы вводов пятого блока 36 сумматоров, на третью группу входов которого поступают сигналы с блока 14 сумматоров, соответствуквдие вектору градиента от критерия по коэффициентам корректора. На выходах пятого блока 36 сумматоров образуется вектор сигнала, соответствующий ортогональной проекции градиента от критерия по синфазным и квадратурным коэффициентам корректора, поступакхций соответственно на ynpafiляквдие вторые группы входов первого 5 и второго 6 блоков управляемых коэффициентов и двухплоскостного корректора 2.

Таким образом, прёдлага.емое устройство осуществляет совместную оптимизацию фазы вектора поворота сигнала, фазы тактовой частоты и коэффициентов двухплоскостного корректора во взаимно ортогональных направлениях, что исключает их взаимовлияние. Это повышает помехоустойчивость принимаемого сигнала, поскольку существенно увеличивается скорость настройки, чт также дает возможность работать на более высоких информационных скоростях.

Сокра111ение времени настройки предлагаемого устройства обработки сигналов и работа при более высоких скоростях увеличивают эффективность к аользования каналов связи и с у 1етом стоимости каждого канала дают значительный технико-экономический эффект

Фы1.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ПОЛУЧЕНИЯ МЕТАЛЛИЧЕСКОГО БАРИЯ | 1934 |

|

SU38784A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство обработки сигналов с амплитудно-фазовой модуляцией | 1978 |

|

SU720769A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-05-23—Публикация

1982-01-22—Подача