вого сьмматора по модулю два через второй регистр задержки подключен к второму входу четвертого сузупяатора по моду.пю два, выход второго сумматора по модулю ва через второй аналйзатор инверсной последовательности подключен к первому входу второго элемента ИЛИ, к второму входу которого подключен выход, второго анализатора синхропосылки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приемо-передачи двоичной информации | 1990 |

|

SU1757115A1 |

| Устройство для устранения обратной работы в системах передачи дискретных сообщений с фазовой манипуляцией | 1990 |

|

SU1755722A3 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для формирования циклического синхроимпульса | 1989 |

|

SU1725404A1 |

Изобретение относится к передаче дискретных сообщений и может быть использовано в системах передачи двоичной информации непрерывными кодами по каналам связи.

Известно устройство для одновременной тактовой и групповой синхронизации рабочими посылками в каналах с относительной фазовой.и частотнофазовой манипуляцией и информационными кодами tl .

В этом устройстве производится вращение фазы на границах элементарных посылок и на границах кодовых групп на угол f , вдвое меньше угла информационной модуляции, а на приеме производится оценка угла вращения и, следовательно, выделение границ кодовых групп.

Недостатком этого устройства явяется снижение помехоустойчивости .выделения синхросигнала при увеличении длины кодового слова в нестационарных каналах.

Известно устройство приемо-передачи двоичной информации, содержащее на передающей стороне датчик посылок синхронизации и формирующий регистр, выходы соответствующих разрядов которого через первый сумматор по модулю два подключены к первому входу второго сумматора по мо-г дулю два, выход которого, а также выход формирующего регистра подключен ко входам KOMMjf татора, а на приемной стороне - опорный датчик синхропосылки и коммутатор, выходы которого подключены ко входам регистра проверочных символов и регистра информационных символов, выходы соответствующих разрядов которого подключены к первому и второму входам первого сумматора по модулю два, ход которого подключен ко входу, первого анализатора сийхропосылки, а к третьему входу первого сумматора по модулю подключен выход регистра проверочных символов, выходы соответствующих разрядов которого подключены к первому И второму входам второго сумматора по модулю два, к третьему входу которого через дополнительный регистр подключен выход регистра информационных символов , а выход второго сумматора по модулю два подключен ко входу второго

анализатора синхропоснлки, при этом выхода соответствующих разрядов регистра обнаружения ошибок подключены ко входам элемента И, выход

5 которого подключен к первому входу третьего сумматора по модулю два, а ко входу регистра обнаружения ошибок подключен выход четвертого сумматора по модулю два Е23.

Q Однако известное устройство не обеспечивает совместную передачу сигналов ЦИКЛОВОЙ синхронизации и служебной информации по общему каI налу.

Цель изобретения - обеспечение

передачи сигналов цикловой синхронизации и служебной информации по общему каналу.

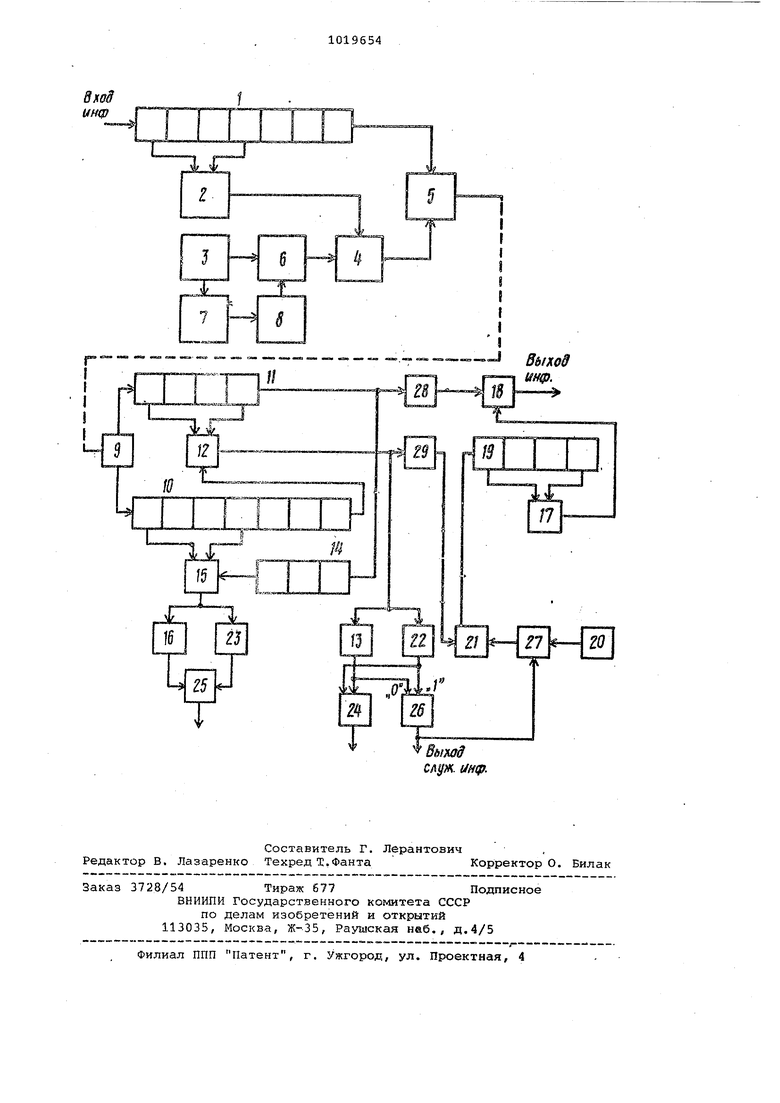

. Поставленная цель достигается тем, что в устройство приемо-переда0 чй двоичной информации, содержащее на передающей стороне датчик синхропосылки и формирующий регистр, выходы соответствукадих разрядов которого через первый сумматор по модулю 5 два подключены к первому входу втр: рого сумматора по модулю два, выf ход которого, а также выход формирукидего регистра подключен к входам коммутатора, а на приемной стороне 0 опорный датчик синхропосылки и комму татор, выходы которого подключены к входам регистра проверочных символов и регистра информационных символов , выходы соответствуняаих разс рядов которого подключены к первому и второму входам первого сумматора по модулю Два, выход которого подключен к входу первого анализатора синхропосылки, а к третьему входу первого сумматора по модулю два подключен вйход регистра проверочных символов, выходы соответствующих разрядов которого подключены к пер-, вому и второму входам второго сумматора по модулю два, к третьему 5 (ВХОДУ которого через дополнительный регистр подключен выход регистра информационных символов, а выход вторюТо сумматора по модулю два подклюЧен к входу второго анализатора синл -хропосылк и, при этом выходы соответ.ствукяцих разрядов регистра обнаружьЫия ошибок подключены к входам элемента И., выход которого подключен .к первому входу третьего сумматора по модулю два, а к входу регистра об наружения ошибок подключен выход четвертого сумматора по модулю два, введены на передающей стороне последовательно соединенные блок фиксации начала синхропосылки, датчик слу жебной информации и третий сумматор по модулю два, выход которого подклю чен к второму входу второго сумматора по модулю два, при этом выходы датчика синхропосылки подключены соответственно к второму входу третьего сумматора по модулю два и вхо ду блока фиксации начала синхропо-. сыпки, а на приемной стороне введены два регистра задержки, два элемента ИЛИ, два анализатора инверсной последовательности, пятый сумматор по модулю два и триггер формирования импульсов служебной ин формации, к единичному входу которого, а также к первому входу первого элемента ИЛИ через первый анализатор инверсной последовательности подключен выход первого сумма тора по модулю два, а к нулевому входу триггера формирования импульсов служебной информации и второму входу первого элемента ИЛИ подключен выход первого анализатора син.хропосылки, а выхол триггера формирования импульсов, служебной информа ции подключен к первому входу пятог сумматора по модулю два, к второму входу которого подключен выход опор ного датчика синхропосылки, а выход пятого сумматора по модулю два подключен к первому входу четвертого сумматора по модулю два, при этом выход регистра- информационных симво лов через первый регистр задержки .подключен к второму входу третьего сумматора по модулю два, а выход пер вого сумматора по модулю два через второй регистр задержки подключен к второму входу четвёртого сумматора по модулю два, выход второго сумматора по модутю два через второй ана лизатор инверсной последовательности подключен к первому входу второг элемента ИЛИ, к второму входу котор го подключен выход второго анализатора синхропосылки. На чертеже приведена структурная электрическая схема устройства. Устройство приемо-передачи двоичной информации содержит на передающей сторона формирующий регистр 1, первый сумматор 2 по модулю два, датчик 3 синхропосылки, второй сумматор 4 по модулю два, коммутатор 5. третий сумматор 6 по модулю два, блок 7 фиксации начала синхропосылки, датчик 8 служебной информации, на приемной стороне - коммутатор 9, регистр 10 пооверочных символов, регистр 11 информационных символов .первый сумматор 12 по модулю два, -первый анализатор 13 синхропосылки, ополнительный регистр 14, второй умматор 15 по модулю два, второй анализатор 16 синхропосылки, элеент И 17, третий сумматор 18 по модулю два, регистр 19 обнаружения ошибок, опорный датчик 20 синхропосылки, четвертый сумматор 21 по модулю два, первый 22 и второй 23 анаг лизаторы инверсной последовательности, первый 24 и второй 25 элементы ИЛИ, триггер 26 формирования импуль сов служебной информации, пятый сумматор 27 по модулю два, первый 28 и второй 2-9 регистры задержки. Устройство работает следующим образом. На вход формирующего регистра 1 подается последовательность информационных символов, которая после соответствующей задержки в этом ре-гистре подается на первый вход коммутатора 5, Одновременно формируется последовательность проверочных символов путем суммирования по модулю два информационных символов, поступающих на входы первого сумматора 2 по модулю два с выходив соответствующих разрядов формирующего регистра 1. Датчик 3 синхропосылки периодически генерирует синхронизирующую последовательность,.которая поступает на второй вход третьего сумматора б по модулю два.. Начало генерации сиЕ1хронизирующей последовательности фиксируется блоком 7 фиксации начала синхропосылки, формируюЩим в момент начала синхропосылки импульс запроса служебной информации, который подается на: датчик 8 служебной информации. По команде, . поступающей с блока 7 фиксации начала синхропосылки, датчик 8 служебной информации выдает очередной симт вол служебной информации на первый вход третьего сумматора б по модулю два. При этом, в зависимости от поступающего на первый вход третьего сумматора 6 символа служебной информации (О или 1), на выходе третьего сумматора б по модулю два формируется либо прямая, либо инверсная синхропосылка. Так при подаче на первый вход третьего сумматора 6 по модулю два символа О на выход третьего сумматора 6 по модулю два проходит прямая синхропосыяка, а при подаче 1 - инверсная. С выхода третьего сумматора б по модулю два прямая или инвеосная синхропосылка поступает на второй вход второго сумматора 4 по модулю два, на первый вход которого подается последовательность проверочных символов с выхода первого сумматора 2 по модулю два. Суммарная последовательность с выхода первого сумматора 2 по модулю два подается на второй вход коммутатора 5, который поочередно выдает на выход символы

информационной и cyNtf/iapHOft последовательностей. Последовательность символов с выхода коммутатора 5 передается по каналу связи и поступает далее на вход коммутатора 9, работающего синхронно с коммутатором 5.

Синфазная работа обоих коммутаторов, т.е. цикловая синхронизация, а также прием символов служебной информации осуществляется следующим образом.

В случае правильной фазы комму-, тации клммутатор 9 направляет последовательность информационных символов в регистр 11 информационных символов, а суммарную последовательность - в регистр 10 проверочных символов. С выхода регистра 10 проверочных символов суммарная последовательность поступает на третий вход первого сумматора 10 по модулю два, на первый и второй входы которого подаются информационные символы с выходов соответствующих разрядов ре гистра 11 информационных символов. При этом на.выходе первого сумматора 12 по модулю два выделяется пряма или инверсная (в зависимости от передаваемого в данный момент символа служебной информации синхронизирующаяся последовательность, которая подается далее на входы первых анализаторов 13, 22 прямой и инверсной синхропосылок, анализирующих поступающую последовательность на принадлежность ее прямой или инверсной синхропосылке. передается пряма синхропосылка, то на выходе первого анализатора 13 синхропосылки формируется импульс опознания этой синхропосылке. Аналогично, при передаче инверсной синхропосылки импульс опознания формируется на выходе первого анализатора 22 инверсной синхропосылки . Так как выходы первых анализаторов 13 и 22 прямой и инверсной синхропосылок объединены первым элементом ИЛИ 24, то при правильной фазе коммутации KOMT-iyTaTopa 9 на выходе первого элемента ИЛИ 24 формируется синхронизирующий импульс, подтверждающий правильность фазы коммутации коммутатора 9.

Одновременно с формированием синхронизирующих импульсов происходит выделение символов служебной информации на выходе триггера 26 формирования импульсов служебной информации путем установки выхода триггера 26 формирования импульсов служебной информации в состояние О при подаче импульса опознания прямой синхропосылки с выхода первого анализатора 13 синхропосылка на нулевой вход триггера 26 формирования импульсов служебной информации и, соответственно, в состояние 1 при подаче импульса опознания инйерсной синхропосылки с выхода первого анализатора 22 инверсной последовательности на единичный вход триггера 26 формирования импульсов служебной информации.

Последовательность символов, поступающих на входы вторых анализаторов 167 23 прямой и инверсной синхропосылок при правильной фазе коммутации коммутатора 9, является случайной и, следовательно, не приводит к формированию импульсов опознания на выходе второго элемента ИЛИ -25, объединяющей выходы вторых анализаторов 13, 23 прямой и инверсной последовательности. В. случае неправильной фазы коммутации коммутатора 9 информационная последовательность направляется коммутатором 9 в регистр 10 проверочных символов, а суммарная последовательность - в регистр 11 информационных символов. Прямая или инверсная синхропосылка при этом выделяется на выходе второго суматора 15, сумматора по модулю два, а на выходе первого сумматора 12 выделяется некоторая случайная последовательность символов. Тогда импульс опознания синхропосылки формируется на выходе или второго анализатора 13 синхропосылки или второго анализатора 23 инверсной ( синхропосылки}, выходы которых объединены вторым элементом ИЛИ 25. Импульс цикловой синхронизации формируется в этом случае на выходе второго элемента ИЛИ 25, что свидетельству ет об обратной фазе коммутации коммутатора 9 и, следовательно, о необходимости изменения этой фазы на противоположную с целью обеспече- , ния цикловой синхронизации передатчика и приемника и осуществления приема символов служебной информации.

После установления цикловой синх ронизации декодирование цепного кода ос-уществляется следующим путем. Опорный датчик 20 синхропосылки фазируется синхронизирующими импульсами, выдаваемыми первым элементом ИЛИ 24, и периодически генерирует синхропоследовательность, которая с выхода датчика 20 синхропосылки поступает на второй вход пятого сумматора 27 по модулю два, на первый вход которого подаются символы служебной информации с выхода триггера 26 формирования импульсов служебной информации. При этом пятый сумматор 27 по модулю два осуществляет манипуляцию фазы синхропосылок на 180° в моменты смены символов служебной информации, что позволяет синхронизировать смену знаков синхропосылок на передающей и приемной сторонах с задержкой, определяемой защитньгм промежутком цепного KOffti и длительностью синхропосылки. Для правильного декодирования элементов цепного кода информационная последовательность, поступающая с вьжода регистра 11 информационных символов, и прямая или инверсная син хропоследовательность,, поступающая с выхода сумматора 15 по модулю два (искаженные, в общем случае, помехами) , также задерживаются на длительность синхропосылки посредством регистров 28, 29 задержки соответственно и подаются: информационная последовательность - на второй вход третьего сумматора 18 по модулю два а синхропоследовательность с соот- ветствующим знаком - на второй вход четвертого сумматора 21 по модулю два, на первый вход которого подается синхропоследовательность с выхода пятого сумматора 27 по модулю два со знаком, совпадающим со знаком синхропоследовательности, по тупающей на второй вход этого сумма тора. На выходе четвертого сумматор 21-по модулю два выделяется исправляющая последовательность, состоящая из одних нулей при отсутствии ошибок в передаваемой информации. Если же имеются ошибки, то испрзвляющая последовательность содержит единицы в определенном расположении, позволяющем исправить ошибки. С выхода четвертого сумматора 21 по мсэдулю два исправляющая чоследовате льность поступает; на вход регистра 19 обнаружения ошибок. При появлени единиц в разрядах регистра 19 обнаружения ошибок, соединенных со входами элемента И 17, появляется единица на выходе этого элемента и, следовательно, на первом входе третьего сумйатора 18 по модулю два соединенном с выходом элемента И 17 В этом случае информационный символ поступающий на второй вход третьего сумматора 18 пс модулю два, заменяется на выходе сумматора в результа те суммирования по модулю два с единицей, присутствугацей на его втором входе, на противоположный, ем и достигается испр авление ошибки. Таким образом, предлагаемое устройство позволяет передавать сигналы ЦИКловЬй синхронизации и дополнительную служебную информацию по общему каналу без расширения занимаемой полосы частот и снижения скорости передачи основной информации. Незначительная задержка в выдаче основной информации по сравнению с известным устройством, равная длительности синхропосылки, в брльшинстве практических случаев не играет существенной роли, особенно при передаче больших объег|юв информации поско.льку величина этой задержки становится пренебрежимо малой относительно общего времени передачи информации. Следовательно, указанная цель изобретения достигается практическ1й без снижения проп: скной способности канала связи. Отметим также, что помехоустойчивосаь передачи служебной информации превосходит помехоустойчивость передачи основной информации, так как решение о знаке синхропосылки, а следовательно о передаваемом символе служебной информации, производится в результате анализ всей совокупности элементов синхропоследовательности в целом, часть из которых может быть принята ошибочно и не исправлена в дальнейшем в декодере при появлении серийной ошибки дли-л ной, большей чем защитный промежуток используемого цепного кода. Кроме того, к достоинствам предлагаемого устройства относится то, что использование его. в ргши жаналах не требует никаких изменений в радиочастотных трактах ни передающего, ни приемного устройств.

ску. инф.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ОДНОВРЕМЕННОЙ ТАКТОВОЙ И ГРУППОВОЙ СИНХРОНИЗАЦИИ РАБОЧИМИ ПОСБ1ЛКАМИ В КАНАЛАХ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ И ЧАСТОТНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ И ИНФОРМАЦИОННБШИ КОДАМИ | 0 |

|

SU305594A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ПАТЕНТНО ТЕХНЯНГ К** | 0 |

|

SU344597A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| пос;.едогвательности подключен выход первого сумматора по модулю два, а со к нулевому входу триггера формироваа ния импульсов служебной информации и второму входу первого элемента ИЛИ ел подключен выход первого анализатора 4 синхропосылки, а выход триггера формирования импульсов служебной информации подключен к первому входу пятого сумматора по модулю два, к второму входу которого подключен выход опорного датчика синхропосылки, а выход пятого сумматора по модулю два подключен к первому входу четвертого сумматора по модулю два, при этом выход регистра информационных символов через первый регистр задержки подключен к второму входу третьего сумматора по :oдyлю два, а выход пер | |||

Авторы

Даты

1983-05-23—Публикация

1982-02-01—Подача