Изобретение относится к технике многоканальной связи и может использоваться для приема сигналов контроля о состоянии радиорелейных станций, работающих на пригщипе временного разделения каналор с модуляцией параметров импульсов аналоговым сигналом.

Известно устройство для приема сигналов контрсия, содержащее поеледова тель.но соединенные первый элемент И, вход которого является входом устройства, расширитель импульсов и регистр сдвига, прямой вь1Ход Первого разряда которого соединен с входом распределителя приема, выходы которого подключены через дешифратор к приемнику, а инвертированный выход второго разряда и прямые выходы остальных разрядов соединены с входами второго элемента И, делитель импульсов, тактовый вход которого срединен с тактовым входом регистра сдвига и с вторым входом первого элемента И til Однако известное устройство имеет низкую помехозащищенность приема. Цель изобретения - повьпиение помехезащищенности приема. Для достижения поставленной цели в устройство дла приема сигналов контроля, содержащее последовательно соединенные первый элемент И, вход которого является входом устройства, расширитель импульсов и регистр сдвига, прямой выход первого разряда которого соединен с входом распределителя приема, выходы которого подключены через дешифратор к приемнику, а инвертированный выход БТОрЬго разряда и прямые выходы остальных ; разрядов соединены с входами второго элемента И, усилитель импульсов, тактовый вход которого соединен с тактовым входом регистра сдвига и с вторым входомпервого элемента И, введены блок поразрядного сравнения, два D -триггера, элемент задержки, дифференциккщая цепочка, инвертор, третий, четвертый, пятый, шестой и седьмой элементы И,при атом первый и второй входы блока поразрядного сравнения соединены соответственно с прямым выходом первого разряда сдвига и с выходом последнего разряда распределителя npieMa, л выход блока поразрядного сравнения соединен с первым входом шестого элемента И, выход которого через инвертор подключен к первому входу второго D -триггера, йричем выход Второго элемента И соединен с первыми входами третьего и четвертого ( элементов И, выход и второй вход которого соединены соответственно с вторььмй входами первого и второго D -триггеров и с объединенными входом элемента задержки и выходом делителя импульсов, второй вход которого через дифференциру5 юшую цепочку соединен с выходом третьего элемента И, второй вход которого соединен с первым выходом второго D триггера, второй выход и тактовый вход которого соединены соответственно с первым входом седьмого элемента И и с тактовым входом nepBoix D -триггера и выходом элемента задержки, а второй вход и первый и второй выходы перво-го D -триггера соединены соответственно

15 с выходом последнего разряда регистра сдвига, с вторыми входами пятого и шестого элементов И и с вторым входом седмого элемента И, выход которого соединен е управляющим входом дешифратора.

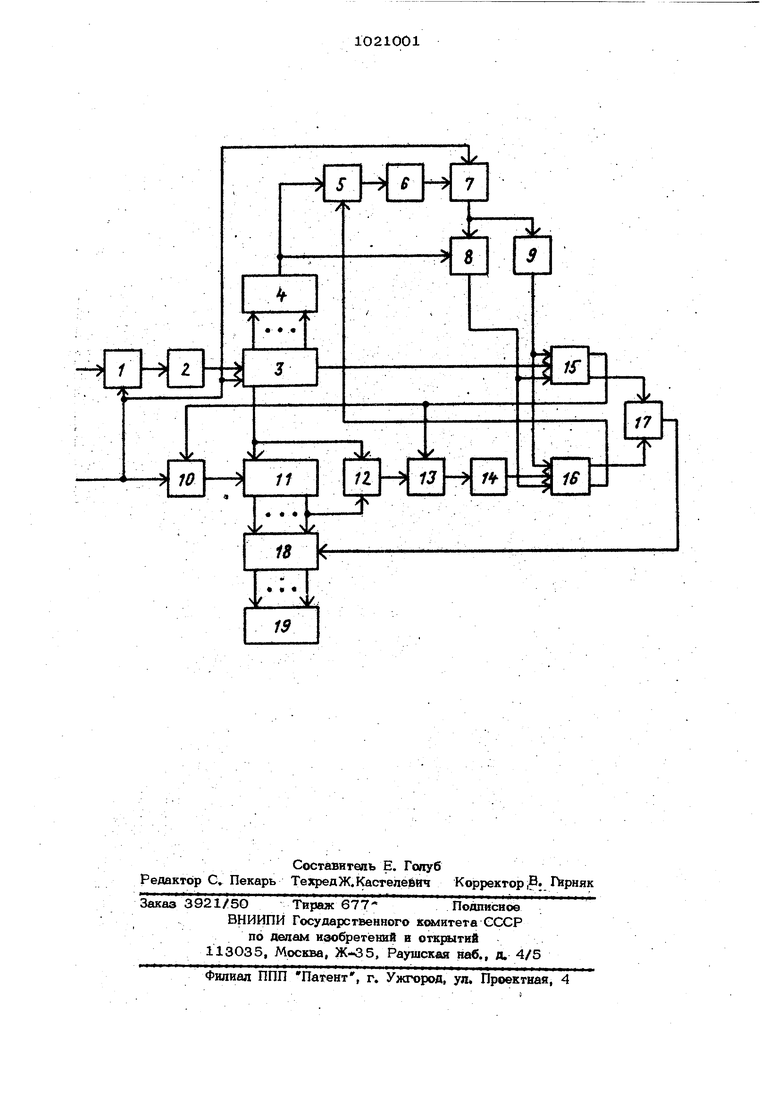

ставе импульсов служебного канала сигналов контрйпя, которые следуют через П тактов и состоят из стартовой посылки (отсутствие импульса) и г тактов , инфсфмационных, 0 которых передается отсутствием импульса служебного канала, а 1 - наличием импульса служебного канала. 20 выход пятого элемента И соединен с тактовым входом распределителя приема, а первый вход соединен с вторым входом первого элемента И и является другим входом устройства. 25 На чертеже представлена структурная схема предлагаемого устройства. Устройство для приема сигналов контроля содержит первый элемент И 1, расширитель 2 импульсов, регистр 3 сдвига. зо второй и третий, элементы И 4 и 5 соответственно, дифференцирующую Цепоч1су 6, делитель ,7 имцульсов, четвертый элемент И 8, элемент 9 задержки, пятый элемент И 10, распределитель 11 приема, блок 12 поразрядного сравнения, шестой элемент И 13, инвертор 14, первый и второй J5 -триггеры 15 и 16 соответственно, седьмой элемент И 17, дешифратор 18 и приемник 19. Устройство работает следуклдим образом. Работа устройства приема сигналов контроля рассматривается на примере ио-, . Яолъзования его в радиорелейной 24-ка{кшьной станций с фазоимпульсной модуляцией в двух случаях: при отсутствии сигналов контроля в составе импульсов служебного кйнаяа, т, е. когда импульсы служебного канала следуют непрерывно (исходное состояние), и при наличии в соПоложительные импульсы всех каналов подаются На первый первого элемё та И 1, на второй вход которого подаются импульсы подставки служебного канала Первый элемент И .1 обеспечивает выде,пение из последовательности всех импуль сов, только импульсов служебного канала дли тельное ИзЮ 0,5-О,6 мкс, которые поступают на взсбд расширителя 2, обеспечивающего увеличение длитвдьности импульсов до 6-7 МКС дня того, ЧТО&1 он своим задним фронтбМ перекривал импуль подставки. Выход расигаритеяя 2 подключен к входу регистра 3 сдвига, состоя.щего из г-+2 разрядов, на второй вход которого подаются тактовые импульсы, При отсутствии сигналов контропя в составе импульсов служебного канапа по всем разрядам {эегистра 3 сдвига будет постоянно подвигаться 1. Так как к входам второго элет 1ента И 4 подключен инвертированный выход второго разряда регистра 3 сдвига и прямые выхох1ы остальных г разрядов, то на первом входе второго элемента И 4 будет постоянно логический О, а на остальных входах 1. Вследствие этого на его выходе будет постоянно логический У1Ю вень О, Ввиду того,iчто Jaыxoд BTopwe элемента И 4 пошслючён к первым входам третьего элемента И 5 и четвертого элемента И 8, то и на их выходах не зависимо от уровня сигнала на остальных входах будет постоянно логический уровень О который с выхода четвертого элемента И 8 подается на J5-входы обои и-триггеров. 15 и 16. Так как на выходе третьего элемента И 5 будёт постоян но логический уровень О, т.е. будут отсутствовать перепады напряжения, то дифферешщруюшая цепочка 6 не будет формировать импульсов, которые должны подаваться на вход установки в О дели Теля 7 импульсов, и делитель 7 импульсов будет производить деление импульсов подставки на п поступакяшсх на его второй вход, с произвольной фазой. Импулыял подставки в рассматриваемой радиорелейной станции следуют с частотой 8 кГц, поэтому на выходе де .лителя 7 импульсов будут появляться им тсуяьсы с частотой 8/п кГц, которые через элемент 9 задержки устанавливают D-триггеры 15 и 16 в состояние О , так как на их В-входах присутствовал логический уровень О. Логический уровень О с прямого выхода первого D триггера 15 подается на первый вход пя 10 14 ого элемента И 10 и не пропускает на го выход .тактовые импульсы подставки, следствие чего запись информации в расределитель 11 приема, поступающей с ыхода первого разряда регистра 3 двига, производиться не будет. Этот же огический уровень О с прдалого выхо да первого D -триггера 15, поступая на первый вход шестого элемента И 13, эа крывает прохождение инфср ации с бпсжа 12 пора ядного сравнения на его выход. Логический уровень с инвертированного выхода первого В -триггера 15 н логический уровень О с прямого Ш1 хода второго D-триггера 16, п хзтупая на входы седьмого элемента И 17, сформулируют на его выходе логичес1шй уровень О, кото{а 1й поступит на вход гашения дешифpatqpa 18 и этим отключит его выход от приемника сообщения. Теперь рассмотрим работу усгройстьд приема при поступлении йа его вход сигналов контроля, следующих в составе импульсов служебного канала с частотой 8/п кГц и состоящий из стартовой посылки (отсутствие ймпульса канала) и г информационных посылок, О или I которых передается отсутстзтем ипи напичием импульса канапа. Первый элемент И 1 и расширитель 2 работают так же, как екшо описано в первом случае. Импульсы служебного канала, пройдя через эти элементы на вход регистра 3 сдвига, будут продвигаться по нему с помощью импульсов подставки, и первое же отсутствие импульса (стартовая посылка) запишет В регистр 3 сдвига О, Как только этот О попадет во второй разряд регистра 3 сдвига, то на выходе второго элемента И 4 появится логический ypoiaeHb/1, так как к первому его входу подключен инвертированный выход второго разряда регистра 3 сдвига, а к остальным г входам - прямые выходы остальных , а они были в состоянии до прихода ста|ргрвого сигнала, т.е. произойдет выделение стартовой посылки. На логические уровни О а составе г. ннфсрмшионных посылок второго элемента И 4 реагировать не %дег, так как стартовая нулевая посылка, подвигаясь далее по г разрядам регистра 3 сдвига, будет последовательно подавать логический уровень О на остальные г входы второго элемента И 4. Вьшелившийся положительный стартовый импульс подается с выхода второго элемента И 4 на первый вход четвертого элемента И 8 в на первый вход тре510гьего элемента И 5. Третий элемент И 5 открыт, так как на его Ьторой вход подается логический уровень I с инвертированного выхода второго В -триг гера 16 который находился в этом со- стоянии до прихода сигналов контрстга, п зп1му стартовый импульс проходит на вход дифференцирующей цепочки 6, где из его заднего фронта формируется короткий импульс. Этот импульс, перепадая на вход установки в О делителя 7 им.пульсов, устанавливает.все его разряды в состо5тие О, т.е. фазирует его работу таким образом, что импуль на его выходе появитчгя только через п тактов одновременно с выделенной стартовой посылкой следующего сигнала. Еели делитель 7 находится не в фазе с при шедшим стартовым импульсом, то на выходе четвертого элемента И 8 будет погический уровень О и работа остальной части устройства будет происходить как было описано выше, т.е. первый пришедший сигнал контроля только лишь фазирует делитель 7 импульсов. После выделения второго стартового сигнала через п тактов на входах четвертого элемента И 8 noHBKncH одновременно импульс выделенного сигнала и 1 мпульс с выхода уже сфазированного делителя 7. На время их совпадения на выходе четвертого элемента И 8 появится логический уровень . который поступает на D-входы обоих D-триггеров 15 и 16,-на тактовы входы которых, пройдя элемент 9 задерж «и поступает импульс с выхода делителя 7. Этот импульс своим передним фронтом переводит D-триггеры 15 и 16 в состояние 1, Элемент 9 задержки производи т. задержку фронта импульса с выхода делителя 7 на 0,1-0,2 мкс для обеспечения записи логической 1 с выхода четвертого элемента И 8 в D -триг геры 15 и 16, Логический уровень . с выхода первого D -триггера 15 поступает на первые входы пятого элемента И 10 и шестого элемента И 13, в результате чего импульсы подставки проходят через пятый элемент И 10, поступают на тактовый вход распределителя 11 приема, состоящего из разрядов, и производят запись в него информационного сиг нала контроля, котор 1й подается с выхода первого разряда. 3 сдвига. Запись сигналя начнется именно с первого информационного разряда, так как пятый элемент И Ю открывается в мсыент выделения стартового сигнапа, который га Ш€пяется тогда, когДа стартовая посыл 01 ка находится во втором разряде рег истра 3 сдвига 4, а в первом его разряде находится первая информационная посылка сигнала контроля. Таким образом, сигнал контроля будет записываться одновременно в регистр 3 сдвига и в распределитель 11 приема. При этом на входы блока 12 поразрядного сравнения подаются сигналы с выхода первого разряда регистра 3 сдвига и с выхода последнего разряда распределителя 11 приема. В блоке 12 поразрядного сравнения происходит поразрядное сравнение пришедшего сигнала с сигналом, хранинившимся в распределителе приема. Блок поразрядного сравне1шя работает таким образом, что на его выходе будет логический уровень О при совпадении сигналов и логический уровень при их несовпадении. При несовпаде ши сигналов логический уровень пройдя шестой элемент И 13, инвертируется инвертором 14 в логический уровень О, попадает на вход установки в О второго 5 -триггера 16 и переводит его в О . Логический уровень О с прямого выхода второго D -триггера 16 через седьмой элемент И 17 попадает на вход гашения дешифратора 18, чем отключает его выходы от приемника 19. Несовпадение пришедшего и записанного в распределитель 11 приема сигналов может быть в следующих случаях: в начальный момент времени (так как до прихода сигналов контроля разряды распределителя 11 приема могут находиться в произвольном состоянии, которое установилось в момент включения) или если произошла ошибка вследствие воздействия помехи в пришедшем сигнале, или если сменился сигнал контроия. Как только стартовый импульс (логический уровень О) дойдет до последнего разряда регистра 3 сдвига и одновременно запишется весь сигнал из символов в распределитель 11 приема, этот логический уровень О, попадая с выхода последнего разряда регистра 3 сдвига на вход установки в О первого Ё -триггера 15, переведет его в состояние О. Логический урхзвень О с прямого выхода первого) -триггера 15, попадая на вход пятого элемента И 10, закроет прохождение через него импульсов подставки на тактовый вход распределителя приема. Таким образом, в распределитель 11 приема будет записан сигнал к(жтропя и оставлен в нем до прихода следующего сигнала. Далее этот сигнал через дешифратор 18 подается к пртем

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля состояния станций радиорелейной линии связи | 1977 |

|

SU743215A1 |

| Устройство для контроля состояния станций радиорелейной линии связи | 1979 |

|

SU886277A2 |

| Устройство синхронизации по циклам | 1983 |

|

SU1172053A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для коммутации сообщений в сетях передачи данных | 1988 |

|

SU1522232A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Селектор сигналов | 1989 |

|

SU1732451A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ КОНТРОЛЯ, содержащее последовательно соединенные первый элемент 1-1, вход которого является входом устройсува, расширитель импульсов и регистр сдвига, прямой выход первого разряда которого соединен с BXiuAOM распределителя приема, выходы которого подключены через дешифратор к приемнику, а инвертированный выход второго разряда и прямые выходы остадьных раз|зядов соединены с входами второго элемента И, делитель импульсов, тактовый вход которого соединен с тактовым входом регистра сдвига и с вторым входом первого элемента И, о т л ичающееся тем, что, с целью повышения помехозаш щеннрсти приема, введены блок . поразрядного сравнения, два D -триггера, элемент задержки, Диффере1Щйрующая цепочка, инвертор, третий, четвертый, пятый, шестой и седьмой элементы И, при этом первый и второй входы блока поразрядного сравнения соединены сосгветственно с прямым выходом первого разряда регистра сдвига и с выходом последнего разряда распределителя приема, а выход 0лока поразрядного сравнения соединен с первым входом шестого элемента И, выход которого через инвертор подключен к первому входу второго D -триггера, причем выход второго элемента И соединен с первыми входами третьего и четвертого эпеменгов И, выход и второй вход которого соединен с вторыми входами первого и второго) - . триггеров и с объединенными входом элемента задержки и выходом делителя импульсов, второй вход которого через дпф 4зеренцирукмцую цепочку соединен с выходом третьего элемента И, вторЫ1 вход i которого соединен с переым выходом вгорого D-триггера, второй выход и та1|то(Л С вый вход которого соединен соответственно с первым входом седьмого элемента И и с тактовым входом первого.D-триггера и выходом элемента задержки, а второй вход и первый и второй выходы первого и-триггера соединены соответственно й выходом последнего разряда решстра сдвига, с вторыми входами пятого и шестого элементов И и с втога 1М входом седьмого элемента И, выход которого соединен с управляющим входом дешифратора, выход пятого элемента И соединен с тактовым входом распределителя приема, а первый вход соединен с вторым входокг nepBoio элемента И и является /фугим входом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-05-30—Публикация

1981-10-13—Подача