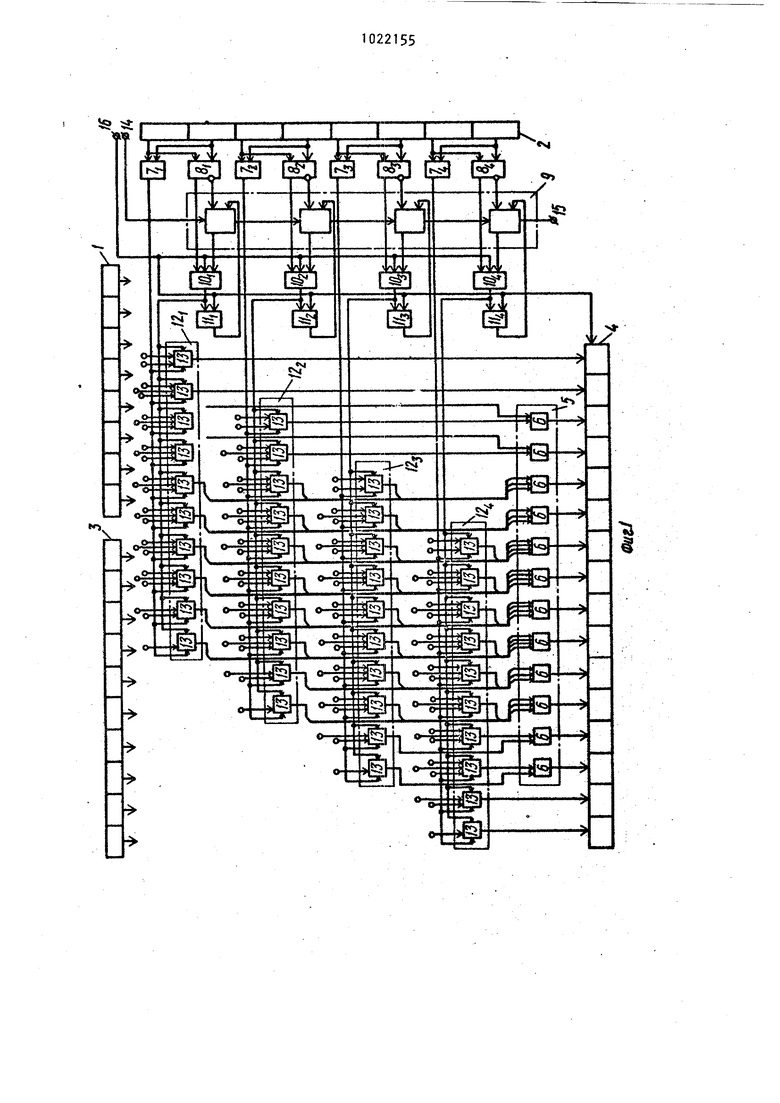

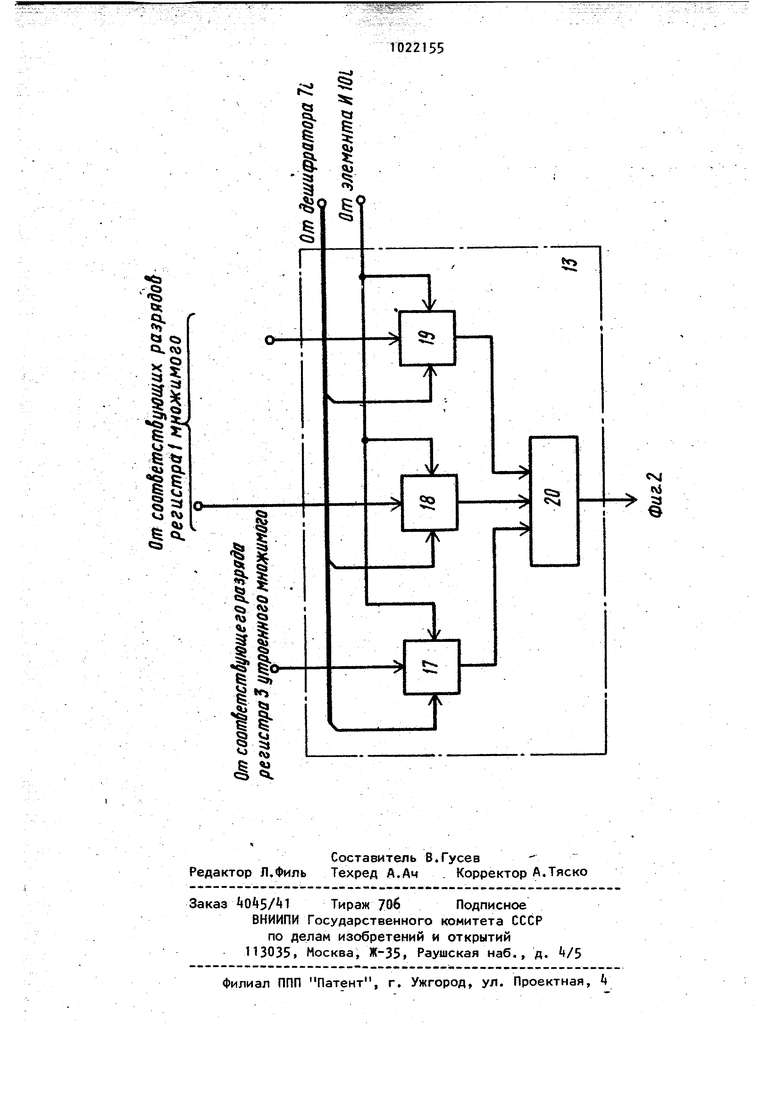

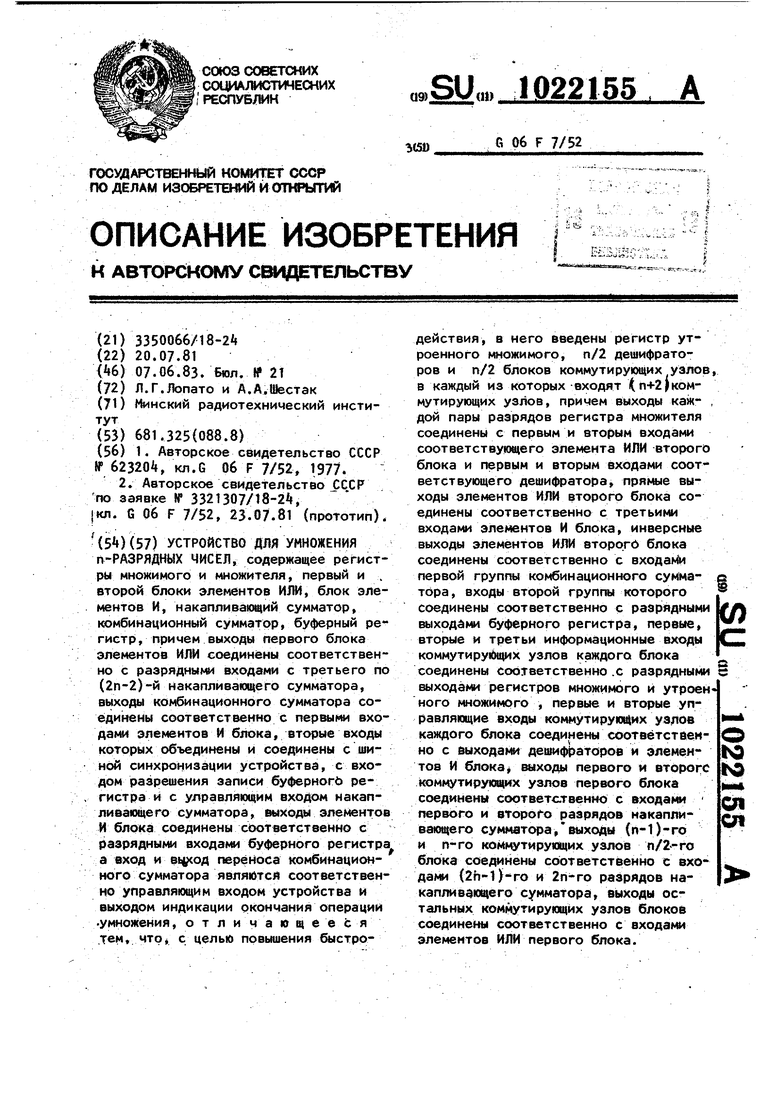

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного типа. Известно устройство для умножения п-разрядных чисел, содержащее регистры множимого и множителя, накапливающий сумматор, матрицу элементов И, первый и второй блоки элементов ИЛИ, элементы И и задержки СО . К недостаткам указанного устройства относятся относительно низкое быстродействие и использование низкотехнологичных элементов задержки для высокоплотной интегральной технологии изготовления электронных схем. Наиболее близким по технической .сущности к предлагаемому является устройство для умножения п-разрядных чисел, содержащее регистры множимого и множителя, первый и второй блоки элементов ИЛИ, блок элементов И, накапливающий сумматор, комбинационный сумматор и буферный регистр, причем выходы первого блока элементов ИЛИ соединены соответственно с разрядным входами с третьего по (2п-2)-й накап ливающего сумматора, выходы комбинационного сумматора соединены соответственно с первыми входами элементов И блока, вторые входы которых объединены и соединены с шиной синхр низации устройства, с входом разреше ния записи буферного регистра и с управляющим входом накапливающего сумматора, выходы элементов И блока соединены соответственно с разрядным входами буферного регистра, вход и выход переноса комбинационного сумма тора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения 2 3 Недостатком известного устройства является его относительно низкое быстродействие. Цель изобретения - повышение быст родействия устройства. ,1 Поставленная цель достигается тем что в устройство для умножения п-раз рядных чисел, содержащее регистры множимого и множителя, первый и втор блоки элементов ИЛИ, блок элементов накапливающий сумматор, комбинационный сумматор и буферный регистр,;причем выходы первого блока элементов ИЛИ соединены соответственно с разря ными входами с третьего по (2п-2)-й накапливающего сумматора, выходы комбинационного сумматора соединены соответственно с первыми входами элементов И блока, вторые входы которых объединены и соединены с шиной синхронизации устройства, с входом разрешения записи буферного регистра и с управляющим входом накапливающего сумматора, выходы элементов И (блока соединены соответственно с разЬядными входами буферного регистра, вход и выход переноса комбинационногЬ сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения, введены регистр утроенного , п/2 дешифраторов и п/2 блоков коммутирующих узлов, в каждый из кото|эых входят п+2) коммутирующих узлов|, причём выходы каждой пары разрядов регистра множителя соединены с первым и вторым входами соответствующего элемента ИЛИ второго блока и первым л вторым входами соответствующего дешифратора, прямые выходы элементов ИЛИ второго блока соединены соответственно с третьиБлока, инверсми входами элементов ИЛИ второго блоные выходы элементов ка соединены соответств енно с входами первой Труппы комбинаци|энного суммагора, входы второй группы которого соединены соответственна с разрядными выходами буферного региЬтра, первые вторые и третьи информационные входы коммутирующих узлов каждого блока со(здинены соответственно b разрядными выходами регистров множимого и утроенпёрвые и ного множимого, первые и вторые управляющие входы коммути|эуюЩих узлов каждого блока соединены соответственно с выходами дешифраторов и элементов И блока, выходы первого и ВТОрого коммутирующих узлоз первого блока соединены соответств1гнно с входами первого и второго разря ов накапливающего сумматора, (п-1)-го и п-го коммутирующих узлов п/2-го блока соединены соответственно с входами (2п-1)-го и 2п-го разря ов накапливающего сумматора, выходы остальных коммутирующих узлов блоков соединены соотв етственно с входами Элементов ИЛИ первого блока. Каждый коммутирующий узел блока содержит первый, второй I и третий элементы И и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И являются соответственно первым, вторым и третьим информационным входами коммутирующего узла, вторые третьи входы первого, второго и третьего элементов И являются соответст венно первым и вторым управляющими входами коммутирующего узла, а выход первого, второго и третьего элементо И соединены с входаьм элемента ИЛИ, выход которого является выходом коммутирующего узла. На фиг.1 представлена функциональ ная схема устройства для умножения п-разрядных чисел для случая на фиг.2 г функциональная схема коммутирующего узла. Устройство содержит восьмиразрядный регистр 1 множимого, восьмиразрядный регистр 2 множителя, десятиразрядный регистр 3 утроенного мно)кимого, шестнадцатиразрядный накапли вающий сумматор 4, первый блок 5 из двенадцати элементов ИЛИ 6, дешифраторы 7; 7i, второй блок из четырех элементов ИЛИ 8j- 8, комбинационный сумматор 9, блок из четырех элементов И 104, четырехразрядный буферный регистр 11|г- 11д, четыре 12. из десяти коммутирующих узлов 13 каждый, управляющий вход I выход 15 индикации окончания операци умножения и шину 16 синхронизации, причем первые информационные входы первых восьми коммутирующих узлов 13 каждого из блоков 12 соединены с соответствующими разрядными выходами регистра 1 множимого, вторые информационные входы коммутирующих узлов 13 со второго по девятый каждого из блоков 12 соединены соо ветственно с разрядными выходами регистра 1 множимого, третьи информационные входы коммутирующих узлов 13 с первого по десятый каждого из блоков 12| -124. соединены соответственно с разрядными выходами регистра 3 утроенного множимого, первые управляющие входы коммутирующих узлов 13 в каждом из блоков12 -124 объединены и соединены с соответствующими выходами дешифраторов , вторые управляющие входы коммутиру1Э1дих узлов 13 «в каждом из блоков . объединены и соединены с соответствующими выходами элементов И Oj. блока, выходы первого и второго коммутирующих узлов 13 блока 12 соединены соответственно с первым и вторым разрядными входами накапливакщего сумматора Ц, выходы девятого и десятого коммутирующих узлов 13 блока 12j соединены соответственно с входами 15то и 16-го разрядов накапливающего сумматора Л, остальные выходы коммутирующих узлов 13 блоков 12;f-12 соединены с соответствующими входами элементов ИЛИ 6 первого блока 5, выходы которых соответственно соединены с входами 3 - It-ro разрядов накапливающего сумматора А, выходы каждой пары разрядов регистра 2 множителя соединены с первым и вторым входами соответствующего элемента ИЛИ второго блокаПи первым и вторым входа- ми соответствующего дешифратора инверсные выходы элементов ИЛИ В -84 второго блока соединены соответственно с входами первой группы комбинационного сумматора 9, входы второй группы которого соединены соответственно с разрядными выходами буферного pie гистра llxj- ll., а выходы комбинационного сумматора 9 соединены соот ветственно с первые входами элементов И 104 блока, вторые входы которых объединены и соединены с шиной 16 синхронизации устройства, с входом разрешения записи буферного регистра П управляющим входом накапливающего сумматора , третьи входы элементов И lOij- 10 соединены соответственно с прямыми выходаKW элементов ИЛИ второго блока а выходы элементов И 104 соедине:ны соответственно с разрядными входами буферного регистра 11 -114 ЗД и выход переноса комбинационного сумматора 9 являются соответственно управляющим входом I устройства и выходом 15 индикации окончания операции умножения. Узел 13 коммутации содержит элементы И 17 19 и элемент ИЛИ 20, причем первые входы элементов И 17, 18 и 19 являются соответственно первым, вторым и третьим информационными входами узла 13 коммутации, вторые и третьи входы элементов И 17-19 являются соответственно первым и вторым управляющими входами узла 13 коммутации, а выходы элементов И 17-19 соединены с входами элемента ИЛИ 20, выход которого является выходом узла 13 коммутации. Устройство работает следующим образом. В исходном состоянии в регистрах 1 и 2 хранятся без знаков восьмираз1рядные соответственно множимое и множитель, в регистре 3 десятиразрядное утроенное множимое (оно можетБыть предварительно сформировано либо на сумматоре , либо с использованием дополнительной комбина ционной схемы), сумматор 4 и регистры П - 11 обнулены. По значению пар разрядов регистра 2 множителя на выходах дешифраторов 7 7л формируются соответствующие управляющие потенциалы, которые действуют на протя жении всего времени умножения Мисел . и настраивают блоки коммутирующих узлов на передачу в накапливающий сумматор Ч через блок 5 элементов ИЛИ 6 одинарного, удвоенного или утроенного значения множимого. В каждом такте работы устройства производится передача одинарного, удвоенного или утроенного значения множимого в накапливающий сумматор с выходов только одного блока 12 коммутирующих узлов. Выбор этого блока осуществляется с помощью управляющего сигнала, который формируется на выходе элемента И 10 в момент прихода сигнала на шину 16 синхронизации устройства. Подготовка и формирование этого управляющего сигнала производится одновременно с суммированием очередного частичного произведения в накапливающем сумматоре k. На управляющий вход Ik устройства на протяжении всего времени умножения подает ся потенциал, соответствующий значению логической единицы, а наличие сигнала на выходе 15 устройства озна чает окончание умножения чисел. Боле детально работу устройства рассмотри на примере умножения множимого X на множитель У 10001100. С учетом этого в исходном состоянии дешифратор 1 настраивает блок 12/ на передачу в накапливающий сумматор k утроенного значения множимого ЗХ, а дешифратор 74. настраивает блок 12 на передачу накапливающий сумматор t удвоенного значения множимого 2Х, на выходах д шифраторов 12 и 12з управляющие потенциалы не формируются. На инверсны выходах элементов ИЛИ 8 8 сформирован код , который является первым и неизменяющимся слагае:мым для сумматора 9. Вторым слагаемым дл сумматора 9 служит код В, хранящийся в регистре ГЦ- 1Ц. В исходном состоянии код , а в процессе умно жения он изменяется от такта к такту 556 i таким образом, что к мдменту окончания умножения он равен |инверсному значению кода А. Таким образом, в исходном состоянии на выход4 сумматора 9 с учетом логической , поступающей на управляющий ход 1 устройства, сформирован код С А+В+0001 0101+0000+0001 0110. В первом такте рабо-/ы устройства при приходе первого синхроимпульса на вход 16 устройства на выходе элемента И 10д формируется управляющий сигнал, который осуществляет передачу соответствующим образом сдвинутого утроенного множимого с выходов блока 12 коммутирующих узлов 13 в накапливающий сумматор k и служит логической единицей на S-входе синхронного RS-триггера Ид.(запись информации в регистр 11А осуществляется по синхроимпульсам, поступающим на вход 1б устройства).Одновременное суммированием в накапливающем сумматоре очередного частичного произведения вкомбинационном сумматореЭ осуществляется суммирование кодовА 0101 сучетом логической единицы на входе устройства, в результате на выходе комбинационного сумматора S формируется код суммы е 0101+0010+0001 1000. На втором такте работы устройства на его вход 16 по истечении времени, равного времени суммирования 10-разрядных чисел в накапливающем сумматоре k, поступает второй синхроимпульс. В результате .этого на выходе элемента И 10 формируется управляющий сигнал, который осуществляет передачу соответствующим образом сдвинутого удвоенного множимого с выходов блока 12 коммутирующих узлов 13 в накапливающий сумматор k и служит логической единицей на S-входе RS-триггера 114. Одновременно с суммированием чисел в накапливающем сумматоре Ц в комбинационном сумматоре 9 производится сложение кодов А«0101 и В 1010 с учетом логической единицы на входе 14 устройства, врезультате на выходе 15 устройства формируется сигнал, означающий окончание умножений. Таким образом, в рассмотренном случае умножение двух чисел выполнено за два такта, причем длительность такта определяется временем суммирования (п+2)-разрядных чисел в 2|} разрядном накапливающемсумматоре 4, так как суммирование чисел в комбинационном сумматоре 9

может быть организовано более быстро ввиде его меньшей разрядности.

Итак, среднее время умножения двух п-разрядных чисел в предлагаемом устройстве составляет величину

тогда как среднее время умножения двух п-разрядных чисел В известном устройстве coctaвляer величину

т - «. ср Y Чц V

где п число разрядов перемножаемых чисел;

время сумм1рования двух празрядных двоичных чисел. , Тогда выигрыш в лстродёйствии составит величину

Tj.p а

cf-YT -г - Г 5Р

Такйм образом , предлагаемое устройство позволяет сократить время умножения двух п разрядных двоичных чисел примерно в 1,3 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения п-разрядных чисел | 1981 |

|

SU985783A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU993255A1 |

| Арифметическое устройство | 2016 |

|

RU2625528C1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ п-РАЗРЯДНЫХ ЧИСЕЛ, содержащее регистры множимого и множителя, первый и . второй блоки элементов ИЛИ, блок элементов И, накапливающий сумматор, комбинационный сумматор, буферный регистр, причем выходы первого блока элементов ИЛИ соединены соответственно с разрядными входами с третьего по

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения двух празрядных чисел | 1977 |

|

SU623204A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство ССР по заявке № 3321307/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-07—Публикация

1981-07-29—Подача