113

Изобретение относится; к вычислительной технике и может быть использовано при разработке быстродействующих устройств 1ТУ1ножения асинхронного типа.

Целью изобретения является расшире- йие функциональных возможностей за счет умножения отрицательных чисел.

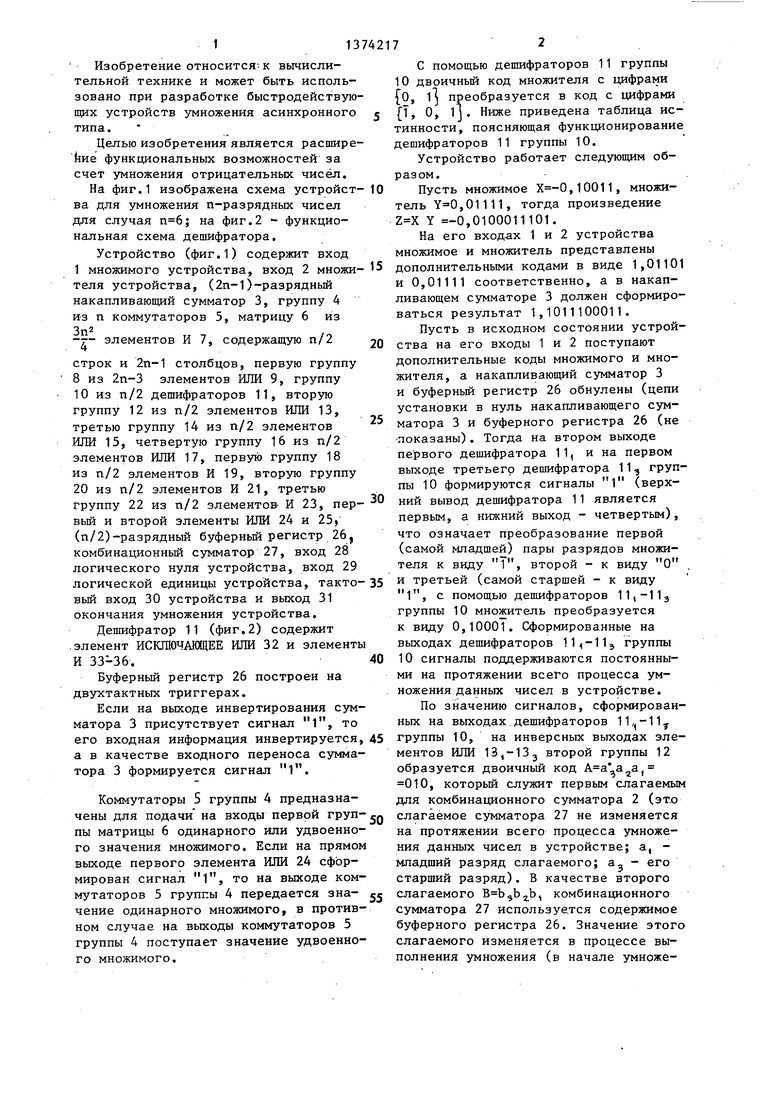

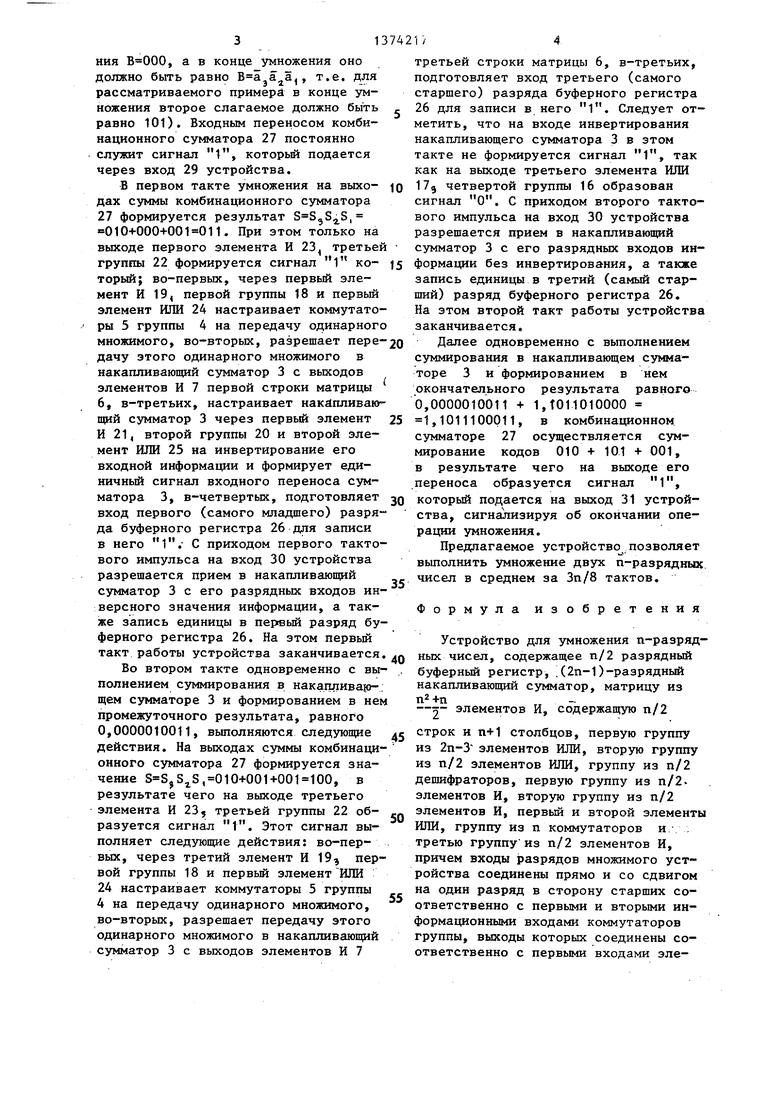

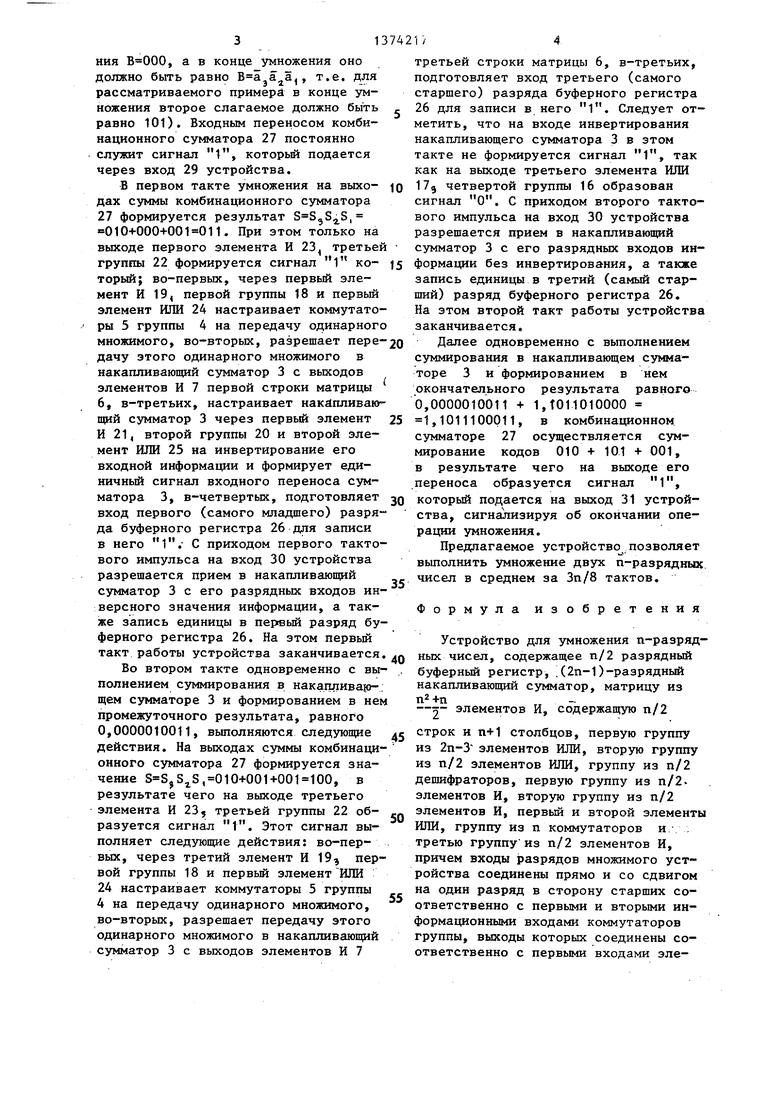

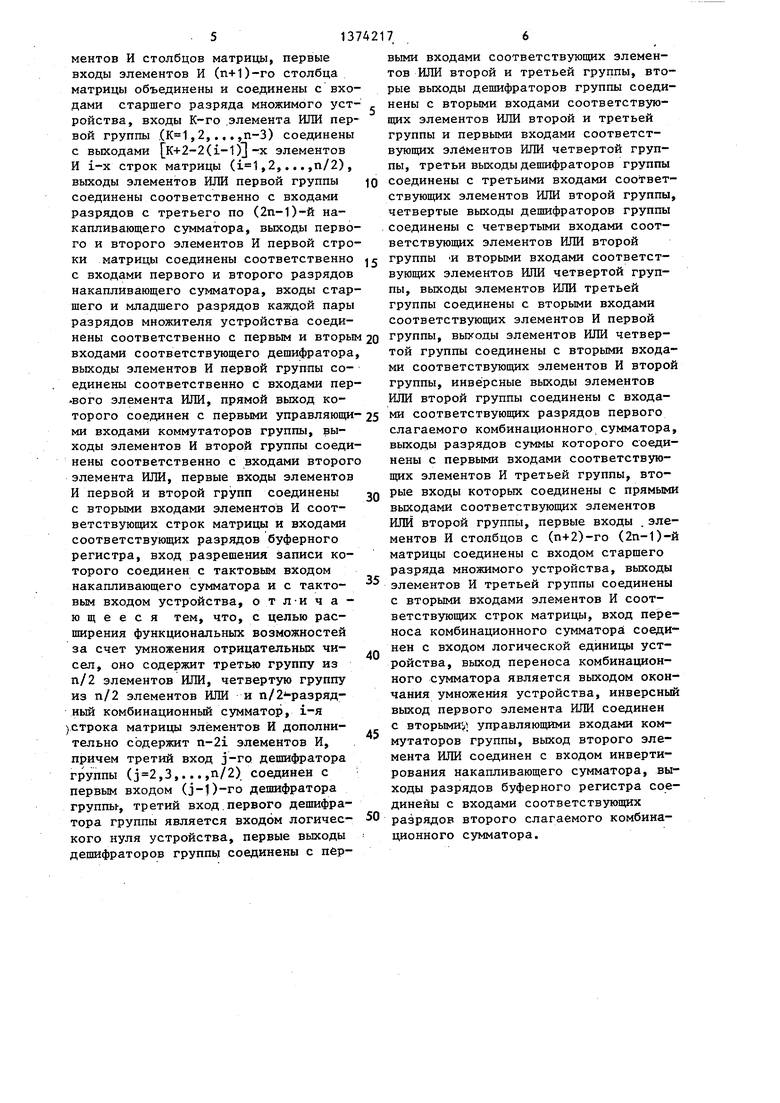

На фиг.1 изображена схема устройст- ва для умножения п-разрядных чисел для случая на фиг.2 - функциональная схема дешифратора.

Устройство (фиг.1) содержит вход 1 множимого устройства, вход 2 множи- теля устройства, (2п-1)-разрядный накапливающий сумматор 3, группу 4 из п коммутаторов 5, матрицу 6 из

Зп2

-г- элементов И 7, содержащую п/2

строк и 2п-1 столбцов, первую группу 8 из 2п-3 элементов ИЛИ 9, группу 10 из п/2 дешифраторов 11, вторую группу 12 из п/2 элементов ИЛИ 13, третью группу 14 из п/2 элементов ИЛИ 15, четвертую группу 16 из п/2 элементов ИЛИ 17, первую группу 18 из п/2 элементов И 19, вторую группу 20 из п/2 элеме:нтов И 21, третью группу 22 из п/2 элементов- И 23, пер- вый и второй элементы ШШ 24 и 25 (п/2)-разрядный буферный регистр 26, комбинационный сумматор 27, вход 28 логического нуля устройства, вход 29 логической единицы устройства, такте- вый вход 30 устройства и выход 31 окончания умножения устройства.

Дешифратор 11 (фиг.2) содержит .элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 32 и элементы И 33-36.

Буферный регистр 26 построен на двухтактных триггерах.

Если на выходе инвертирования сумматора 3 присутствует сигнал 1, то его входная информация инвертируется, а в качестве входного переноса тора 3 формируется сигнал 1.

Коммутаторы S группы 4 предназначены для подачи на входы первой груп- пы матрицы 6 одинарного или удвоенного значения множимого. Если на прямом выходе первого элемента ИЛИ 24 сформирован сигнал 1, то на выходе коммутаторов 5 группы 4 передается зна- чение одинарного множимого, в противном случае на выходы коммутаторов 5 группы 4 поступает значение удвоенного множимого.

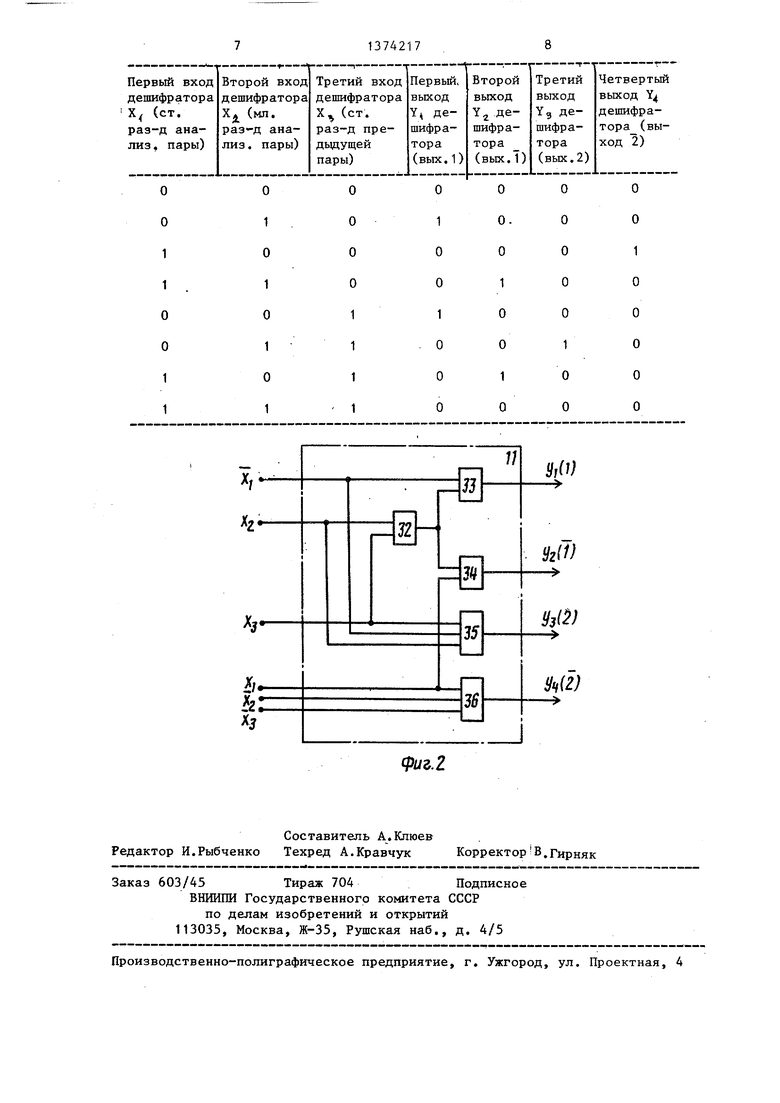

с помощью дешифраторов 11 группы 10 двоичньй код множителя с цифрами {о, 1 преобразуется в код с цифрами Т, О, 11. Ниже приведена таблица истинности, поясняющая функционирование дешифраторов 11 группы 10.

Устройство работает следующим образом.

Пусть множимое ,10011, множитель 0,01111, тогда произведение Y -0,0100011101.

На его входах 1 и 2 устройства множимое и множитель представлены дополнительными кодами в виде 1,0110 и 0,01111 соответственно, а в накапливающем сумматоре 3 должен сформироваться результат 1,1011100011.

Пусть в исходном состоянии устройства на его входы 1 и 2 поступают дополнительные коды множимого и множителя, а накапливающий сумматор 3 и буферньм регистр 26 обнулены (цепи установки в нуль накапливающего сумматора 3 и буферного регистра 26 (не показаны). Тогда на втором выходе пе рвого дешифратора 11, и на первом выходе третьего дешифратора 11 группы 10 формируются сигналы 1 (верхний вывод дешифратора 11 является первым, а нижний выход - четвертым), что означает преобразование первой (самой мпадшей) пары разрядов множителя к виду 1, второй - к виду О и третьей (самой старшей - к виду 1, с помощью дешифраторов 11,-11з группы 10 множитель преобразуется к виду 0,10001. Сформированные на выходах дешифраторов , группы 10 сигналы поддерживаются постоянными на протяжении всего процесса умножения данных чисел в устройстве.

По значению сигналов, сформированных на выходах.дешифраторов 11,,-11 группы 10, на инверсных выходах элементов ИЛИ 13,-13j второй группы 12 образуется двоичный код а . 010, который служит первым слагаемым для комбинационного сумматора 2 (эт.о слагаемое сумматора 27 не изменяется на протяжении всего процесса умножения данных чисел в устройстве; а, - младший разряд слагаемого; а„ - его старший разряд). В качестве второго слагаемого ,, комбинационного сумматора 27 используется содержимое буферного регистра 26. Значение этого слагаемого изменяется в процессе выполнения умножения (в начале умноже313

ния , а в конце умножения оно должно быть равно , т.е. для рассматриваемого примера в конце умножения второе слагаемое должно быть равно 101). Входным переносом комбинационного сумматора 27 постоянно служит сигнал 1, которьй подается через вход 29 устройства.

В первом такте умножения на выхо- дах суммы комбинационного сзгмматора 27 формируется результат ,, 010+000+001 011. При этом только на выходе первого элемента И 23, третьей группы 22 формируется сигнал 1 ко- торый; во-первых, через первый элемент И 19, первой группы 18 и первый элемент ИЛИ 24 настраивает коммутаторы 5 группы 4 на передачу одинарного множимого, во-вторых, разрешает передачу этого одинарного множимого в накапливающий сумматор 3 с выходов элементов И 7 первой строки матрицы 6, в-третьих, настраивает накйпливаю- щий сумматор 3 через первьй элемент И 21, второй группы 20 и второй элемент ИЛИ 25 на инвертирование его входной информации и формирует единичный сигнал входного переноса сумматора 3, в-четвертых, подготовляет вход первого (самого младшего) разря да буферного регистра 26 дая записи в него 1.- С приходом первого тактового импульса на вход 30 устройства разрешается прием в накапливающий сумматор 3 с его разрядных входов инверсного значения информации, а также запись единицы в пер®ьй разряд буферного регистра 26. На этом первый такт работы устройства заканчивается.

Во втором такте одновременно с вы- полнением сзпимирования в накапливаю-, щем сумматоре 3 и формированием в нем промежуточного результата, равного 0,0000010011, выполняются следующие действия. На выходах суммы комбинаци- онного сумматора 27 формируется значение ,010+001+001 100, в результате чего на выходе третьего элемента И 23, третьей группы 22 об

разуется сигнал 1. Этот сигнал выполняет следующие действия: во-первых, через третий элемент И 19, первой группы 18 и первьй элемент ИЛИ 24 настраивает коммутаторы 5 группы 4 на передачу одинарного множимого, во-вторых, разрешает передачу этого одинарного множимого в накапливающий сумматор 3 с выходов элементов И 7

4

Q 5 0 5 Q .«

. j

5

0

5

третьей строки матрицы 6, в-третьих, подготовляет вход третьего (самого старшего) разряда буферного регистра 26 для записи в него 1. Следует отметить, что на входе инвертирования накапливающего сумматора 3 в этом такте не формируется сигнал 1, так как на выходе третьего элемента ИЛИ 17з четвертой группы 16 образован сигнал О. С приходом второго тактового импульса на вход 30 устройства разрешается прием в накапливающий сумматор 3 с его разрядных входов информации без инвертирования, а также запись единицы в третий (самый старший) разряд буферного регистра 26. На этом второй такт работы устройства заканчивается.

Далее одновременно с вьтолнением суммирования в накапливающем сумматоре 3 и формированием в нем окончательного результата равного 0,0000010011 + 1,1011010000 1,1011100011, в комбинационном сумматоре 27 осуществляется суммирование кодов 010 + 101 + 001, в результате чего на выходе его переноса образуется сигнал 1, который подается на выход 31 устройства, сигнализируя об окончании операции умножения.

Предпагаемое устройство позволяет

О

выполнить умножение двух п-разрядных чисел в среднем за Зп/8 тактов.

Формула изобретения

Устройство для умножения п-разрядных чисел, содержащее п/2 разрядный буферный регистр, Х2п-1)-разрядный накапливающий сумматор, матрицу из

п2+п „ - -2 элементов И, содержащую п/2

строк и п+1 столбцов, первую группу из 2п-3 элементов ИЛИ, вторую группу из п/2 элементов ИЛИ, группу из п/2 дешифраторов, первую группу из п/2. элементов И, вторую группу из п/2 элементов И, первый и второй элементы ИЛИ, группу из п коммутаторов и . третью группу из п/2 элементов И, причем входы разрядов множимого устройства соединены прямо и со сдвигом на один разряд в сторону старших соответственно с первыми и вторыми информационными входами коммутаторов группы, выходы которых соединены соответственно с первыми входами эле513

ментов И столбцов матрицы, первые входы элементов И (п+1)-го столбца матрицы объединены и соединены с входами старшего разряда множимого устройства, входы К-го .элемента ИЛИ первой группы .(,2,.,. ,п-3) соединены с выходами к+2-2(1-1)-X элементов И i-x строк матрицы (,2,...,п/2), выходы элементов ИЛИ первой группы соединены соответственно с входами разрядов с третьего по (2п-1)-й накапливающего сумматора, выходы первого и второго элементов И первой строки матрицы соединены соответственно с входами первого и второго разрядов накапливающего сумматора, входы старшего и младшего разрядов каждой пары разрядов множителя устройства соединены соответственно с первым и вторым входами соответствующего дешифратора, выходы элементов И первой группы соединены соответственно с входами пер- вого элемента ИЛИ, прямой выход которого соединен с первыми управляюш - ми входами коммутаторов группы, выходы элементов И второй группы соединены соответственно с входами второго элемента ИЛИ, первые входы элементов И первой и второй групп соединены с вторыми входами элементов И соот- Бетствуюш;их строк матрицы и входами соответствующих разрядов буферного регистра, вход разрешения записи которого соединен с тактовым входом накапливающего сумматора и с тактовым входом устройства, о т л-и ч а - ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет умножения отрицательных чисел, оно содержит третью группу из п/2 элементов ИЛИ, четвертую группу из п/2 элементов ИЛИ и п/2 -разряд- ный комбинационный сумматор, i-я )строка матрицы элементов И дополнительно содержит n-2i элементов И, причем третий вход j-ro дешифратора группы (,3,...,п/2) соединен с первым входом (j-i)-ro дешифратора rpynnbf, третий вход.первого дешифратора группы является входом логического нуля устройства, первые выходы дешифраторов группы соединены с пбр

0 5

0

5

0

5

0

выми входами соответствующих элементов ИЛИ второй и третьей группы, вторые выходы дешифраторов группы соединены с вторыми входами соответствующих элементов ИЛИ второй и третьей группы и первыми входами соответствующих элементов ИЛИ четвертой группы, третьи выходы дешифраторов группы соединены с третьими входами соответствующих элементов ИЛИ второй группы, четвертые выходы дешифраторов группы соединены с четвертыми входами соот- ветствуюших элементов ИЛИ второй группы И вторыми входами соответствующих элементов ИЛИ четвертой группы, выходы элементов ИЛИ третьей группы соединены с вторыми входами соответствующих элементов И первой группы, выходы элементов ИЖ четвертой группы соединены с вторыми входами соответствующих элементов И второй группы, инверсные выходы элементов ИЛИ второй группы соединены с входами соответствующих разрядов первого слагаемого комбинационного сумматора, выходы разрядов суммы которого соединены с первыми входами соответствующих элементов И третьей группы, вторые входы которых соединены с прямыми выходами соответствующих элементов ИЛИ второй группы, первые входы . элементов И столбцов с (п+2)-го (2п-1)-й матрицы соединены с входом старшего разряда множимого устройства, выходы элементов И третьей группы соединены с вторыми входами элементов И соот- ветствуюш 1х строк матрицы, вход переноса комбинационного сумматора соединен с входом логической единицы устройства, выход переноса комбинационного сумматора является выходом окончания умножения устройства, инверсный выход первого элемента ИЛИ соединен с вторыми ; управляющими входами коммутаторов группы, выход второго элемента ИЛИ соединен с входом инвертирования накапливающего сумматора, выходы разрядов буферного регистра соединены с входами соответствующих разрядов второго слагаемого комбинационного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного / А --j f-i f-г 4г4 iVl 5 lYl/l/l типа. Целью изобретения является расширение функциональных возможностей за счет умножения отрицательных чисел. Поставленная цель достигается тем, что устройство для умножения п-разрядных чисел, содержащее накапливающий сумматор I 3, группу 4 коммутаторов 5, матрицу 6 элементов И 7, группу 8 элементов ИЛИ 9, группу 10 дешифраторов 11, группу 12 элементов ИЛИ 13, группу 18 элементов И 19, группу 20 элементов И 21, группу 22 элементов И 23, элементы ИЛИ 24, 25 и буферный регистр 26, дополнительно содержит группы 14 и 16 элементов ИЛИ и комбинационный сумматор 27. 2 ил. ,Л Л

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1193667A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-15—Публикация

1986-08-04—Подача