(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ П-РАЗРЯДНЫХ

ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU993255A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

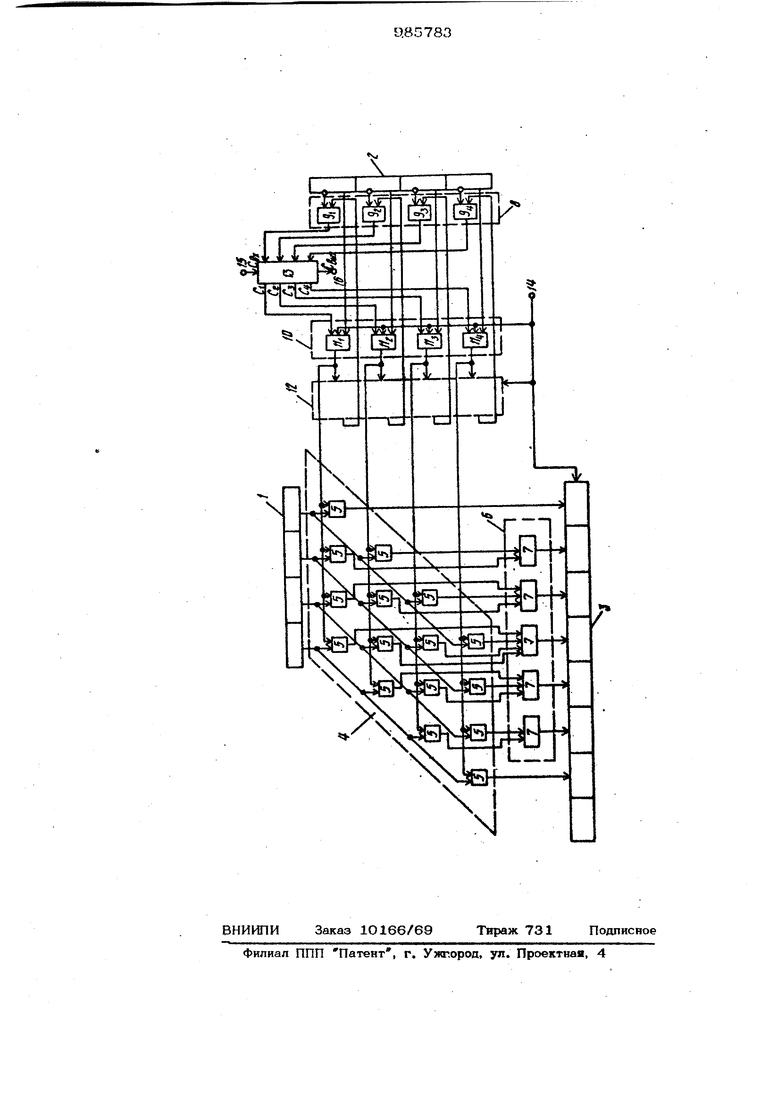

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхрон го типа. Известно устройство для умножения t -разрядных чисел, содержащее п-раа-; рядные регистры множимого, множителя к результата, 2п-разрядный сумматор и блок управления 1 1Недостатком известного устройства является низкое быстродействие. Известно усл ройство для умножения п -разрядных чисел, содержащее г -разрядные регистры множимого и множителя, 2 п -разрядный сумматор, матрицу вз п элементов И, блок элементов ИЛИ по два элемента И для каждого разряда регистра множителя 1.2. Недостатками данного устройства яв ляются разрушение информации в регвст ре множителя в процессе умножения и невысокое быстродействие. Наиболее близким к предлагаемому по технической сущности является устройство для умножения h -разрядных чисел, содержащее п -разрядный регистр множимого, п-разрядный регмстр множителя, (2п-1)-разрядный накапливающий сумматор, матрицу вз п элементов И, пер вый (2п-3)-разрадный блок элементов ИЛИ, второй п -разрядный блок элемевн тов ИЛИ и п-разрядный блок элементов И, причем выходы регистра множимого соответственно соединены с перяаой входов матрицы элементов И, ЕЫХЕ ды (2,...2п-3)-го разрядов которой соединены с соответствующими входами , эл0 1ентов ИЛИ первого блока элементов ИЛИ, выходы элементов ИЛИ первого блока элементов ИЛИ соответственно сот единены с (2,. ..,2п-3) входными разрядами вакаштивающего сумматора, и (2и-1) входные; разряды которого соответственно соединены с первыми в с выходами матрицы элементов И, вторая хфуппа входов матрицы 39 .: абментов И соответственно соединена Свыходами элементов И блока элементов И, первые входы которых соответст.венно соединены с прямыми выходами ре гистра множителя З . Недостатком известного устройства является его относительно нвзкое быстро действие. Цель изобретения - повышение быстро действия устройства. Поставленная цель достигается тем, что в устройство для умножения п -разрядных чисел, содержащее п -разрядный регистр множимого, h -разрядный регистр множителя, (2.П-1 )-разрядный накапливающей сумматор, матрицу №з п элементов. И, первый (2 п-3)-разрядный блок элементов ИЛИ, второй п -разрядный блок элементов ИЛИ и п -разрядный блок элементов И, причем выходы регистра множимого соответственно соединены с первой 1тэуппой входов матрицы элементов И, выходы (2,...,2п .-3)-го разрядов которой соединены с соответствующими входами элементов ИЛИ первого блока элементов ИЛИ, выходы элементов ИЛИ первого блока элементов ИЛИ соответственно соединены с (2,...,2 п-3)-м входными разрядами накапливающего сумматора, первый (2п 1)-й входные разрядь которого соответственно соединены с первым и выходами матрицы элементов И, вторая группа входов матрицы элементов И соответственно соединена с выходами элементов И блока элементов И, первье входы которых соответственно соединены с ирямымк выходами регистра множителя, : введены п-разрядньШ diTJxjpi-ibiH регистр и п-разрядный комбинационный сумматор, причем прямые . выходы буферного регистра соответствевно соединены с первыми входами элементов ИЛИ второго блока элементов ИЛ вторые входы которых соответственно соединены с инверсными выходами регист ра множителя, а выходы соответственно соединены с входами комбинационного сумма тора ,вы ходы комбинационного сум матора соответственно соединены с вторы ми входами элементов И блока элементов И, третьи входы которых объединены и соединены с шиной синхронизации 5стройства, которая соединена с входом разрешения записи буфернохт регистра и с утгравляющим входом накапливающего сумматора, вход переноса ксмбинациояного сумматора яымется згправляющим входом устройства, выход переноса комбияч3ционного сумматора является выходом индикации окончашш операции умножения, выходы элементов И блока элементов И соответственно соединены с разрядными входами буферного регистра. На чертеже изображена структурная ; схема устройства для умножения п -разрядных чисел. Устройство для умножения п -разряд- ных чисел содержит п -разряный регистр 1 множимого, п -разрядный регистр 2 множителя, (2п -1 )-разрядный накапливающий сумматор 3, матрицу 4 из| п элементов И 5, первый (2 п-3)-рааряд- ный блок 6 элементов ИЛИ 7, второй п-разрядный блок 8 элементов ИЛИ 9, п -разрядный блок 10 элементов И 11, п-разрядный буферный регистр 12, п разрядный комбинационный сумматор 13, цтну 14 синхронизации, управляющий вход 15 и выход 16 индикации окончания операции умножения, причем выходы рогистра 1 множимого соответственно соединены с первой группой входов матрицы 4 элементов И 5, Е ЛХОДЫ (2,...,2п-3)го разрядов которой соединены с соответствующими входами элементов ИЛИ 7 первого блока б элементов ИЛИ 7, выходы элементов ИЛИ 7 первого блока 6 элементов ИЛИ 7 соответственно соединены с (2,...,2п-3)-м входными разрядами накапливающего сумматора 3, первый (2п-1)-ый входные разряды которого соответственно соединены с первым и выходами матрицы 4 элементов И 5, вторая грухша входов матрицы 4 элег ентов И 5 соответственно соединена с выходами элементов И 11 блока 1О элементов И 11, первые входы которых соответственно соегинены с прямыми выходами регистра 2 множителя, вторые входы соответственно соединены с выходами комбинационного сумматора 13, а третьи входы объединены и соединены с шиной 14 синхронизации устройства, прямые выходы буферного улегистра 12 соответственно соединеиы с вхо.дами элементов ИЛИ 9 второго блока 8 элементов ИЛИ 9, вторые входы которых соответственно соединешы с инвероными выходами регистра 2 множителя, а выходы соответственно соединены с входами комбинационного сумматора 13, шиш 14 синхронизации устройства соединена с входом разрешения записи буферного регистра 1.2 ъ с управляющим входом накагагаваюпюго сумматора 3, управляющий вход 15 устройства coeew нен с входом переноса комбинационного , сумматора 13, выход переноса которогосоединен с выходом 16 иншпсашга окончания операции умножения устройства, выходы элементов И 11 блока 1О элементов И соответственно соединены с разрядными входами буферного решет- ра 12. Устройство работает следующим образом. Пусть требуется умножить п -разрядное множимое X на множитель 1О10. В исходном состоянии в регистре 1 множимого хранится двоичный код числа X без знака, в регистре 2 множ теля - двоичный код числа У без знака, накащшваюигай сумматор 3 и буферный регистр 12 обнулены, на управляющий вход 15 устройства подан сигнал в виде уровня логической единицы, а на Bbixoae комбинационного сумматора 13 оформит рован результат ,2.0101 + +0001« 011О (суммирование инверсного значения множителя с единицей, поступающей в младший разряд сумматора с управляющего входа 15 устройства). При подаче на шину 14 синхронизации устройства синхроимпульса на выходе эле мента И И блока 10 элементов И 11 формируется управляющий сигнал, которы производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 5 второй строки матрицы 4 элементов И 5 через блок 6 элементов ИЛИ 7 в накапливающий сумматор 3 и устанавливает в единицу второй разряд буферного регистра 12с разрешения син хроимпульса, поступающего на его вход разрешения записи. После окончания действия синхроимпульса одновременно с суммированием частичного произведен. в накапливающем сумматоре 3 в комбинаивонвс сумматоре 13 формируется результат ОС4С С С О1114ОО01 1ОО Во втором такте работы устройства с приходом второго синхроимпульса на шину 14 синхронизации устройства на выходе четвертого элемента И 11 бло;ка 10 элементов И 11 формиру ется управляющий сигнал, который производит передачу соответствующим образом сдв1 нутого множимого с выходов элементов И 5 четвертой строки матршш 4 элемен тов И 5 через блок б элементов ИЛИ 7 в накапливающий сумматор 3 н устанавлстает в единшху четвертый разряд буфер вогч регис-гра 12. После окончания aeft.ствия второго синхроимпульса одновр мевш с суммироваШ1ем частичного произведения в накапливающем сумматоре 3, в комбинационном сумматоре 13 форм1 о руется результат О С 0 020 1111+ Ю001 ООООи возникает перенос Cg|jjy l. Но так как ,го на вь1ходе 16 устройства присутствует сигнал,который означает окончание операции умножения чисел.Таким образом,в рассмотренном примере умнЬж&ние чисел выполнено в два такта,причем длительность такта(временной интервал меяшу двумя йоследовйтельнымиейИз роимпульсами,поступающими на шину 14 устройства) определяется временем суммирования п -разрядных чисел в накапливающем сумматоре 3, так как прибавление единицы к младшему разряду п-разрядного числа, поступающего на вход комбинационного сумматора 13., может быть орга низовано более быстро, чем суммирование п -разрядных чисел в накапливающем сумматоре 3. Итак, среднее время умножения двух п -разрядных чисел в предлагаемом yciv. ройстве составляет величину Т ср 2 сум Увеличение быстродействия предлага- емого устройства в сравнении с прототипом достигнуто за счет исключения из общего времени умножения составляющей 2nf, определяющей задержку сигнала на VI элементах ЦЩЛ второго блока элементов ИЛИ и п элементах И первого (.второго) блока элементов И, управля1О. щего выборкой соответствующим образом сдвинутого множимого. В предлагаемом устройстве формирование такого управляющего сигнала фактвяески производится одновременно с суммированием очередного частичного произведения в накашшва- ющ&л сумматоре. Формула изобретения Устройство для умножения п -разрядных чисел, содержащее п -разрядный регистр множимого, г -разрвэдный регистр множителя, ()-разрядный накаплвн вающий сумматор, матрицу из п эпемевн тов И, первый (2п-3)-разрядный бп(ж апемевтов ИЛИ, второй п -разрядный блок элементов ИЛИ в п -разрядный блок эл@.1ентов И, причем Kunoaii регистра множимого соответственно соединены с первой грушюй входов матрицы элементов И, выхода (2,...,2«1-3)-го разрядов которой соединены с соответствутощими входами элементов ИЛИ первого бпока элементов ИЛИ, выходы элементов ИЛИ первого блока элементов ИЛИ соответственно соединены с (2,..,,2п-3)-м входными разрядами накапливающего сугиматора, первый и (2п-1)-й входные разряды которого соответственно соедине№1 с первым и выходами матрицы элементов И, вторая группа входов матринь элементов И соответственно сое динена с выходами элементов И блока элементов И, первые входы которых соответственно соединены с прямыми выходами регистра множителя, отличаю ш е е с я тем, что, с целью повыше ния быстродействия, в нех введены п разрядный буферный регистр и п -разрядный комбинационный сумматор, причем прямые выходы буферного регистра соответственно соединены с первыми входами элементов ИЛИ второго блока элементов ИЛИ, вторые входы которых соответствен но соединены с инверсными выходами регистра множителя, а выходы соответст- венно соединены с входами комбинаиионЭ838 ного сумматора, выходы комбинационного сумматора соответственно соединены с вторыми входами элементов И блока элементов И, третьи входы которых объединены и соединены с шиной синхронизации устройства, которая соединена с входом разрешения записи буферного регистра и с управляющим входом накапливающего сумматора, вход переноса комбинационн1 го сумматора является управляющим входом устройства, выход переноса комбина1ШОННОГО сумматора является выходом индикации окончания .операции умножения выходы элементов И блока элементов И соответственно соединеньт с разрядными входами буферного регистра. Источники информации, принятые во внимание при экспертизе 1. КарцевМ.А. Арифметика цифровых машин, М., Наука, 1969, с. 350, 364. 2.Авторское свидетельство СССР fc 48274О, кл. G 06 F 7/52, 1974. 3.Авторское свидетельство СССР № 623204, кл. G 06 F 7/52, 1977 (прототип).

Авторы

Даты

1982-12-30—Публикация

1981-07-23—Подача