(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ п-РАЗРЯДНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения п-разрядных чисел | 1981 |

|

SU985783A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1003077A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения асинхронного типа.

Известно устройство для умножения п-разрядных чисел, содержащее п-разрядные регистры множимого, множителя и результата, сумматор и блок управления fl.

Недостатком известного устройства является его низкое быстродействие, вызванное тем, что время, затрачиваемое на сдвиги инфосжации в регистрах, не зависит от числа единиц в разрядах множителя и всегда равно Htcg.

Известно также устройство для умножения п-разрядных чисел, содержащее п-разрядные регистры множимого и множителя, 2п-разрядный сумматор, матрицу из п элементов И, блок из (2п-3) элементов ИЛИ и два блока из п элементов И каждый 1..

Недостаток известного устройства низ кое быстродействие, поскольку длительность такта работы устройства зависит от времени переходного процесса во втором блоке элементов И.

Наиболее близким к предлагаемому является устройство дпя умножения п-разрядных чисел, содержащее п-разс рядный регистр множимого, )п-раэряд-ный регистр множителя, {2п-1)-разрядный накапливакяций сумматор, матрицу, из п элементов И, (2 п -3)-разрядный |блок элементов ИЛИ, п-разрядный

Q элементов и и п-разрядньш комбина ционный сумматор, причем выходы регистра в oжимoгo соответственно соедщнены с первой группой входов матрицы элементов И, выходы (2,| ..., 2п-2)-го .разрядов которой соединены

15 с соответствующими входами элементов ИЛИ блока элементов ШШ, выходы элементов. ИЛИ которого соответственно соединены с (2, ..., 2п-2)-ми входными разрядёши накапливающего сум-.

20 матора, первый и (2п-1)-й разрядные входы накапливающего cy « aтopa ссютветственно соединены с первым и п -м клходами матрицы элементов И, вторая группа входов которой соответствен25но соединена с выходами элементов И блока элементов И, первые входы которых соответственно соединены с прямлвя выходами регистра множителя, вторые входы элементов И блока эле30ментов И соответственно соединены

с выходами комбинационного сумматора , а третьи входы объединены и соединены с управляющим входом накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения з.

Недостаток известного устройства сложность.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем что в устройстве для умножения п-разрядных чисел, содержащем п-разрядный регистр ножимого, п-разрядный регистр множителя, (2п-1)-разрядный накапливающий сумматор, матрицу из п элементов И, {2п-3)-разрядный блок элементов ИЛИ, п-разрядный блок элементов И и п-разрядный комбинационный сумматор, причем выходы регистра множимого соответственно соединены с первой группой входов матрицы элементов и, выходы (2, ..., 2п-2)-го разрядов которой соединены с соответствующими входами элементов ИЛИ блока элементов ИЛИ, выходы элементов ИЛИ которого соответственно соединены с (2, ..., 2п-2)-ми входными разрядами накапливающего сумматора, первый и (2п-1)-й разрядные входы накапливающего сумматора соответственно соединены с первым и выходами матрицы элементов И, вторая группа входов которой соответственно соединена с выходами элементов И бло ка элементов И, первый входы элементов И блока элементов и соб тветственно соединены с прямыми выходами peiгистра множителя, вторые входы элементов И блока элементов И соответственно соединены с выходами комбинационного сумматора, а третьи входы объединены и соединены с управляющим входом йакапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения, выходы элементов И блока элементов И соответственно соединены с входами установки в нуль п разрядов регистра множителя, инверсные выходы которого соответственно соединены с входами комбинационного сумматора, а вход разрэаения записи регистра множителя соединен с шиной синхронизации устройства.

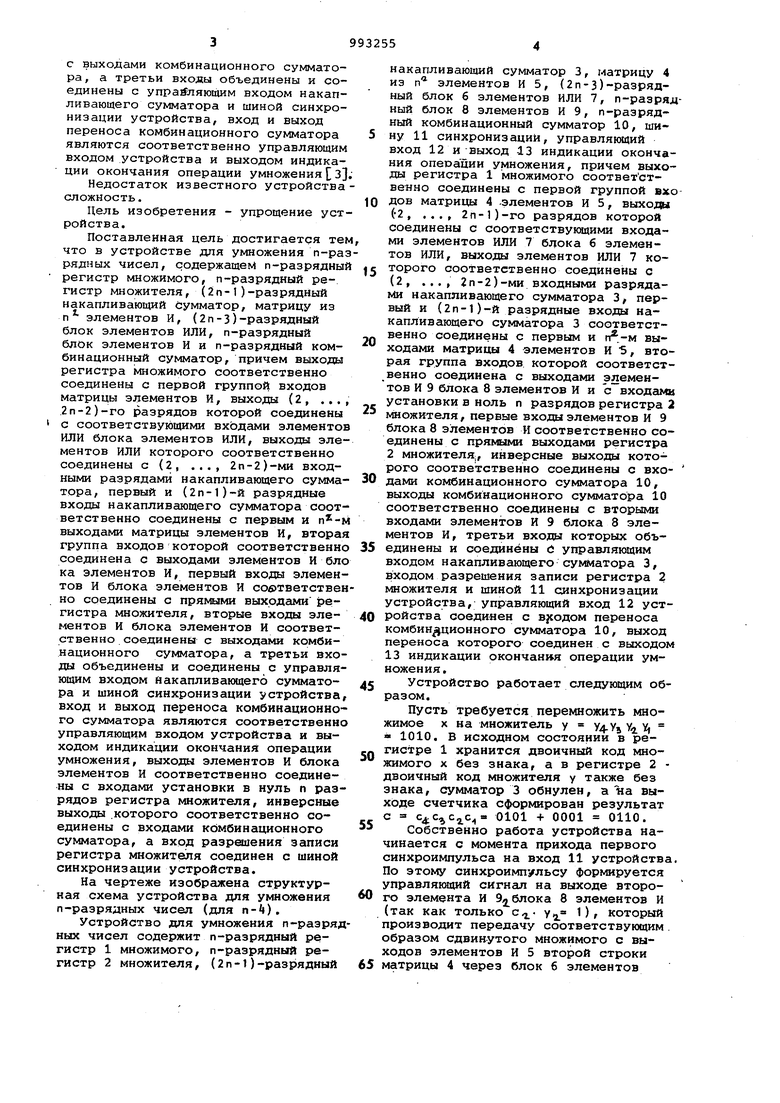

На чертеже изображена структурная схема устройства для умножения п-разрядных чисел (для n-i).

Устройство для умножения п-разрядных чисел содержит п-разрядный регистр 1 множимого, п-разрядный регистр 2 множителя, (2п-1)-разрядный

накапливающий сумматор 3, матрицу 4 из п элементов И 5, (2п-З)-разрядный блок б элементов ИЛИ 7, п-разрядный блок 8 элементов И 9, п-разрядный комбинационный сумматор 10, шину 11 синхронизации, управляющий вход 12 и-выход 13 индикации окончания операции умножения, причем выходы регистра 1 множимого соответственно соединены с первой группой вхо дов матрицы 4 -элементов И 5, выходы (2 , . . . , 2п- 1 )-го разрядов которой соединены с соответствукяцими входами элементов ИЛИ 7 блока б элементов ИЛИ, выходы элементов ИЛИ 7 которого соответственно соединены с (2, ..., гп-2)-ми входными разрядаKftf накапливающего сумматора 3, первый и (2п-1)-и разрядные входы накапливающего сумматора 3 соответственно соединены с первым и п.-м выходами матрицы 4 элементов И 5, вторая группа входов которой соответственно соединена с выходами элементов И 9 блока 8 элементов И и с входс1мв установки в ноль п разрядов регистра 2 множителя, первые входы элементов И 9 блока 8 элементов И соответственно соединены с прямыми выходами регистра 2 множителя;, инверсные выходы которого соответственно соединены с входами комбинационного сумматора 10, выходы комбинационного сумматора 10 соответственно соединены с вторыми входами элементов И 9 блока 8 элементов И, третьи входы которых объединены и соединены б управляющим входом накапливающего сумматора 3, входом разрешения записи регистра 2 множителя и шиной 11 синхронизации устройства, управляющий вход 12 устройства соединен с в}содом переноса кoмбин Jциoннoгo сумматора 10, выход переноса которого соединен с ВЕЛХОДОМ 13 индикации окончання операции умножения.

Устройство работает следующим образом.

Пусть требуется перемножить множимое X на множитель у . У) « 1010. В исходном состоянии в регистре 1 хранится двоичный код множимого X без знака, а в регистре 2 двоичный код множителя у также без знака, сумматор 3 обнулен, а на выходе счетчика сформирован результат с 0101 + 0001 ОНО.

Собственно работа устройства начинается с момента прихода первого синхроимпульса на вход 11 устройства По этому синхроимпульсу формируется управлякиций сигнал на выходе второго элемента И 92 блока 8 элементов И (так как только с. 1), который производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 5 второй строки матрицы 4 через блок 6 элементов

ИЛИ 7 в накапливающий сумматор 3, а также осуществляет установку второго разряда регистра 2 множителя в нуль с разрешения синхроимпульса, поступающего на его вход разрешения записи с. шины 11 синхронизации устройства. После этого одновременно с суммированием частичного произведения в накапливающем сумматоре 3 в комбинационном 10 формируется результат с с с-с-с. 0111 + + 0001 1000.

Во втором такте работы устройства с приходом второго синхроимпульса на шину 11 синхронизации устройства на выходе четвертого элемента И 9 блока 8 элементов И фot flиpyeтcя уп равляющий сигнгш {с 1 и у - 1), который производит передачи соответствующим образом сдвинутого множимого с выходов элементов И 5 четвертой строки матрицы 4 элементов И 5 через блок 6 элементов ИЛИ 7 в накапливающий сумматор 3 и осуществляет уста новку четвертого разряда регистра 2 множителя в ноль. После этого, одновременно с суммированием в накапливающем .сумматоре 3 очередного частичного произведения, комбинационном сумматоре 10 формируется результат с 40503, 1111 + 0001 0000 и возникает перенос 1 Поскольку

1, то на выходе 13 индикации

&ЫХ

устройства присутствует сигнгш, что означает окончание операции умаожения чисел.

Отсутствие, по сравнению с прототипом, п-разрягдаого буферного регистра и второго блока элементов И значительно упрощает устройство, не снижая его быстродействия.

Формула изобретения

Устройство для умножения п-разрядных чисел, содержащее п-разрядный регистр множимого, п-разрядный регистр множителя, (2п-1)-разрядный накапливающий сумматор, матрицу из п элементов И, (2п-3)-разрядный блок элементов ИЛИ, п-разрядный блок

элементов и и п-разрядный комбинационный сумматор, причем выходы регистра множимого соответственно соединены с первой группой входов .матрицы элементов И, выходы (2, ...,

2п-2)-го разрядов которой соединены с соответствующими входами элементов ИЛИ блока элементов ИЛИ, выходов элементов ИЛИ которого соответственно соединены с (2, ..., 2п-2)-ми входными разрядами накапливающего сумматора, первый и (2п-1)-й разрядные входы накаплив.акнцего сумматора соответственно соединены с первым и выходами матрицы элементов И, вторая

группа входов которой соответственно соединена с выходами элементов И блока элементов И, первые входы элементов И блока элементов И соответственно соединены с прямыми выходами регистра множителя, вторые входы элементов И блока элементов И соответственно соединены с выходами комбинационного сумматора, а третьи входы объединены и соединены с управляющим входом .накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного су о4атора являются соответственно управляющим входом устройства и выходом индикацииокончания операции

умножения, отличающееся тем, что, с целью упрощения устройства, выходы элементов И блока элементов И соответственно соединены с входами установки в нуль п разрядов регистра множителя, инверсные выходы которого соответственно соединены с входами комбинационного сумматора, а вход разрзпения записи регистра множителя соединен с шиной .

синхронизации устройства.

Источники информации, принятые во внимание при экспертизе

кл. G Об F 7/52, 1981 (прототип).

Авторы

Даты

1983-01-30—Публикация

1981-07-28—Подача