Изобретение относится к области вынисутительной техники и может быть использовано при ра зработке быстродействукяаих устройств умножения .. .асинхронного типа.

Известно устройство для умножения п-разрядных чисел, содержащее регистры ожимого и множителя, мат-рицу элементов и,, накапливающий сумматор, блоки элементов И и ИЛИ Ij.

Недостатком данного устройства является невозможность умножения чисел, записанных в двоично-десятичном коде, и относительно низкое быстродействие.

Известно также устройство для умножения п-разрядных чисел, содержащее регистры множимого и множителя, иакаплива щий сумматор и блок управления 2 .

Недостатком данного устройства : является его низкое быстродействие.

Наиболее близким к .пpeдлaгaeмo 4y является устройство для умножения п- раэр5Шных чисел, содержащее п-разрядный регистр множимого, п-разрядный регистр множителя, накапливающий сумматор, матрицу элементов И, группу элементов ИЛИ, группу элементов , И и комбинационный сумма тор j причеля

выходы регистра множимого соответственно соединены с первь 4и входги ш элементов И матрицы, вторые входы элементов И матрищл соответственно , соединены с выходаи/а: элементов И группы и с входсши установки в ноль соответствующих разрядов регис;тра множителя, выхода элементов ИЛИ группы соответственно соединены с разряд-,

10 ньали входами накапливающего суммато ра, первые входы элементов И группы соединены с прямыми выходами соответствукяцих разрядов регистра мнсикип теля,, вторые входы элементов И груп15jnj соответственно соединены с выхорами комбинационного сумматора, а третьи входы объединены и соединены с входом синхронизации накапливающего сумматора, а входом разрешения

20 записи регистра множителя и с входом синхронизации устройства, инверсные выходы регистра множителя соответственно соединены с входами ком бинационного сумматора, вход перено25са которого является управляющим вхо. дом устройства (TsJ.

Недостатком известного устройства является отсутствие возможности ytaioжения чисел, записанных в двоично3( десятичном коде.

Цель изобретения - расширение фун кционсшьных возможностей за счет выполнения операции умножения чисел в двоично-десятичном коде.

Поставленная цель достигается тем что fe устройство для умножения п-раэрядных чисел, содержащее п-разрядный регистр множимого, п-разрядный регистр множителя, накапливающий сумматор, матрицу элементов И, групhy. элементов ИЛИ, группу элементовИ и комбинационный сумматор, причем выходы регистра множимого соответственно соединены с первыми входами элементов И матрицы, вторые входы элементов И матрицы соответственно соединены с выходами элементов И группы и с входами установки в ноль соответствующих разрядов регистра множителя, выходы элементов ИЛИ rpynпы соответственно соединены с разряднуми входами накапливающего сумматора, первые входы элементов И группы соединены с прямыми вых.одами соответствующих разрядов регистра множителя, вторые входы элементов И группы соответственно соединены с выходами комбинационного сумматора, а третьи входы объединены и соединены с входом синхронизации накапливающего сумматора, свходом разрешения записи регистра множителя и с входом синхронизации устройства, инверсные выходы регистра множителя соотротственно- соединены с входами комбинационного сумматора, вход переноса которого является управляющим входом устройства, введен элемент И, причем выход переноса комбинационного сумматора соединен с первымвходом элемента И, второй вход которого соединен с входом синхронизации устройства, а выход соединен с входами сдвига регистра множителя и накапливакнцего сумматора и с выходом индикации окончания .операции умножения устройства, зыходы четырех младших элементовй первой строки матрицы и четЕЛрех старших элементов И последней строки матрицы соединены с соответствующими разрядными входами накапливающего сумматора, а выходы остальных элементов И Матрицы соединены с соответствующими входами элементов ИЛИ группы, первый и второй управляющие входы накапливающего сумматора соединены со входами режимов работы и запрета суммирования устройства соответственно.

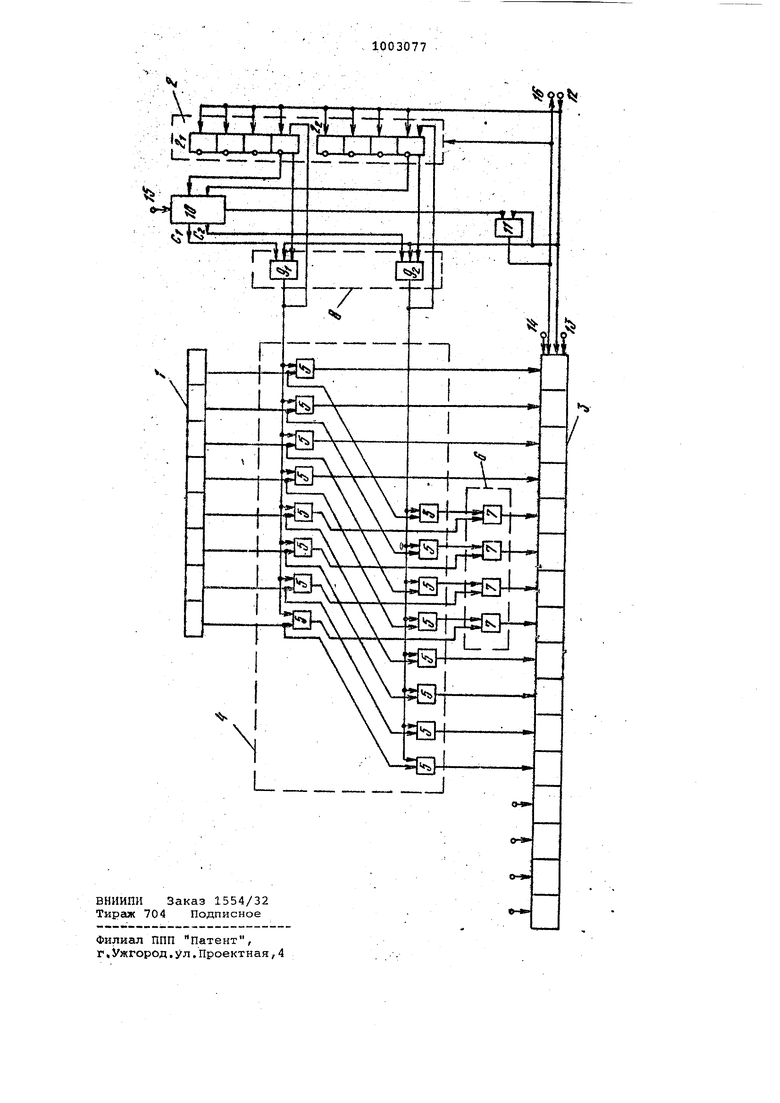

На чертеже изображена структурная схема устройства умножения п-разряднйх чисел для Ь 8.

Устройство содержит регистр 1 множимого, регистр 2 множителя, содержащий тетрады 2 , 2., накапливающий сумматор 3, матрицу 4 элементов И 5, группу 6 элементов ИЛИ 7, группу 8 элементов И 9, комбинационный сумматор 1-0, элемент И 11, вход 12 синхронизации устройства, вход 13 режима работы устройства, вход 14 запрета суммирования-накапливающего сумматора 3, управляющий вход 15 устройства и выход 16 индикации окончания опэрации умножения устройства, причем выходы регистра 1 множимого соответственно соединены с первыми Входами элементов И 5 матрицы 4, втдрые входа элементов И 5 матри1щ 4 соответственно соединены с выходами элементов И 9 группы 8 и с входами установки в ноль соответствующих разрядов регистра 2 множители, выходы четырех младших элементов И 5 первой строки матрицы 4 и четырех старших элементов И 5 последней строки матрицы 4 соединены с соответст вующими разрядными входами накапливающего сумматора 3, а выходы осталь ных элементов и 5 матрицы 4 соединены с соответствующими входами элементов ИЛИ 7 группы б, выходы которых соответственно соединены с остальными входами накапливающего сумматора 3 первые входы элементов И 9 группы 8 соединены с прямыми выходами соответствующих разрядов регистра 2 множителя, вторые входы элементов И 9 группы 8 соответственно соединены с выходами комбинационного сумматора 10, а третьи входы объединены и соединены с входом синхронизации накапливающего сумматора 3 , с входом разрешения записи регистра 2 множителя и с входом 12 синхронизации устройства, инверсные выходы регистра 2 множителя соответственно соединены с входами комбинационного сумматора 10, вход переноса которого является управляющим входом 15 устройства, а выход переноса соединен с первым входом элемента И 11, второй вход элемента И 11 соединен с входом 12 синхронизации устройства, а выход соединен с входами сдвига регистра-2 множителя и накапливающего сумматора 3 и с. выходом 16 индикации.

Рассмотрим работу устройства на примере умножения двух десятичных чисел. Пусть множимое X 69 ОНО 1001 ХдХ7ХбХ5-Х4ХзХаХ,, и множитель Y 91 1001 0001 YgY, Yg , тогда произведение 2 X-Y « 6279. В исходном состоянии в регистре 1 хранится двоично-десятичный код множимого X, в регистре 2 - двоично-десятичный код множителя Y, накапливающий сумматор 3 обнулен- и на выходги комбинационного сумматора 10 сформирован результат С « . 010, В предлагаемом устройстве используется десятично-двоичный способ умно жения двоично-десятичных чисел, при котором множитель обрабатывается ка следуютее десятично-двоичное число Y (10)-2 5 + (00)- (00) (11)-:2«. Умножение на. каждую десятичную груп разрядов множителя сводится к десятичным сдвигам мнржимого, которые реализуются в устройство на матрице 4 элементов И 5, и к десятичному суммированию в накапливающем сумматоре 3,. В предлагаемом устройстве у можение начинается с десятичной гру пы разрядов мно ; ителя, имеющей . наибольший вес 2. Как только закончи ся умножение на старшую десятичную группу разрядов множителя осуиествляется удвоение содержимого накапливающего сумматора 3, а также сдви на одиндвоичный разряд в направлении старших разрядов в регистре 2 множителя. Последним подготавливает ся к обработке следующая десятичная группа разрядов множителя с двоичным весом,2. Умножение заканчивает ся после обработки десятичной группы разрядов множителя с двоичным весом 2° . После умножения на каждую десятичную группу разрядов множителя, кроме самой младшей, осуществля ется удвоение содержимого накаплива ющего сумматора 3 и сдвиг информации на один двоичный разряд в напра лении старших разрядов в регистре 2 множителя. Разрешение или запрещение удвоения содержимого накапливающего сумматора 3 производится путе подачи соответствующего управляющег потенциала на вход 14 запрета сумми рования. Работа устройства начинается с момента прихода первого синхроимпул са на вход 12 синхронизации устройства. По .этому синхроимпульсу формируется управляющий сигнал на выход элемента И 9 группы 8 элементов И (так как только C2. который производит передачу соответствукяцим образом сдвинутого множимого с выходов элементов И 5 второй строки матрицы 4 через группу б элементов ИЛИ 7 в накапливающий сумматор 3, а также осуществляет установку восьмого разряда регистра 2 множителя в нуль с разрешения синхроимпульса поступающего на его синхровход с входа 12 синхронизации устройства. После окончания действия синхроимпульса на входе 12 синхронизации устройства одновременно с суммированием частичного произведения в накапливающем сумматоре 3 в комбинационном сумматоре 10 формируется результат С 100. На этом первый такт работы устройства заканчивается , а в накапливающем сумматоре 3 формируется результат Z 0690. Во втором такте работы устройства с приходом второго синхроимпульса на вход 12 синхронизации устройства не производится передача множимого в накапливающий сумматор 3 (так как и С , и С. равны нулю) , а осуществляется удвоение содержимого накап ливающего сумматора 3 и сдвиг информации на один двоичный разряд в регистре 2 множителя в сторону его старших разрядов под действием управляющего сигнала, сформированного на выходе элемента И 11 (так как Cgjj,), Сдвиг информации в регистре 2 осуществляется с разрешения синхроимпульса, поступающего на вход сдвига с входа 12 синхронизации устройства, удвоение содержимого накапливающего сумматора 3 осуществляется при наличии не только -синхроимпульса, но и. разрешающего потенциала, поступающе- го с входа 14 запрета суммирования. Управляющий сигнал, сформированный на выходе элемента И 11, поступает также на выход 16 индикации устройства, сообщая о том, что закончейо умножение на самую старшую десятичную группу разрядов множителя. После окончания действия второго синхроимпульса на входе 12 синхронизации устройства в комбинационном сумматоре 10 и в накапливаннцем сумматоре 3 будут сформированы следующие результаты t С 100 и Z 1380 соответственно.Третий и четвертый такты работы устройства полностью аналогичны второму такту. В каждом из этих тактов осуществляется удвоение содержимого накапливающего сумматора 3 и сдвиг информации в регистре 2 множителя на один двоичный разряд и направлении его старших-разрядов, а также на выход 16 индикации устройства поступают два сигнала, сообщающие о том, что произведено умножение еще на две десятичные групгм разрядов множителя. В результате выпол- .; нения этих двух тактов в комбинационном сумматоре и в накапливающем сумматоре 3 формируются следующие результаты. 001 и Z 5520. Здесь следует отметить, что после появления на выходе 16 индикации устройства третьего импульса, сообщающего о том, что завершилось умножение на третью.группу разрядов.множителя с двоичным весом 2 , на накапливающий сумматор 3 через вход 14 запрета суммирования должен поступить управляющий потенциал, запрещающий, в далд нейыем удвоение содержимого накапливающего сумматора 3 (этот управляющий потенциал может быть легко сформирован с помощью счетчика, определяющего момент окончания операции умнозкения двух чисел), В пятом такте работы устройства с приходом пяТого синхроимпульса на вход 12 синхронизации устройства формируется управляришй сигнал на . выходе элемента И группы 8 элеменscoB И 9 (так как только 1), который производит передачу множимого в накапливающий сумматор 3 с выходов элементов И 5 первой строки . матрицы 4 через группу б элементов ИЛИ 7 а также осуиествляет установку четвертого разряда регистра 2 множителя в нуль с разрешения синхро импульса, поступающего на е.го .синхро вход с входа 12 синхронизации устройства. После окончания действия синхроимпульса на входе 12 синхрони0сщи и устройства одновременно с сум-а мированием в накапливающем сумматоре 3 очередного частичного произве дения в комбинационном сумматоре 10 формируется результат С Сд . 010, На этом пятый такт работы устройства заканчивается, в накаплиг вающем сумматоре 3 формируется результат Z 5589.. При подаче на вход 12 синхронизации устройства шестого синхроимпульса формируется управляющий сигнал на выходе элемента И 9 группы В элемен тов И 9 (так как только Сд; Y « 1), который производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 5 второй строки матрицы 4 через группу б элементов ИЛИ 7 в накапливающий сумматор 3, а также осуществляет установку восьмого разряда регистра 2множителя в нуль с разрешения синхроимпульса, поступаюнего на синхровход с входа 12 синхронизации устройства, После окончания действия синхроимпульса на входе 12 синхронизации устройства одновременно с. суммированием очередного частичного произведения в накапливающем сумматоре 3 в комбинационном сумматоре 10 формируется результат С &ьгу. 1. ЮО На этом шестой такт работы устройств заканчивается, в накапливающем сум-/ маторе 3 формируется результат 2 6279. В седьмом такте работы устройства с приходом седьмого синхроимпульса на вход 12 синхронизации устройства на выходе элемента И 11 формируется сигнал, который поступает на выход 16 индикации устройства, сообщая о том, что завершено умножение на са-мую младшую десятичную группу разрядов множителя с весом 2 , тем самым указывая на окончание операции умножения двух чисел. Формирование в последнем такте сигнала на выходе.элемента И 11 не приводит к удвоению содержимого накапливающего сумматора 3, так как на его управляющем входе действует потенциал, запрещающий удвоение информации. Итак, появление на выходе 16 индикации устройства четырех импульсов указывает на завершение операции умножения. Сформированный .в сумматоре 3 результат 7 6279 и являетсй окончательным произведением. Умножение чисел в двоичном коде в предлагаемом устройстве осуществляется аналогично вышеописанному процессу умножения чисел в двоичнодесятичном коде. Отличия состоят только в том, что в накапливающем сумматоре производится двоичное сумладрование (вместо десятичного в предыдущем с-пучае), а удвоение содержимого сумматора фактически является обычным сдвигом его информации на Ьдин двоичный разряд в направлении старших разрядов. Такимобразом, умножение чисел в двоичном коде производится фактически на той же аппаратуре, на кото-рой выполняется умножение чисел в двоично-десятичном коде. Формула изобретения Устройство для умножения п-раэрядннх чисел, содержащее п-разрядный регистр множимого, п-раэряд 1Ый регистр множителя, накапливающий сумматор/ матрицу элементов И, группу элементов ИЛИ, группу элементов И и комбинационный сумматор, причём выходы регистра множимого соответственно соединены с первыми входами элементов И матрицы, вторые входы элементов и матрицы соответственно соединены с выходами элементов И группы и с входами установки в воль соответствующих разрядов регистра множителя, выходы элементов ИЛИ соответственно соединены с разрядными входами накапливающего сумматора, первые входа элементов И группы соединены с пряквлми выходами соответствующих разрядов регистра множителя, вторые входи элементов И группы соответственно соединены с выходами комбинационного сумматора, а третьи входы объединены и соединены с входом синхронизации накапливаввдегр сумматора, с входом разрегаекия 3аписи регистра множителя и с входом синхронизации устройства инверсНые выходы регистра множителя соответственно соединены с входами комбияационного сумматора, вход переноса которого является управляющим входом устройства, о т л и- ч а ю щ ее с я тем, что, с целью расширения его функциональных возможностей.за счет выполнения операции умножения чисел в двоично-десятичном коде, в него введен элемент И, причем вы-.

ход переноса комбинационного сумматора соединен с первым входом элемента И, второй вход которого соединен входом синхрониэёщии устройства а выход соединен с входами сдвига регистра множителя и накалливающего сумматора и с. выходом HH;|QIкации окончания операции умножения устройства, выходы четырех младфшх элементов И первой строки матрицы и четырех старших..элементов И последнейстроки матрицы соединены с соответствующими разрядными входами накапливающего сумматора, а выходы остальных элементов И матрицы соединены с соответствующими входами элементов ИЛИ группы, первый и второй управляющий входы накапливающего сумматора соединены: « входами режимов работы и запрета суКошрования устройства соответственно.

Источники информации, принятые во внимание 1фи экспертизе ,

1.Авторское свидетельство СССР 482740, кл. G Об F 7/52, 1973.

2.Карцев М. А. Арифметика цифро- вых машин. М., Наука, 1969, с. 364.

3.Авторское свидетельство СССР по заявке 3343801/18-24,

кл. G 06 F 7/52f 07.09.81 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU993255A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения п-разрядных чисел | 1981 |

|

SU985783A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

Авторы

Даты

1983-03-07—Публикация

1981-09-07—Подача