тов и второй группы, вторые входы элементов И первой и второй групп соединены соответственно с прямьм выходом первого элемента ИЛИ второй группы и выходами первого и второго элементов И блока выделения младшего значащего разряда и с входами установки в ноль И/2 пар разрядов h-разрядного регистра множителя, выходы элементов И первой группы соединены с входами первого элемента

ИЛИ,выходы элементов И второй группы соединены с входами второго элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом элемента ИЛИНЕ и с первыми управляющими входами коммутаторов, выход второго элемента ИЛИ соединен с вторым входом элемента Ш1И-НЕ и с вторыми управляющими входами коммутаторов, выход элемента ИЛИ-НЕ соединен с третьими управляющими входами коммутаторов,

прямые выходы второго и третьего элементов ШШ второй группы соединены соответственно с первыми входами первого и второго элементов И блока выделения младшего значащего разряда, вторые входы первого и второго элементов И и первый вход третьего элемента И блока вьщеления младшего значащего ; разряда соединены с инверсным выходом первого элемента ИЛИ второй группы, инверсный- выход второго злемента ИЛИ второй группы соединен с третьим входом второго элемента И и вторым входом третьего элемента И блока вьщеления младшего значащего: разряда, третий вход третьехо -элемента И которого соединен с инверсным выходом третьего элемента ИЛИ второй группы, выход i третьего элемента И блока выделения I младшего значащего разряда соединен с выходом окончания умножения устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

| Устройство для умножения двух @ -разрядных чисел | 1987 |

|

SU1439581A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения @ -разрядных чисел | 1986 |

|

SU1374217A1 |

| Устройство для умножения @ -разрядных чисел | 1981 |

|

SU1022155A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

УСТРОЙСТВО ДЛЯ УГ ОЖЕНИЯ . п-РАЗРЯДНЫХ ЧИСЕЛ, содержащее п -разрядный регистр множимого и п-разрядный регистр множителя, (и-2)-разрядный регистр утроенного множимого, 2л -разрядный накапливающий сумматор, первую группу из 2п -4 элементов ИЛИ, вторую группу из П/2 элементов ИЛИ, первую группу из п/2 эле ментов И, группу п/2 дешифраторов и Ih+2 коммутаторов, причем первые, вторые и третьи информационные входы коммутаторов соединены соответственно с разрядными выходами г -раз- . рядного регистра множимого и п+2 разрядного регистра утроенного множимого;, выходы

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействую щих устройств.умножения асинхронного типа.

Известно устройство для умножения Л-разрядных чисел, содержащее п-разрядные регистры множимого и множителя, 2п -разрядный накапливающий сумматор, матрицу из п элементов И, (2ц -3)-разрядный блок элементов ШШ и два h -разрядных 6jioKa элементов И, Умножение двух чисел в этом устройстве выполняется в среднем за

.и/2 тактов L11. I J

Недостатком данного устройства является низкое быстродействие как из-за большого числа его тактов работы, так и из-за большой длительности такта,.поскольку длительность такта работы определяется временем переходного процесса в блоке элементов И, -образующих последовательную цепь.

Известно также устройство для умножения п -разрядных чисел, содержащее г -разрядные регистры множимого и множителя, 2п -разрядный накапливающий и п-разрядный комбинационный сумматоры, матрицу из (.элементов И, ( - разрядный блок элементов ИЛИ и р-разрядный блок элеМентов И. В этом устройстве умножение двух чисел также производится в среднем за п /2 тактов С21.

Недостатком этого устройства является его относительно низкое быстродействиё из-за большого числа тактов работы.

Наиболее близким по технической сущности к - предлагаемому является устройство для умножения h -разрядных чисел, содержащее i -разрядные регистры множимого и множителя, П +2 -разрядный регистр утроенного множимого, 2ул -разрядный накапливающий сумматор, первый 2h -41-разрядный и второй К|/2-разрядный блоки элементов ИЛИ, п/2-разрядный блок элементов И, ул/2-разрядный блок дешифраторов и СУ1+2Уразрядный блок коммутирующих узлой, причем вторые

и третьи информационные входы коммутирующих узлов блока соединены соответственно с разрядными выходами регистров множимого и утроенного

множимого, выходы элементов ИЛИ первого блока соединены соответственно с разрядными входами с третьего по(2и -21-й накапливающего сумматора выходы каждой пары разрядов регистра множителя соединены с первым и вторы входами соответствующего элемента ИЛИ второго блока и с первым и вторым входами соответствующего дешифратора блока, вход разрешения записи регистра множителя соединен с управляющим входом накапливающего сумматора и с щиной синхронизации .устройства. Умножение двух чисел вьтолняется. в среднем за. Зп/8 тактов С31.

Недостатком известного устройства являются большие аппаратурные затраты при его реализации.

Цель изобретения - сокращение аппаратурных затрат при реализации устройства.

Поставленная цель достигается тем, что в устройство для умножения |г -разрядньгх чисел, содержащее п -разрядный регистр множимого и h-разрядный регистр множителя,Си+21-разрядный регистр утроенного множимого, 2п -разрядный накапливающий сумматор первую группу из (2v -А элементов ИЛИ,вторую группу из п/2 элементов ИЛИ, первую группу из .la/2 элементов И, группу п/2 дешифраторов и (п+2 коммутаторов, причем первые, вторые и третьи информационные входы коммутаторов соединены соответственно с разрядными выходами п -разрядного регистра множимого и (п+2 -разрядного регистра утроенного множимого, выход j 2in-4 элементов ИЛИ первой группы соединены соответственно с разрядными входами с третьего по(2лл -2)-и 2VI -разрядного накапливающего сумматора, выходы каждой пары разрядов (-разрядного регистра множителя соединены с первым и вторым входами соответствующего элемента ИЛИ второй группы и с первым и вторым входами соответствующего дешифратора, вход разрешения записи f -разрядного регистра множителя соединен с тактовым входом 2v -разрядного накапливающего сумматора и тактовым входом устройства,введены матрица из (nV2+v) элементов И, содержащая h/2 строк и(у +2) столбцов, блок выделения -младшего значащего разряда, содержащийпервый, второй и третий элементы И, вторая группа из п/2 элементов И,

первый и второй элементы Ш1И, элемен ИЛИ-НЕ, причем выходы коммутаторов соединены соответственно с первыми входами элементов И столбцов матрицы, вторые входы элементов И первой строки матрицы соединены с прямым выходом первого элемента ИЛИ второй группы, вторые входы элементов И второй и третьей строк матрицы соединены с выходами соответственнопервого и второго элементов .И блока вьщеления младшего значащего разряда, входы к-го элемента ИЛИ первой груЬпы соединены с выходами (к+2 -2

5

элементов И (-X строк матрицы, выходы первого, второго элементов И первой строки матрицы и(п+П-го и ( К +2)-го элементов И последней строки матрицы соединены соответ0ственно с первым, вторым, ( и 2у -м разрядными входами накапливающего сумматора, первые выходы п/2 дешифраторов соединены соответственно с первыми входами элементов

5 И первой группы, вторые выходы дешифраторов соединены соответственно с первыми входами элементов И второй группы, вторые входы элементов И первой и второй групп соединены со0ответственно с прямым выходом первого элемента ИЛИ второй-группы и выходами первого и второго элементов И блока выделения младшего значащего разряда и с входами установки в ноль п/2 пар разрядов и -разрядного

5 регистра множителя, выходы элементов И первой группы соединены с входамипервого элемента ИЛИ, выходы элементов И второй группы соединены с входами второго элемента ИЛИ, выход

0 первого элемента ИЛИ соединен с первым входом элемента ИЛИ-НЕ и с первыми управляющими входами коммутаторов, выход второго элемента ИЛИ соединен с вторым входом элемента

5 ИЛИ-НЕ и с вторыми управляющими входами коммутаторов, выход элемента ИЛИ-НЕ соединен с третьими управляющими входами коммутаторов, прямые выходы второго и третьего элементов

0 ИЛИ второй группы соединены соответственно с первыми входами первого и второго элементов И блока выделения младшего значащего разряда, вторые входы первого и второго эле5ментов И и вход третьего элемента И блока выделения младшего значащего разряда соединены с инверсным выходом первого элемента

ИЛИ второй группы, инверсный выход второго элемента ИЛИ второй группы соединен с третьим входом второго элемента И и вторым входом третьего элемента И блока выделения младшего значащего разряда, третий вход третьего элемента И которого соединен с инверсным выходом третьего элемента ИЛИ второй группы, выход третьего элемента И блока выделения младшего значащего разряда соединен с выходом окончания умножения устройства .

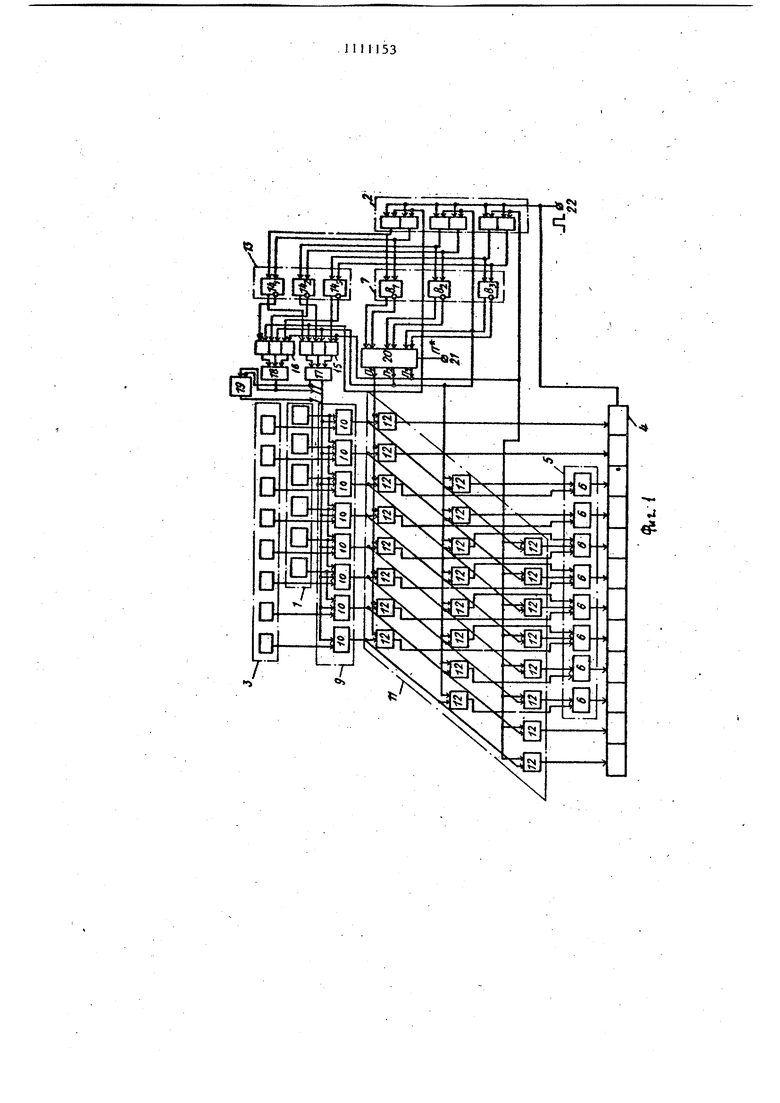

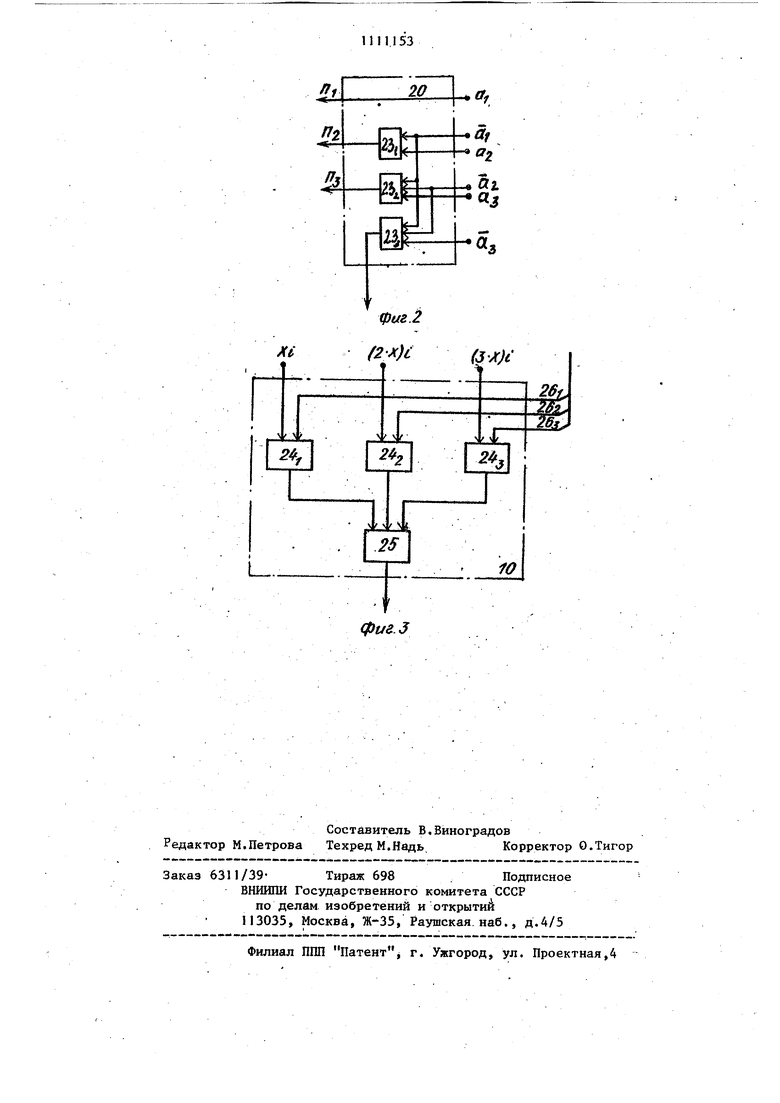

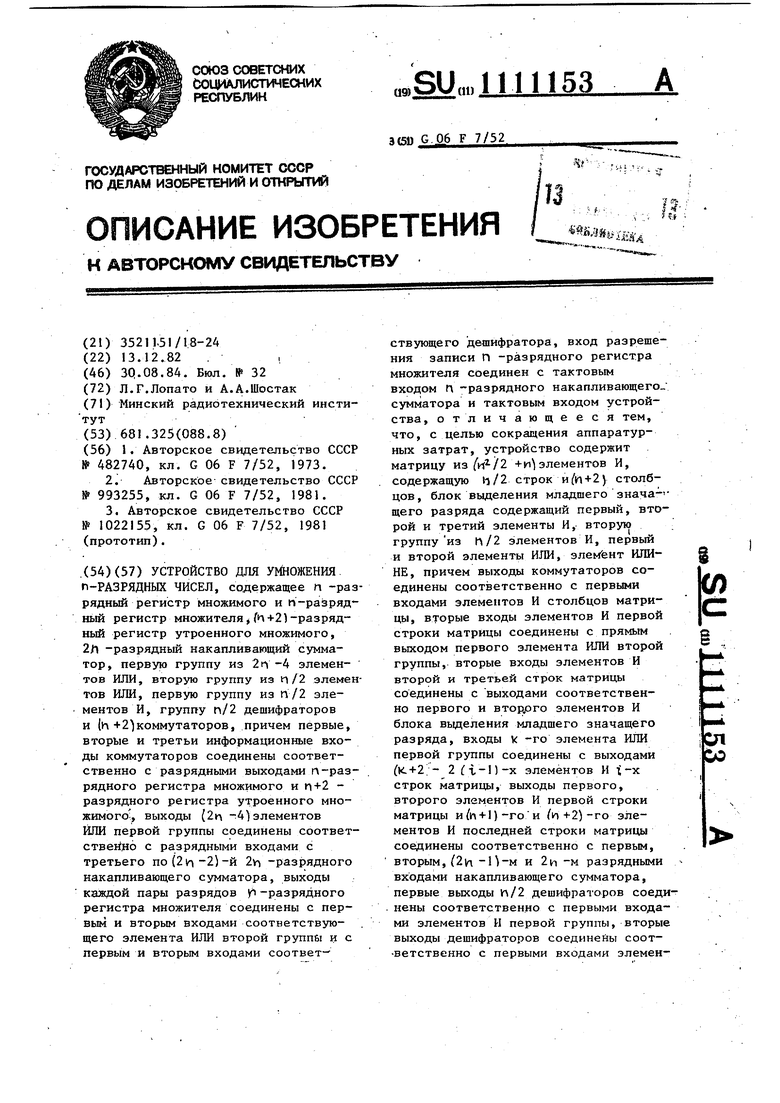

На фиг. 1 приведена структурная схема устройства для умножения Л - разрядных чисел для случая на фиг. 2 - функциональная схема . блока выделения младшего значащего разряда; на фиг. 3 - функциональная схема коммутатора.

Устройство содержит 6-разрядный регистр множимого, 6-разрядный регистр 2 множителя, 8-разрядный регистр 3 утроенного множимого, 12-разрядный накапливающий сумматор 4, первую группу 5 из восьми элементов ИЛИ 6, вторую группу 7 из трех элементов ИЛИ 8,,-8j , группу 9 из восьми коммутаторов 10, матрицу 11 из 24 элементов И 12, группу 13 из трех дешифраторов 14, первую 3-разрядную группу 15 элементов И, вторую 3-разрядную группу I6 элементов И, первый элемент ИЛИ 17, второй элемент ИЛИ 18, элементИЛИ-НЕ 19, блок 20 вьделения младшего значащего разряда, выход 21 индикации окончания операции умножения и шину 22 синхронизации, причем первые информационные входы первых щести коммутаторов IО группы 9 соединены с соответствующими разрядными выходами регистра 1 множимого, вторые информационные входы коммутаторов 10 с второго по седьмой соединены соот- , вбтственно с разрядными выходами регистра 1 множимого, третьи информационные входы коммутаторов 10 с первого по восьмой группы 9 соединены соответственно с разрядными выходами регистра 3 утроенного множимого, управляющие входы коммутаторов 10 группы 9 соединены с ее шиной управления, выходы коммутаторов 10 . соединены соответственно с первой группой входов матрицы 11 элементов И 12, выходыf3-101-го разрядов которой соединены соответственно с входами элементов ИЛИ 6 группы 5, выходы 1,2,11 и 12-го разрядов матрицы I1 элементов И 12 соединены соответственно с 1,2,11 и 12-м разряд5 ными входами накапливающего сумматора, 4, выходы каждой из трех пар разрядов регистра 2 множителя соединены с первым и вторым входами соответствующего элемента ИЛИ 8/1-8 J О группы 7 и с первым и вторым входами соответствующего дешифратора . первые выходы дешифраторов 14j соединены соответственно с первыми входами элементов И 15, вторые 5 выходы дешифраторов 14дсоедине-, ны соответственно с первыми входами элементов И 16, выходы элементов И 15 соединены с входами первого элемента ИЛИ 17, выходы элементов И 0 16 соединены с входами второго элемента ИЛИ 18, выход первого элемента ИЛИ 17 соединен с первым входом эле-, мента ИЛИ-НЕ I9 и с первым входом шины управления группы 9 коммутаторов 10, выход второго элемента ИЛИ. 18 соединен с вторым входом элемента ИЛИ-НЕ 19 и с вторым входом щины управления группы 9 коммутаторов 10, выход элемента ИЛИ-НЕ 19 соединен с третьим входом шины управления группы 9 коммутаторов 10, прямые выходы элементов ИЛИ соединены соответственно с первой группой входов блока 20 выделения младшего значащего разряда, вторая группа входов которого соединена соответственно с инг версными выходами элементов ИЛИ 8/8, выходы блока 20 выделения младшего значащего разряда соединены соответственно с второй группой

входов матрицы 11 элементов И 12, с входами установки в ноль трех пар разрядов регистра 2 множителя и с вторыми входами элементов И 15 и 16, выход П блока 20 вьщеления младшего значащего разряда является выходом 21 индикации окончания операции умножения, вход разрешения записи регистра 2 множителя соединен с управляю.щим входом накапливающего сумматора 4 и с шиной 22 синхронизации устройства.

Блок 20 выделения младщего значащего . разряда предназначен для последовательного выделения единиц из 3-разрядного двоичного кода А а,, а , а , начиная с его м.падщих разрядов, и сформированного

1на прямых выходах элементов ИЛИ бд-бд здесь и далее возрастание индексов при буквенных обозначениях принято в направлении старших разрядов) . Блок 20 содержит(фиг. 2)три элемента И 23,( - 23 и функционирует, в соответствии со следующими логическими выражениями:

П;| я, ,-5iz,n,ciia2Q%,

где П Oj Oj - признаки вьщеления соответственно первого, второго и третьего значащих : разрядов двоичного кода .А, п - признак окончания выделения значащих разрядов кода А . Этот вариант построения блока 20 выделения младшего значащего разряда обладает исключительно.высоким быстродействием, особенно при малых значениях разрядности обрабатываемой информации . При больших же значениях V ограниченных возможностей логических элементов целесообразно в блоке 20 использовать принцип разбиения его на группы с последовательной либо параллельной передачей между группами признаков (Т окончания выделения значащих разрядов в группах. Это позволяет при существующей элементной базе обеспечить в большинстве практических случаев время выделения значащего разряда, не превышающее величину (2-3/ТГ) , где t - задержка сигнала на одном логическом элементе.

Коммутатор I -го разряда группы 9 содержит(фиг. 31 три элемента И элемент ИЛИ 25, причем первые входы элементов И 24,- 24g являются соответственно первым, вторым и третьим информационными входами i-ro коммутатора на первый информационный вход подается значение г -го разряда регистра 1 множимого X, на второй информационный вход - значение (г-П-го разряда, регистра 1 множимого X, т.е. i -ый разряд удвоенного множимого третий информационный вход поступает значение г-го разряда регистра 3 утроенного множимого З-у), вторые управляющие входы элементов И . 24ц- 24 соединены соответственно с первым 26 , вторым 2(2 и третьим 26выходами шины управления группы 9

коммутаторов 10 (первый выход 26| щины управления является выходом первого элемента ИЛИ 17, второй выход 26j шины управления - выходом

второго элемента ИЛИ 18, а третий выход 26з шины управления - выходом элемента Ш1И-11Е I 9 .

Таким образом, если сигнал логической единицы образуется на выходе

первого элемента ИЛИ 17, то группа 9 коммутаторов 10 передает соответствующим образом на первую группу входов матрицы 1I элементов И 12 одинарное множимое .Ьх, если сигнал

логической единицы образуется на выходе второго элемента ИЛИ 18 - удвоенное множимое 2- X ,если сигнал логической единицы формируется на выходе элемента ИЛИ-НЕ 19, то группа 9

коммутаторов 10 подает соответствующим образом на первую группу входов матрицы 11 элементов И I2 утроенное множимое 3- у (сигнал логической единицы может образоваться только на

одном из выходов элементов ИЛИ I7 и 18 и элемента ИЛИ-НЕ 19, т.е. либо только на выходе первого элемента ИЛИ 17, либо только на выходе второго элемента ИЛИ 18, или же только

на выходе элемента ИЛИ-НЕ 19.

Каждый из дешифраторов 14 может быть реализован с использованием двух двухвходовых элементов И, причем сигнал логической единицы формируется на его первом выходе тогда, когда значение сосэтветствующей пары разрядов регистра 2 множителя равно единице, и на его втором выходе , когда значение соответствующей

пары разрядов регистра 2 множителя равно двум.

Устройство работает следующим образом.

В исходном состоянии в регистрах I и 2 хранятся без знаков 6-разрядные соответственно множимое х и множитель , в регистре 3 - 8-разрядное утроенное множимое 3v (оно может быть предварительно сформировано либо На сумматоре. 4, либо с использованием дополнительной комбинационной схемы), накапливающий сумматор 4 обнулен.

Детально работу устройства рас1смотрим на примере умножения шожимого

Хна множитель У 110001 .С учетом

этого в исходном состоянии на первом выходе дешифратора 14 формируется сигнал логической единицы, а на прямык выходах элементов ИЛИ 8 образуется двоичный код ..Л 101, из которого в блоке 20 осуществляется выделение младшего значащего разря.да, что приводит к образованию сигнала признака П. По этому сигналу на выходе первого элемента ИЛИ 17 формируется сигнал логической едини цы, который,.поступая по шине управления группы 9 на управляющие входы его коммутаторов 10, производит передачу на выходы одинарного множимого , которое далее поступает на первую группу входов матрицы 1I элементов И 12 и передается с разрешения того же сигнала признака П через первую линейку.элементов И 12 матрицы 11 и элементы ИЛИ 6 с определенным сдвигом на соответствующие информационныевход накапливающего сумматора 4. Собственно работа устройства начинается с момента прихода первого синхроимпульса на шину 22 синхрониз ции устройства. С разрешения этого синхроимпульса осуществляется установка в ноль первой (самой мл.адшей), пары разрядов регистра 2 множителя по сигналу признака П, и производит ся прием информации в накапливающий сумматор 4 с его информационных входов. По окончании действия перво го синхроимпульса на шине 22 устрой ства одновременно с суммированием в накапливающем сумматоре 4 первого частичного произведения в устройстве выполняются следующие действия: на всех выходах дешифраторов 14;,14 образуются сигналы логического нуля и одновременно с этим на прямых выходах элементов ИЛИ формируется двоичный код , по которому в дальнейшем на третьем выходе блока 20 выделения младшего значащего; разряда формируется сигнал признака П,; так как на всех выходах дешифраторов 14зсформи рованы сигналы логического нуля, то на выходах первого и второго эле ментов ИЛИ 17 и 18 также присутству ют сигналы логического нуля, а след вательно, на выходе элемента ШШ-НЕ 19. возникает сигнал логической ёдиницы, который, поступая по шине . управления группы 9 на управляющие входы его коммутаторов 10, производит передачу на выходы группы У утроенного множимого , которое далее поступает на первую группу входов . матрицы 1I элементов И 12; утроенное множимое по сигналу признака П передается с определенным сдвигом через третью линейку элементов И 12 матрицы 11 и элементы ИЛИ 6 на , соответствующие информационные входы накапливающего сумматора 4. На этом первый такт работы устройства заканчивается. Во втором такте с разрешения второго синхроимпульса на шине 22 синхронизации устройства осуществля-; ется установка в Ноль третьей (самой старшей пары разрядов регистра 2 множителя по сигналу признака П и производится прием информации в накапливающий сумматор 4 с его,информационных входов. По окончании действия второго синхроимпульса на шине 22 устройства одновременен с суммированием 9 накапливающем сумматоре 4 второго частичного произведения на прямых выходах элементов ИЛИ формируется двоичный кодЛ,. 000, по которому .на выходе окончания выделения блока 20 выделения младшего значащего разряда формируется сигнал признака П. Этот сигнал поступает на выход 21 устройства, сигнализируя об окончании умножения чисел. Таким образом, умножение в устройстве двух рассмотренных 6-разрядных чисел выполнено за два такта. В общем же случае умножение двух 41 -разрядных чисел в предлагаемом устройстве, так же как и в известном СЗ выполняется в среднем за тактов, причем длительность .такта . определяется либо временем сложения .{v 2 -разрядных чисел в накапливающем сумматоре 4, либо задержкой информации в блоках 5,7,9,15,20, в мат)ице 1 1 и на элементах 17 и 19. Технико-экономическое преимущество предлагаемого устройства в сравнении с прототипом состоит в значительно меньших аппаратурных затратах при его реализации. Так, например, в устройстве при его реализации требуется в 1,7 раза меньше аппаратуры. Скорость же работы предлагаемого устройства не ниже скорости работы прототипа.

фиг. J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения двух -разрядных чисел | 1973 |

|

SU482740A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1984-08-30—Публикация

1982-12-13—Подача